Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин в аналоговые.

Цель изобретения - повьпнение точности за счет улучшения линейности характеристики преббразования.

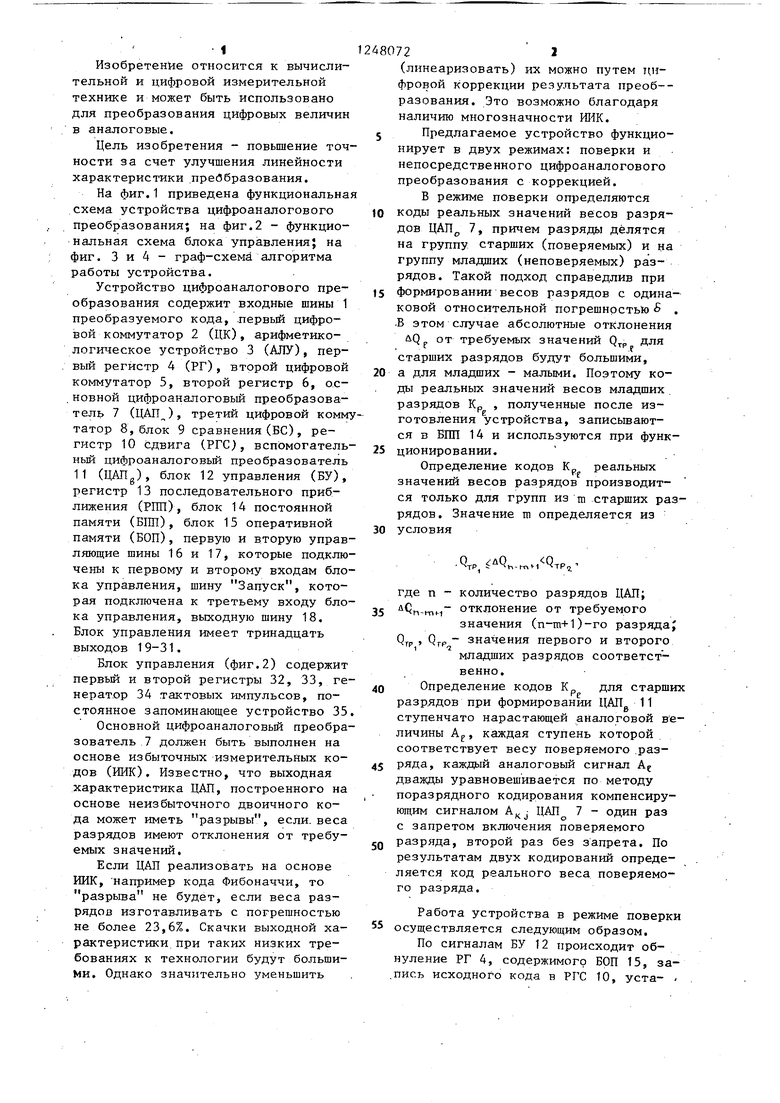

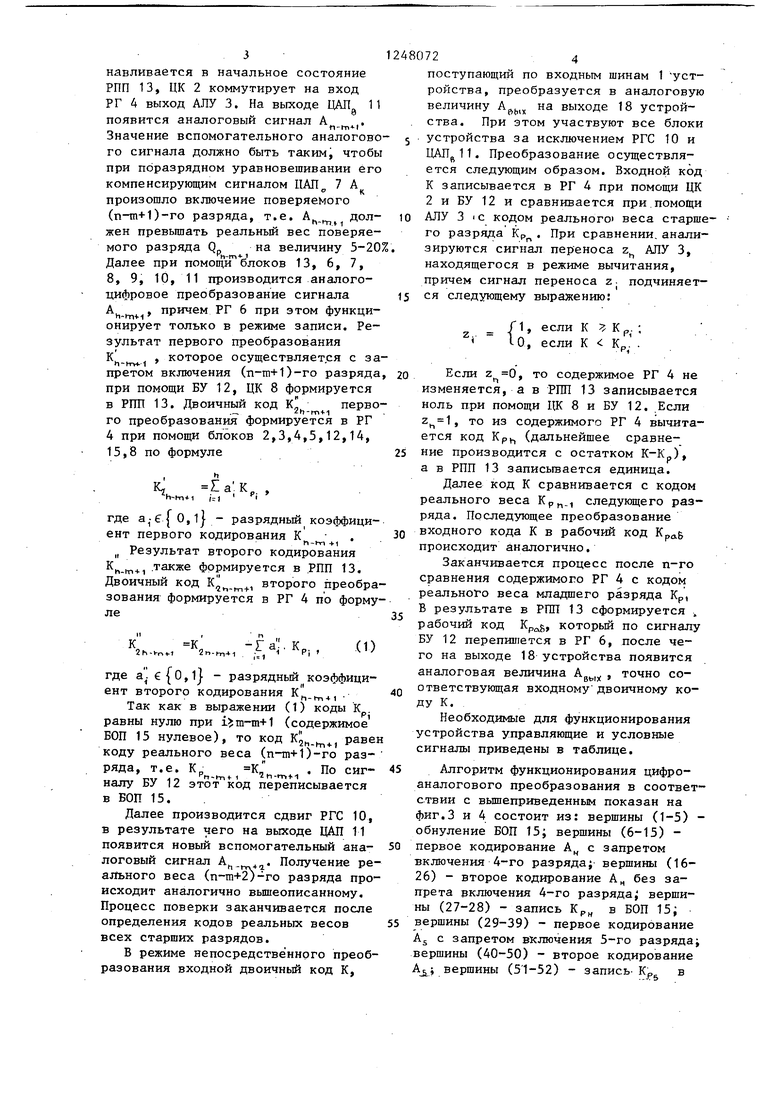

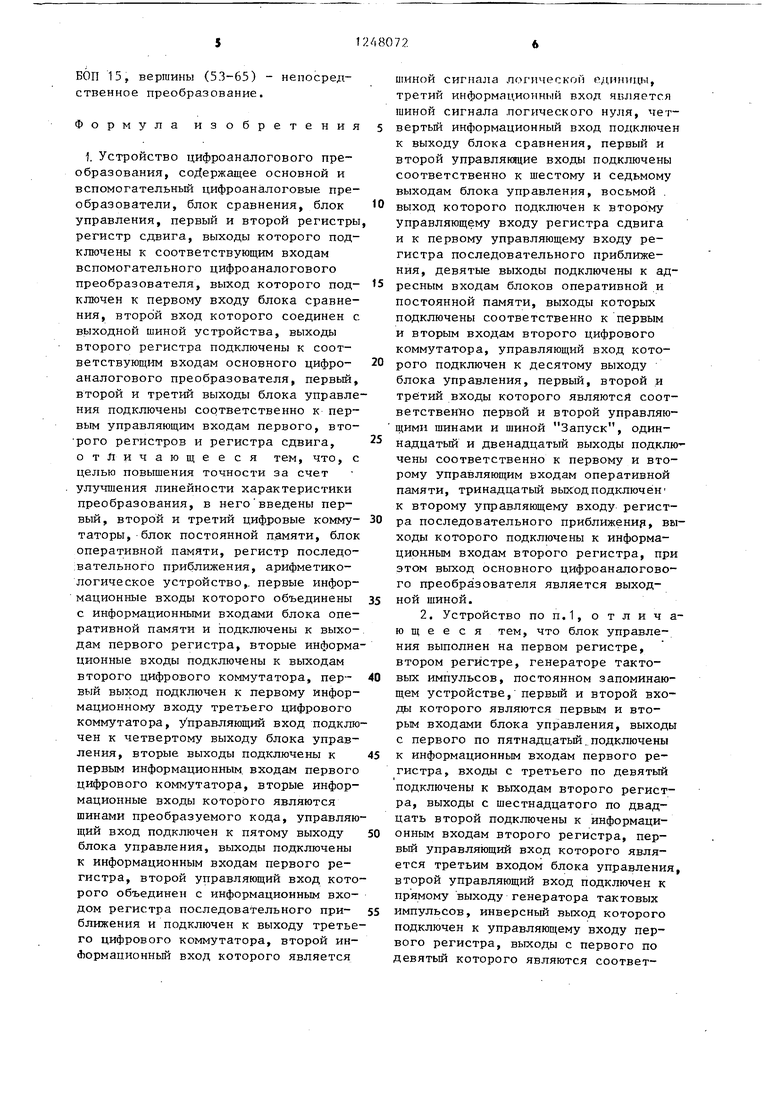

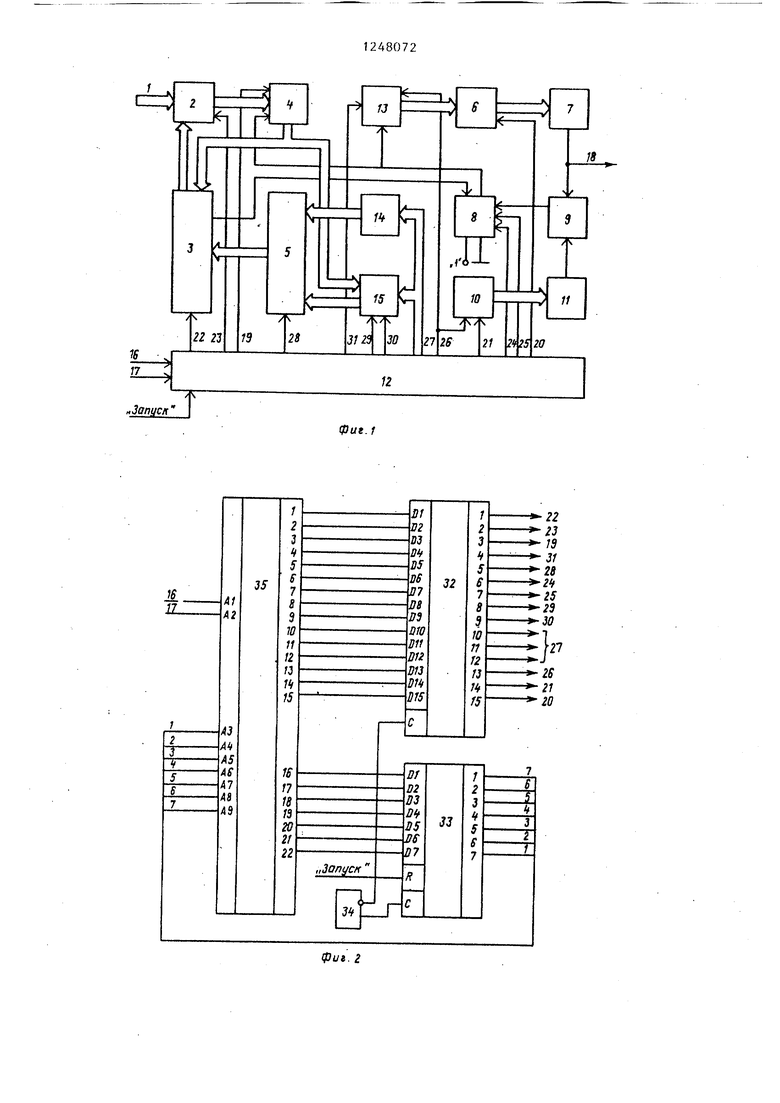

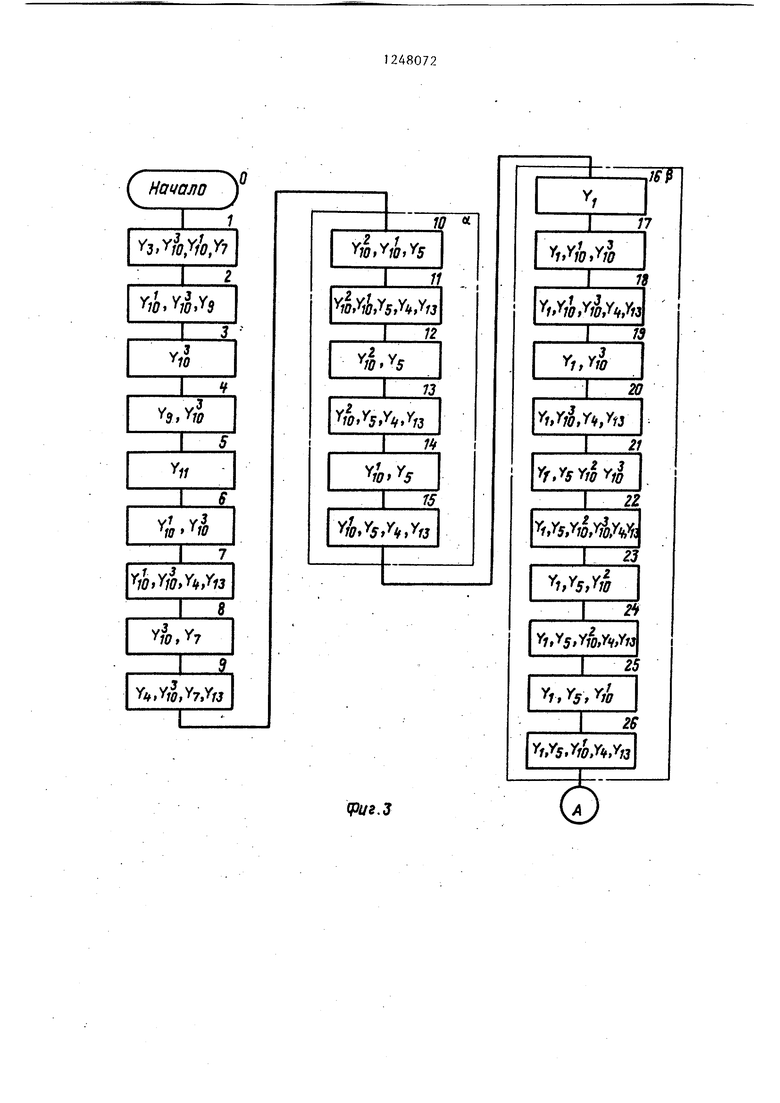

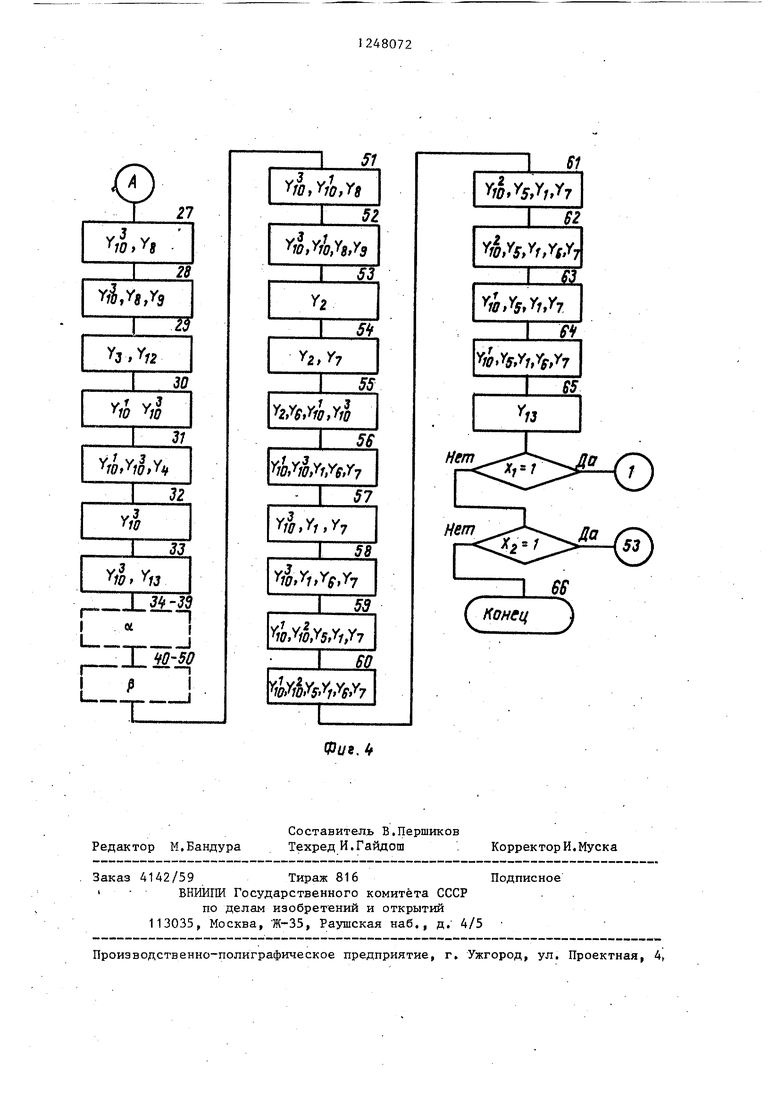

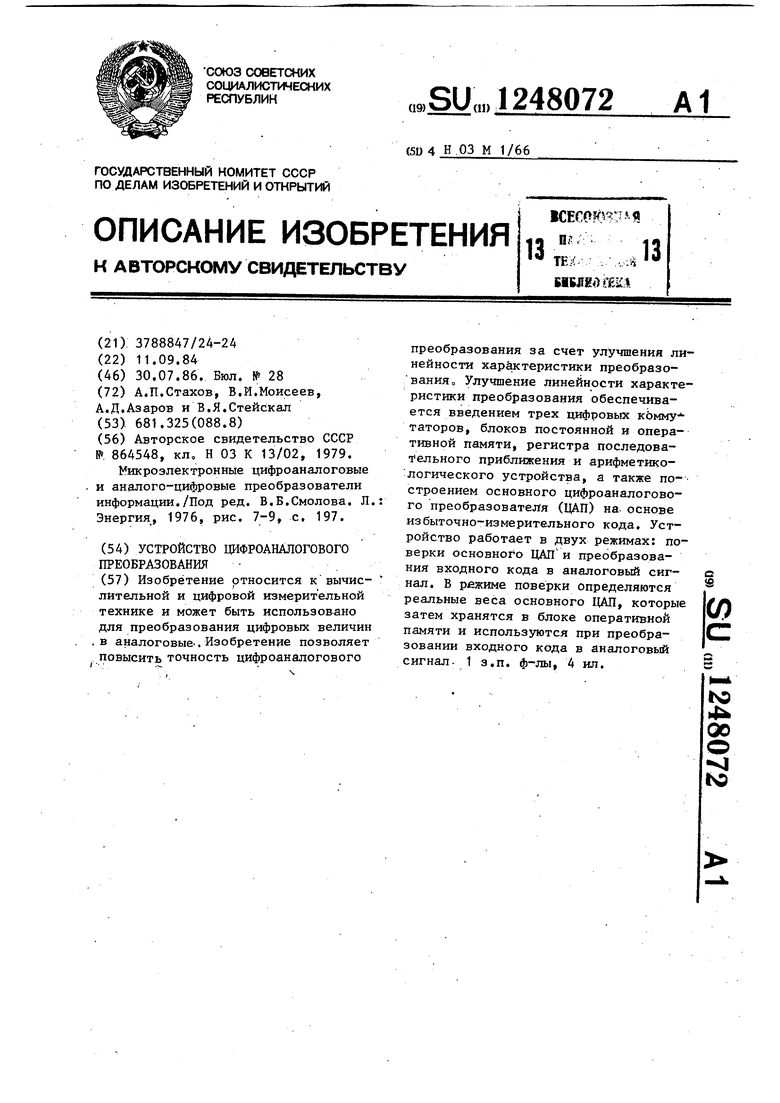

На фиг.1 приведена функциональная схема устройства цифроаналогового преобразования; на фиг.2 - функциональная схема блока управления; на фиг. 3 и 4 - граф-схема алгоритма работы устройства.

Устройство цифроаналогового преобразования содержит входные шины 1 преобразуемого кода, лервьй цифровой коммутатор 2 (ЦК), арифметико- логическое устройство 3 (АЛУ), первый регистр 4 (РГ), второй цифровой коммутатор 5, второй регистр 6, основной цифроаналоговый преобразователь 7 (ЦАП), третий цифровой коммутатор 8,блок 9 сравнения(БС), регистр 10 сдвига (РГС), вспомогательный цифроаналоговьй преобразователь 11 (UAng), блок 12 управления (БУ), регистр 13 последовательного приближения (РПП), блок 14 постоянной памяти (Б1Ш), блок 15 оперативной памяти (БОН), первую и вторую управляющие шины 16 и 17 которые подключены к первому и второму входам блока управления, шину Запуск, которая подключена к третьему входу блока управления, выходную шину 18. Блок управления имеет тринадцать выходов 19-31.

Блок управления (фиг.2) содержит первьй и второй регистры 32, 33, генератор 34 тактовых импульсов, постоянное запоминающее устройство 35

Основной цифроаналоговьй преобразователь 7 должен быть выполнен на основе избыточных измерительных кодов (ИИК). Известно, что выходная характеристика ЦАП, построенного на основе неизбыточного двоичного кода может иметь разрывы, если, веса разрядов имеют отклонения от требуемых значений.

Если ЦАП реализовать на основе ИИК, например кода Фибоначчи, то разрыва не будет, если веса разрядов изготавливать с погрешностью не более 23,6%. Скачки выходной характеристики при таких низких требованиях к технологии будут большими. Однако значительно уменьшить

(линеаризовать) их можно путем цифровой коррекции результата преоб-- разования. Это возможно благодаря наличию многозначности ЮЖ.

5 Предлагаемое устройство функционирует в двух режимах: поверки и непосредственного цифроаналогового преобразования с коррекцией.

В режиме поверки определяются

0 коды реальных значений весов разрядов ЦАПр 7, причем разряды делятся на группу старших (поверяемых) и на группу младших (неповеряемых) разрядов. Такой подход справедлив при

)5 формировании весов разрядов с одинаковой относительной погрешность) 5 . .В этом случае абсолютные отклонения

UQ от требуемых значений для старших разрядов будут большими,

20 а для младших - малыми. Поэтому коды реальных значений весов младших . разрядов Ко , полученные после изБ

готовления устройства, записываются в БПП 14 и используются при функ25 ционировании.

Определение кодов Кр реальных значений весов разрядов производится только для групп из m старших разрядов. Значение m определяется из

30 условия

.QTP,.Qb-H./QTP,

где п - количество разрядов ЦАП;

35 п-ть1 отклонение от требуемого

значения (n-m+D-ro разряда , - значения первого и второго младших разрядов соответственно.

40 Определение кодов Кр для старших разрядов при формировании ЦАП 11 ступенчато нарастающей аналоговой в е- личины Ар, каждая ступень которой соответствует весу поверяемого .раз45 ряда, каждый аналоговый сигнал Ар дважды уравновешивается по методу поразрядного кодирования компенсирующим сигналом ЦАП 7 - один раз с запретом включения поверяемого

JQ разряда, второй раз без запрета. По результатам двух кодирований определяется код реального веса поверяемого разряда.

Работа устройства в режиме поверки 55 осуществляется следующим образом.

По сигналам БУ 12 происходит обнуление РГ 4, содержимого БОП 15, за- .пись исходного кода в РГС 10, уста- 31

навливается в начальное состояние РПП 13, ЦК 2 коммутирует на вход РГ 4 выход АЛУ 3. На выходе ЦАП 11 появится аналоговый сигнал А ,,

tl IH- -1

Значение вспомогательного аналогового сигнала должно быть таким, чтобы при поразрядном уравновешивании его компенсирующим сигналом ПАП 7 А произошло включение поверяемого (п-т+1)-го разряда, т.е. А должен превьппать реальный вес поверяемого разряда QP

на величину 5-20%

Далее при помогцрГЪлоков 13, 6, 7, 8, 9, 10, 11 производится аналого- цифровое преобразование сигнала А , причем РГ 6 при этом функциh-in+-1

онирует только в режиме записи. Результат первого преобразования к , которое осуществляется с заh-h 4--1 / л

претом включения (n-m+D-ro разряда, при помощи БУ 12, ЦК 8 формируется в РПП 13. Двоичный код к перво.-t п - fTt4-1

го преобразования формируется в РГ 4 при помощи блоков 2,3,4,5,12,14, 15,8 по формуле

К Еа Кр. ,

Vin-n i-, 1

где е 0,11 - разрядный коэффициент первого кодирования К

Ь -НП -Ц

I, Результат второго кодирования h-m+i также формируется в РПП 13. Двоичный код К , второго преобразования формируется в РГ 4 по формуле

. II

.-1 2n-in+1 ;., 1

где а. €{0,l| - разрядный коэффициент второго кодирования К., .

Так как в выражении (1) коды К равны нулю при i m-m+l (содержимое БОП 15 нулевое), то код К,., раве коду реального веса (п-т+1)-го разряда, т.е. К к . По сигТТ1Г лп n-tnt 2Ц-ГТ,1

налу БУ 12 этот код переписывается в БОП 15.

Далее производится сдвиг РГС 10, в результате чего на вьпсоде ДАЛ 11 появится новый вспомогательный аналоговый сигнал А . Получение реального веса (п-т+2)-го разряда происходит аналогично вьшгеописанному. Процесс поверки заканчивается после определения кодов реальных весов всех старших разрядов.

В режиме непосредственного преобразования входной двоичный код К,

480724

поступающий по входным шинам 1 устройства, преобразуется в аналоговую величину Ар,, на выходе 18 устрой- . ства. При этом участвуют все блоки 5 устройства за исключением РГС 10 и ЦАП| 11. Преобразование осуществляется следующим образом. Входной код К записывается в РГ 4 при помощи ЦК 2 и БУ 12 и сравнивается при.помощи 10 АЛУ 3 1C кодом реального веса старшего разряда Кр. При сравнении.анали- зируются сигнал переноса z АЛУ 3, находящегося в режиме вычитания, причем сигнал переноса Z| подчиняет- 15 ся следзпощему выражению:

10,

если К К р.

если К К.,.

,

35

20 Если , то содержимое РГ 4 не изменяется, а в РПП 13 записывается ноль при помощи ЦК 8 и БУ 12..Если , то из содержимого РГ 4 вычитается код Кр, (дальнейшее сравне25 ние производится с остатком К-К-), а в РПП 13 записьшается единица.

Далее код К сравнивается с кодом реального веса Кр„., следующего разряда. Последующее преобразование

3Q входного кода К в рабочий код происходит аналогично.

Заканчивается процесс после п-го сравнения содержимого РГ 4 с кодом реального веса младшего разряда Кр, В результате в РПП 13 сформируется . рабочий код Край которьш по сигналу БУ 12 перепишется в РГ 6, после чего на выходе 18 устройства появится аналоговая величина А„, , точно соBt iX

Q ответствующая входному двоичному коду К. .

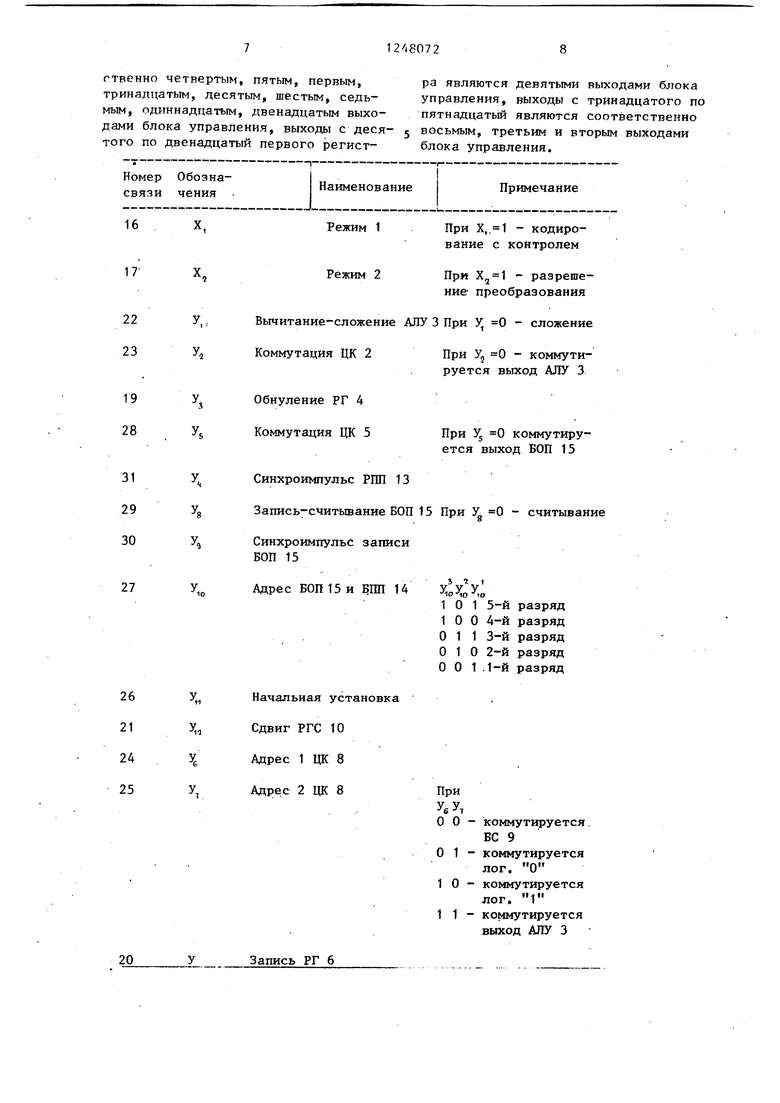

Необходимые для функционирования устройства управляющие и условные сигналы приведены в таблице.

45 Алгоритм функционирования цифро- аналогового преобразования в соответствии с вьштеприведенным показан на фиг.З и 4 состоит из: вершины (1-5) - обнуление БОП 15; вершины (6-15) 50 первое кодирование А с запретом

включения 4-го разряда; вершины (16- 26) - второе кодирование А„ без запрета включения 4-го разряда; вершины (27-28) - запись Кр„ в БОП 15;

55 вершины (29-39) - первое кодирование Ag с запретом включения 5-го разряда; вершины (40-50) - второе кодирование вершины (51-52) - запись- Кр в

БОГ 15, вершины (53-65) - непосредственное преобразование.

Формула изобретения

1 Устройство цифроаналогового преобразования, содержащее основной и вспомогательный цифроаналоговые преобразователи, блок сравнения, блок управления, первый и второй регистры регистр сдвига, выходы которого подключены к соответствующим входам вспомогательного цифроаналогового преобразователя, выход которого под- ключен к первому входу блока сравнения, второй вход которого соединен с выходной шиной устройства, выходы второго регистра подключены к соответствующим входам основного цифро- аналогового преобразователя, первый, второй и третий выходы блока управления подключены соответственно к первым управляющим входам первого, вто- рого регистров и регистра сдвига, отличающееся тем, что, с целью повышения точности за счет улучшения линейности характеристики преобразования, в него введены первый, второй и третий цифровые комму- таторы, блок постоянной памяти, блок оперативной памяти, регистр последо- :вательного приближения, арифметико- логическое устройство,, первые информационные входы которого объединены с информационными входами блока оперативной памяти и подключены к выходам первого регистра, вторые информационные входы подключены к выходам второго цифрового коммутатора, пер- вый выход подключен к первому информационному входу третьего цифрового коммутатора. Управляющий вход подключен к четвертому выходу блока управления, вторые выходы подключены к первым информационным, входам первого цифрового коммутатора, вторые информационные входы которого являются шинами преобразуемого кода, управляющий вход подключен к пятому выходу блока управления, выходы подключены к информационным входам первого регистра, второй управляющий вход которого объединен с информационным входом регистра последовательного при- ближения и подключен к выходу третьего цифрового коммутатора, второй ин- Аормационньш вход которого является

ш.иной сигнала логической единицы, третий информационный вход является шиной сигнала логического нуля, четвертый информационный вход подключен к выходу блока сравнения, первый и второй управляющие входы подключены соответственно к шестому и седьмому выходам блока управления, восьмой . выход которого подключен к второму управляющему входу регистра сдвига и к первому управляющему входу регистра последовательного приближения, девятые выходы подключены к адресным входам блоков оперативной и постоянной памяти, выходы которых подключены соответственно к первым и вторым входам второго цифрового коммутатора, управляющий вход которого подключен к десятому выходу блока управления, первый, второй и третий входы которого являются соответственно первой и второй управляющими шинами и шиной Запуск, одиннадцатый и двенадцатый выходы подключены соответственно к первому и второму управляющим входам оперативной памяти, тринадцатый выход подключён к второму управляющему входу регистра последовательного приближение, выходы которого подключены к информационным входам второго регистра, при этом выход основного цифроаналогового преобразователя является выходной щиной.

2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что блок управления выполнен на первом регистре, втором регистре, генераторе тактовых импульсов, постоянном запоминающем устройстве, первый и второй входы которого являются первым и вторым входами блока управления, выходы с первого по пятнадцатьй.подключены к информационным входам первого регистра, входы с третьего по девятый подключены к выходам второго регистра, выходы с шестнадцатого по двадцать второй подключены к информационным входам второго регистра, первый управляющий вход которого является третьим входом блока управления второй управляющий вход подключен к прямому выходу генератора тактовых импульсов, инверсный выход которого подключен к управляющему входу первого регистра, выходы с первого по девятый которого являются соответгтвснно четвертым, пятым, первым, ра являются девятыми выходами блока тринадцатым, десятым, шестым, седь- управления, выходы с тринадцатого по мым, одиннадцатым, двенадцатым выхо- пятнадцатьй являются соответственно

дами блока управления, выходы с деся-j восьмым, третьим и вторым выходами того по двенадцатый первого регист- блока управления.

1722 23

19 28

31 29 30

27

Режим 2

При - разрешение преобразования

Вычитание-сложение АПУ 3 При yj 0 - сложение

Коммутация ЦК 2

Обнуление РГ 4 Коммутация ЦК 5

Синхроимпульс РПП 13

При У, 0 - коммутируется выход АЛУ 3

При У 0 коммутируется выход БОП 15

Запись-считьшание БОИ 15 При У 0 - считывание

Синхроимпульс записи БОП 15

Адрес БОП 15 и ВШ1 14

y yV

w ю ю

У..

I

Начальная установка Сдвиг РГС 10 Адрес 1 ЦК 8 Адрес 2 ЦК 8

20

Запись РГ 6

вание с контролем

При - разрешение преобразования

При У, 0 - коммутируется выход АЛУ 3

При У 0 коммутируется выход БОП 15

y yV

w ю ю

1 о 1 5-й 1 О О 4-й О 1 1 3-й О 1 О 2-й О О 1.1-й

коммутируется

ЕС 9

коммутируется

лог. О

коммутируется

лог. 1

коммутируется выход АЛУ 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257848A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1257847A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Цифроаналоговый преобразователь | 1984 |

|

SU1216829A1 |

Изобретение относится к вычис- лительной и цифровой измерительной технике и может быть использовано для преобразования цифровых величин ,в аналоговые..Изобретение позволяет , повысить точность цифроаналогового преобразования за счет улучшения линейности характеристики преобразо- ванияо Улучшение линейности характеристики преобразования обеспечивается введением трех цифровых комму таторов, блоков постоянной и оперативной памяти, регистра последовательного приближения и арифметико- -логического устройства, а также по- строением основного цифроаналогового преобразователя (ЦАП) на основе избыточно-измерительного кода. Устройство работает в двух режимах: поверки основного ЦАП и преобразования входного кода в аналоговый сигнал. В режиме поверки определяются реальные веса основного ЦАП, которые затем хранятся в блоке оперативной памяти и используются при преобразовании входного кода в аналоговый сигнал. 1 з.п. ф-лы, 4 ил. i W с: to 4 СХ) О tc

| Цифроаналоговый преобразователь | 1979 |

|

SU864548A1 |

| Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи информации./Под ред | |||

| В.Б.Смолова | |||

| Л.: Энергия, 1976, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Способ утилизации отработанного щелока из бучильных котлов отбельных фабрик | 1923 |

|

SU197A1 |

Авторы

Даты

1986-07-30—Публикация

1984-09-11—Подача