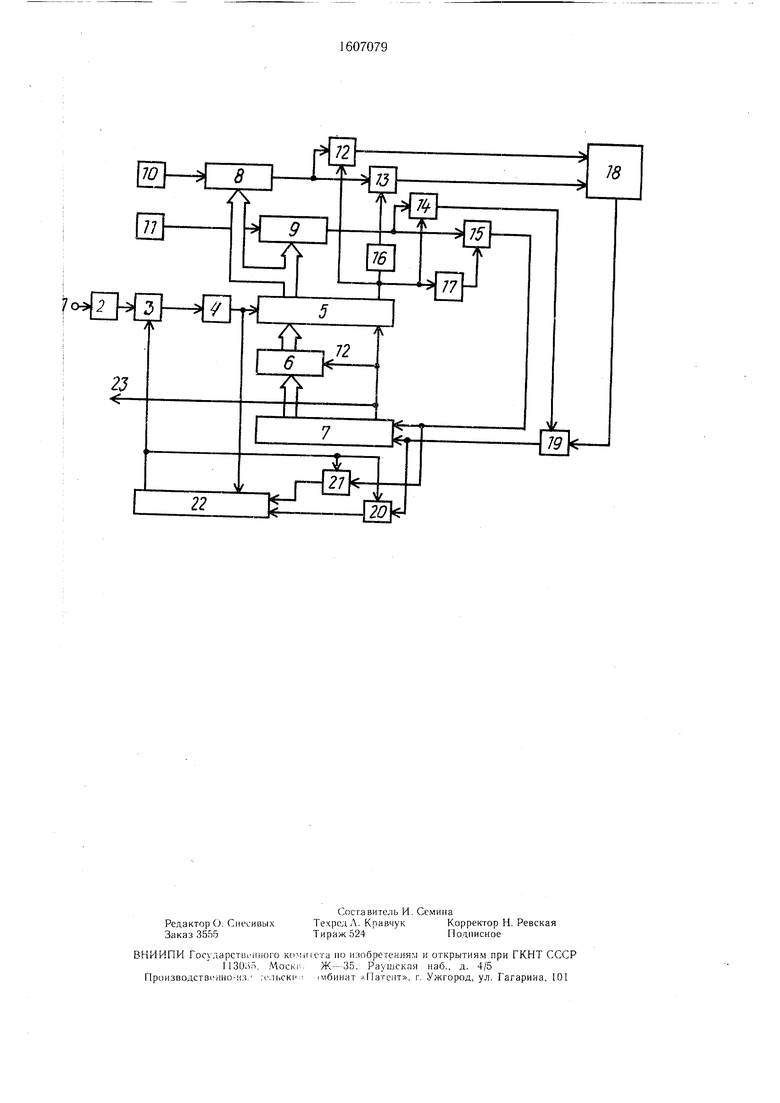

ма структурная

ZTa ,fi f--™- - о.р/з„,а „ ГкЦ 1 -Га-

первы.ми входа.ми элементов И 12 и 13 ч «к, ход преобразователя 9 код час4а сое и нен с первыми входами элементов и И выход знакового разряда регистпч

нен с вторыми вхо дами ле н оГи ,; 14 и через инверторы ifi |- i- и ц

Дами соотве ст. Выходы эле.ментов И 12 и 3 соеаиненм - первым и вторым входами генер ч цифровым управлением, выход ,,; 14 соединен с первым вxoдo, эле ент. ИЛИ 19, выход элемента И ir.cct- тсч - чхс, дом вычитания реверс и.,чо, . ..,,;:,:,;,- ,

cS; SJf;x---HTnt: ия-jsr-л:-;;-.

ния и вычитания реверсивного с егч к 7 соединены соответственно с ичфопмап.пг ными входами элемеитс.в ЗЛ1 выходы которых соо.и,нсны соот8е;ст,е,;ш с входами сложения и в.,читания евеп сивного счетчика 22. Выход nV ряда реверсивного счетчика - сое и ч и с вторым входом элемента И . и та к, Щими входами элеме,;тов ЗЛИРГТ О

вход сброса реверсинно о счс.-чн4 V , Динен с выходом диффере,имип.,:;,;- :.; на 4, выходная нлша 23 чтп (::ч--:-; -, - .

С

о о

со

ключена к выходу старшего разряда реьер- ц:;;о1 ;а-ройство тактовой синхрони- На Гд;ТгрГ Т2 т °п ает при- двоич ная последовательность символов «О и «1, которая может бьггь ис

„ сигнал,которь,и при иаличии иа в.

16070794

е7ж -;рГе;:::;™™ггт г E L-ri;srrij ar- o:

,ые в1оды регистра 5 после перехода от

тл гдггс-г - k - owrrs-- pSc,;r 5 р- 1--1г±нГ;о

-- - У Г°:Äà „а Г,стаГ: сиг; уровня беспрепятствеипи к--- : дифференцирующего звена 4 через эле ,ен-т И 3 Дифференцирующее звено 4 .. „..„vnn R поинимаемом сигнг

it Г.ТЙ1-,с.

ходе иреи 1 „,„,.,,„ на выходе ревТа:Г,еисто,„ика опорного сигнала S a;ra JnvLorHt eb Z/ Ko: -- -,; ,еаТеле« В - . ко.;--..

™«°:S,P : oro .Tat. - °--ГГ„; 9

вуючасло1у И „„„„„„, пазоядов ревер- „яртота служат для подстройки после30

1 V 1 и П nrlivi «- где N - число, двоичных разрядов ревер

Т,хГ старщего разряда реверсивного счетчика на выходную шину 23 устройства поступает меандр тактовой частоты, синхронизованный с принимаемым сигналом в режиме слежения по задержке (фазе) и частоте В момент поступления импульса Грсжта принимаемого сигнала на информа- и он,ые входы регистра 5 содержимое ре „,,„,,м,/п 7 R виде логически.

входы BD14niUJ ii .. -счегчика 7, путем добавления

Кшульс фронта, поступающий на вход управТеГя р е истра 5, -ступает также на вход сброса реверсивного счетчика 22, в ре

.

ЕЕ ЗЕНдаЕ

гель 6 кода, содержимое старшею РазряД начинают поступать 9

г;г:Гр з;г;™ ;р;гп; -««о с;ь„о.о. . --Т«° -гЬ,.Гс°г ;;ГоГ- nonsss ;s

трть о кода АЛ

реверсившго счетчика 7, соответствующего

Лчче О 360° в код, соответствующий фази„воичного символа --- ---- ,.„

п 180°480° 0 Такое преобразование осу-Д ои разряд меньщетв яётся переходом от основного пред- 45 реверсивный счетчик 7). на его вь,

сТавпения информации, имеющейся на ин-ш появится единичный уровень, в резуль

- -- - язоват я о ко-х Д -Гр :Г2ТГ1о.По1а

5: : и преобразова..,я6кс. да к дополнительному для фазового угла 18б...360° и сохранением исходного пред- г-ав1ения для фазового угла 0...18U . Уп- ра«е представления осу ествляется с помощью входа на этом входе имеется символ «О, что соот ветствует содержимому реверсивного счет dr :

,,,,,гчоиир входы оегистра b с Па50

тате чего откроется .лсм. . Пода- тякпоются элементы JAIU ci i ча Пульсов на входы сложения и вь,п. тания реверсивного счетчика 22 при этом поекоати-ся до поступления следующего им- nSa фронта на вход сброса реверсивного счетчика 22. Такая работа рассмаари- вяемь х -злов обеспечивает запирание входа устшГства на некоторое время, например устройства н,.j;двоичного

чика 7 меньше поливипш -.... ; г, ,,.тртустройства на нс,ч..р- / пппичного

V.bca ,„,, ,„,,, .„„а „Р„„-- швоп .0, соответствующий знаку «+.. „,„ая двоичная последовательность симво- Когда на входе знака преобразователя ко

«о с;ь„о.о. . nonsss ;s

„воичного символа --- ---- ,.„

разряд меньх Д -Гр :Г2ТГ1о.По1а

тате чего откроется .лсм. . Пода- тякпоются элементы JAIU ci i ча Пульсов на входы сложения и вь,п. тания реверсивного счетчика 22 при этом поекоати-ся до поступления следующего им- nSa фронта на вход сброса реверсивного счетчика 22. Такая работа рассмаари- вяемь х -злов обеспечивает запирание входа устшГства на некоторое время, например устройства н,.j;двоичного

устройства на нс,ч..р- / пппичного

ТО

лов искажена присутствием помех и шумов. В этом случае сигнал, имеющийся на выходе ограничителя 2, будет содержать импульсы с нулевым уровнем, когда принимается символ «Ь, и импульсы с единичным уровнем, когда принимается символ «О. Наличие таких импульсов может привести к тому, что на выходе дифференциального звена 4, появятся импульсы фронтов, отстоящие друг от друга на время, отличное от длительности целого числа двоичных символов. В тех случаях, когда мешающие шумы и помехи являются гауссовыми с малым (в сравнении с длительностью принимаемых двоичных символов) временем корреляции, что чаще всего встречается на практике, длительность мешающих импуль - сов на выходе ограничителя 2 будет малой или они будут следовать после импульса фронта через короткий интервал (например, меньше половины длительности двоичного

символа).

Таким образом, в цифровом устройстве тактовой синхронизации производится определение ошибки по задержке (фазовой ошибки) путем сравнения модифицированной местной последовательности импульсов

знака преобразователя кода и входу знакового разряда регистра, информационные выходы регистра соединены с информационными входами преобразователей код-частота, вторые входы которых соединены с выходами соответствующих генераторов импульсов, выход первого преобразоватетя код - частота соединен с первыми входами первого и второго элементов И, а выход второго преобразователя код --- частота - с первыми входами третьего и четвертого элементов И, выход знакового разряда регистра соединен с вторыми входами первого и третьего элементов И и через соответствующие инверторы - с вторыми входами второго и четвертого элементов И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами генератора с цифровым управлением, выход третьего элемента И соединен с первым входом апемента ИЛИ, второй вход которого ,п соединен с выходом генератора с цифровым управлением, а выход - - с входом сложения реверсивного счетчика, вход вычитания которого соединен с выходом четвертого элемента И, выход старшего разряда реверс ивно- го счетчика соединен с выходной шиной устной местной iiocjicAut5ciicjionv..iM г.,„.„„ппйгтвя от гичаюше ся тем,

с входной последовательностью импульсов ,,,,,,

моменты перехода в последней от «1 к «и. Измеренная ошибка по задержке (фазовая ошибка) при этом преобразуется в пocлeJ довательность импульсов, частота которой пропорциональна величине этой ошибки, а JQ указанная последовательность импульсов служит для коррекции скорости продвижения реверсивного счетчика 7 в соответствии со знаком указанной ошибки.

Формула изобретения,

Цифровое устройство тактовой синхронизации, содержащее дифференцирующее звено выход которого подключен к входу

управления регистра, информационные вхо-р вёрсивного счетчика. информационные вхо

ды которого соединены с выходами преоб- 40 , ,.э;к ментов З.ЛПРЕТ

разовате..я кода, инФY °;;oнн ымTв Lx o одшеш соответственно с входами слон.е- торого соединены с информационными выхо- вычитания первого реверс1 вно1ч,

дами реверсивного счетчика, выход стар- « и ,

шего разряда которого подключен к входусчетчика.

что. с целью повышения помехоустойчивости при наличии дробления переднего фронта импульса, оно дополнительно содержит второй реверсивный счетчик, ограничитель, два элемента 3. ПРЕТ и пятый э,- емент И. причем входная шина устройства через ограничитель подключена к первому входу пятого элемента И. выход которого соединен с входом дифференцирующего звена, выход которого подключен к в.чоду сброса второго реверсивного счетчика, входы сложения и вычитания реве)- сивного счетчика соединены соответственно с выходами первого и второго элементов ЗАПРЕТ, управляющие входы которых соединены с вторым входом пятого элемента и и выходом старшего разряда второго

знака преобразователя кода и входу знакового разряда регистра, информационные выходы регистра соединены с информационными входами преобразователей код-частота, вторые входы которых соединены с выходами соответствующих генераторов импульсов, выход первого преобразоватетя код - частота соединен с первыми входами первого и второго элементов И, а выход второго преобразователя код --- частота - с первыми входами третьего и четвертого элементов И, выход знакового разряда регистра соединен с вторыми входами первого и третьего элементов И и через соответствующие инверторы - с вторыми входами второго и четвертого элементов И, выходы первого и второго элементов И соединены соответственно с первым и вторым входами генератора с цифровым управлением, выход третьего элемента И соединен с первым входом апемента ИЛИ, второй вход которого п соединен с выходом генератора с цифровым управлением, а выход - - с входом сложения реверсивного счетчика, вход вычитания которого соединен с выходом четвертого элемента И, выход старшего разряда реверс ивно- го счетчика соединен с выходной шиной устппйгтвя от гичаюше ся тем,

,,,,,,

JQ

,

р вёрсивного счетчика. информационные вхо

что. с целью повышения помехоустойчивости при наличии дробления переднего фронта импульса, оно дополнительно содержит второй реверсивный счетчик, ограничитель, два элемента 3. ПРЕТ и пятый э,- емент И. причем входная шина устройства через ограничитель подключена к первому входу пятого элемента И. выход которого соединен с входом дифференцирующего звена, выход которого подключен к в.чоду сброса второго реверсивного счетчика, входы сложения и вычитания реве)- сивного счетчика соединены соответственно с выходами первого и второго элементов ЗАПРЕТ, управляющие входы которых соединены с вторым входом пятого элемента и и выходом старшего разряда второго

im

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Устройство слежения за задержкой кодовой последовательности | 1985 |

|

SU1338093A1 |

| Адаптивный аналого-цифровой преобразователь | 1979 |

|

SU866734A1 |

| Адаптивный аналого-цифровой преобразователь | 1985 |

|

SU1288910A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Электропривод постоянного тока | 1983 |

|

SU1100697A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261116A1 |

| Устройство для отображения информации | 1986 |

|

SU1325456A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1451861A1 |

| Коррелятор | 1988 |

|

SU1705835A1 |

Изобретение относится к технике связи и может быть использовано, преимущественно, в устройствах синхронизации систем радиосвязи. Целью изобретения является повышение помехоустойчивости при наличии дробления переднего фронта импульса. Цифровое устройство содержит два реверсивных счетчика, регистр, преобразователь кода, два преобразователя код - частота, два генератора импульсов, генератор с цифровым управлением, ограничитель, дифференцирующее звено, элементы И, ИЛИ, ЗАПРЕТ и инверторы. 1 ил.

Авторы

Даты

1990-11-15—Публикация

1985-02-19—Подача