по

Изобретение относится .к вьиисли- тельяой технике и может быть исполь- зова но при разработке вычислительных систем с повьппенными требованиями к достэверности получаемых результатов.

Цель изобретения - повьппение достоверности контроля.

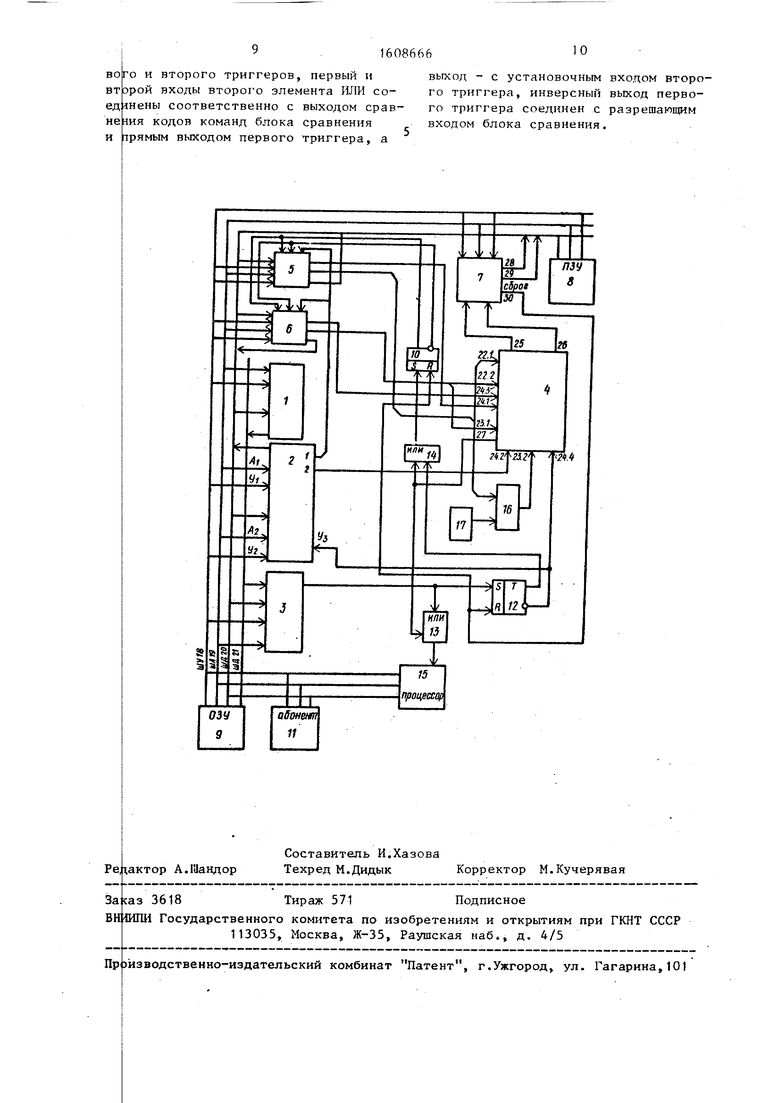

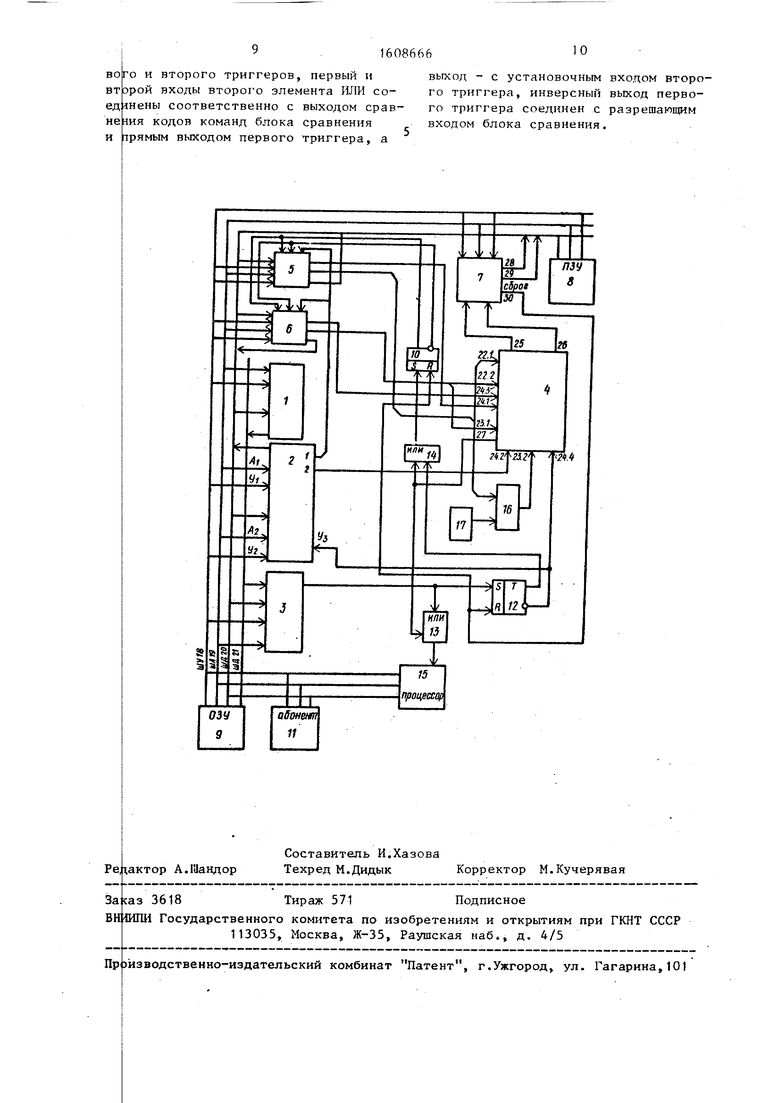

На чертеже представлена схема устройства.

стройство содержит блок 1 сверт- модулю, первый блок 2 буферной

блок 3 контроля по модулю, 4 сравнения, второй блок 5 бу- памяти, третий блок 6 буферной блок 7 выдачи признака ре- , блок 8 постоянной памяти, 9 оперативной памяти, первый ер 10, абонент 11, второй триг- 12, первый 13 и второй 14 злеменпроцессор 15, сумматор 16, 17 задания смещения. Процессор Злоки 1, 8 и 9 и абонент 11 явля- узлами контролируемой ЭВМ. На

памя ги

ки

па

блок

ферной

памяти

зульгата

блок

три г

гер

ты И№

блок

15,

ются

схеме также изображены: шина 18 управления, шина 19 адреса, шина .0 данных и шина 21 контрольных разрядов, входы 22.1 и 22.2 сравниваемых кодов опеоаш1и, входы 23.1 и 23.2 сравниваемых адресов операндов,входы 24.1-24.3 сравниваемых команд и вход 24.4 разрешения блока 4 сравнения,выходы которого: 25 - сравнения кодов операций, 26 - сравнения адресов операндов, 27 - сравнения команд; выходы 28 совпадения адресов операндов,

29- совпадения кодов операций,

30- сброса блока 7 вьщачи признака результата.

Блок 17 задания смещения представляет собой набор переключателей.

Работа устройства может осуществляться в двух режимах.

При первом режиме функционирования ошибок в работе ycTpoiicTBa . нет, т.е. на выходе блока 3 контроля сигнал отсутствует. В этом режиме

(Л

О5

о

00

о: о:

О5

осуществляется контроль функциониро вания блока 2 путем перестройки устройства, т.е. в этом случае для контроля работы блока 2 информация параллельно записывается еще в два блока памяти 5 и 6. Если возникает ошибка в функционировании, то устройство сразу перестраивается во второй режим работы, блоки 5 и 6 начинают вьтолнять .возложенные на них; функции.

Для исключения ложного срабатывания блока 4 его разрешающий вход соединен с инверсным выходом триггера 12.

Второй блок 5 буферной памяти работает следующим образом. При отсутствии сигнала запроса прерывания весь формат текущей команды поступает на вход блока 5. Для считывания текущей команды с блока 5 на его вход поступает адрес, присвоенный блоку 5, а на шину 18 управлния постзшает команда считывания. По этому сигналу информация с блока 5 поступает на выход блока 5, а с него - на шину 20 данных. Запись формата команды с шины 20 данных в блок 5 осуществляется при наличии сигнала записи на шине

18управления при наличии адреса блока 5 на шине 19 адреса.

При наличии сигнала запрос прерывания перебрасывается на триггер 10 от триггера 12 или от сигнала, снимаемого с выхода 27 блока 4 сравнения, чт о приводит к выдаче информа- ции на выход блока 5.

Работа второго блока 6 буферной памяти аналогична работе блока 5.

Блок 7 выдачи признака результата работает следующим образом. Для выбора этого блока поступает код по шине

19адреса, соответствуюпщй данному блоку. На вход блока 7 с шины 18 управления поступает сигнал считывания, который также подготавливает данный блок к работе. При поступлении на его вход сигнала с-выхода 25 блока 4 сравнения, который обеспечивает сравнение кодов операций, с выхода блока 7 информахщя поступает на шину 20 анных. При поступлении сигнала на вход блока 7 с выхода 26 блока 4 сравнения, который обеспечивает сравнение адресов операндов, данная инормация поступает на шину 20 данных. Наличие сигналов на выходах 28 и 29 блока 7 является признаком того , что

0

5

0

искомая ячейка блока 9 оперативной памяти найдена. Только после этого на шине 18 управления появится сигнал Сброс, который поступает на вход блока 7 и, при наличии адреса блока 7 на шине 19 адреса, с выхода блока 7 снимается сигнал сброса на триггеры 10 и 12.

В блоке 8 постоянной памяти и блоке 9 оперативной памяти наиболее важные команды записываются в дублированные ячейки. Так, в блоке 8 постоянной памяти записана команда считывания, причем адрес команды считывания (АКС1) будет отличаться от адреса команды считывания второй на единицу (АКС1+1). По адресу операнда 1 записывается в операнд 1 (), а по адресу операнда 2 записывается операнд 2, причем адреса этих операндов будут отличаться на величину смещения А.

25

АО,2

+ А

сме1ц

0

5

0

5

0

5

Устройство работает следуюш 1м образом.

Процессор 15 работает по программе, записанной в блоке 8 постоянной памяти. Команды могут записывать либо считывать операнды с блока 9 оперативной памяти. Запись в блок 9 оперативной памяти всегда сопровождается формированием и занесением контрольных кодов в контрольные разряды, которые формируются следующим образом.

По шине 20 данных операнд поступает на вход блока 1 свертки, где сворачивается по модулю q, и при поступлении по шине адреса кода адреса, соответствующего данному блоку, и при наличии сигнала Запись на щине 18 управления контрольный код поступает на шину 21 контрольных разрядов и далее - на запись в контрольный разряд блока 9 оперативной памяти.

При считывании операнда он поступает по шине 20 данных на вход блока 3 контроля, где сворачивается по модулю q и сравнивается с контрольными разрядами, поступающими по шине 21 контрольных разрядов. После опознания адреса зоны блока 9 оперативной памяти и при наличии сигнала считывания с ишны 18 управления начинается процесс сравнения.

в блоки 2.

J и

с шины 20 данных

заг|исывается формат команды в момент ее считывания с блока 8 постоянной памяти. Блок 4 сравнения осуществляет

в этом случае, сравнение записанной в блоки 2, 5 и 6 информации.

Если в процессе считывания информации с блока 9 оперативной памяти

86666

ция тто( на входы блока 4 сравнения и сумматора 16. Б.чок 4 сравнивает К071Ы операций считывания. На второй вход сумматора 16 подается смешение (j с/лещ - блока 17 задания смещения. На сумматора 16 значение выходной информации будет определяться выражением

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1439605A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство сопряжения процессора с арифметическим расширителем | 1985 |

|

SU1298758A2 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке вычислительных систем с повышенными требованиями к достоверности получаемых результатов. Целью изобретения является повышение достоверности контроля. Устройство содержит блоки буферной памяти, блок контроля по модулю, блок сравнения, блок выдачи признака результата, триггеры, элементы ИЛИ, сумматор и блок задания смещения. 1 ил.

произойдет ее искажение,то это обнаружится блоком 3 контроля, так как эталонный остаток по модулю q будет от:;ичаться от значения остатка по мо;;улю q, вычисленного на данный момент времени. Это приведет к перебро- t5 С1твляет сравнение адресов операндов су в единичное состояние триггера 12, ас выхода элемента ИЛИ 13 на процессор 15 поступит сигнал запроса прерывания. Переброс триггера 12 приведет к перебросу в единичное сос;тояние триггера 10 и блокировке

20

двух команд, С выхода блока 6 информ ция поступает на вход 23,1 блока 4 сравнения и на вход 22,2 блока 20 сравнения. Выходные сигналы выходов 25 и 26 блока 4 сравне1гая поступают на блок 7 выдач1{ признака результата Опрос блока 7 осуществляется при наличии сигнала считывания на ишне 18 и его кода адреса на шине адреса. По явление сигнала на выходе 29 блока 7 признака вида ячейки свиедетельству- ет о том, что коды операций считывания совпали. Появление сигнала на выходе 28 этого блока свидетельствует о том, что адреса операндов первой и второй команды совпали, С этого момента начинается процесс восстановления сбившейся информации, т,е, информация с ячейки блока 9 опе ративной памяти, соответствующая адресу второго операнда, переписывается в ячейку по адресу первого операнда. После этого процессор 15 по Ш1не 18 управления выдает команду сброса, которая приходит на вход блока 7 и при наличии кода адреса на шине 19 выхода 30 блока 7 вьща- ется сигнал на приведение в исходное со стояние триггеров 12 и 10. После вос

бЛ(

1ка

Таким образом, в блоке 2 будет записан формат текущей команды.

Переброс триггера 10 приводит к переводу блоков 5 и 6 в режим выдачи информации. Сигнал запроса пре- рынания может формироваться и в случае неравенства информации, поступающей на входы блока 4 сравнения, В Г Том случае сигнал с выхода 27 блока 4 сравнения приводит к перебросу в единичное состояние триггера 10 и поступает на вход элемента ИЛИ 13. С выхода последнего сиг- Haj: .запроса прерывания поступает на вход прерывания процессора 15. Посла поступления сигнала запроса пре- рыиания процессор 15 выдает соответ- стиующие команды на шину адреса 19 и :гправления 18 с целью перезаписи инсюрмации с блока 2 во внутренний регистр процессора. После этого в соответствии с информацией, записанной во внутренний регистр процессора 15, он выдает команду на считыва- HH(i формата первой команды из блока 8. ее

ли1 ивает адрес кода считывания и за- пи( ынает эту информацию в свой второй внутренний регистр. Затем в соответствии с записанной информацией во второй регистр 15 процессора из блока 8 постоянной памяти считывается формат второй команды.Эта команда записывается в блок 6. Формат первой команды поступает на выход

Одновременно осуществляется запис в блок 5. Далее процессор 15 увебл

жа 5, с выхода которого информа

АО,, 7.

AOJ

+ А

с ец

Эта информация поступает на вход 23,2 блока 4 сравнения. Блок 4 осуще5 С1твляет сравнение адресов операндов

0

5

0

двух команд, С выхода блока 6 информация поступает на вход 23,1 блока 4 сравнения и на вход 22,2 блока 20 сравнения. Выходные сигналы выходов 25 и 26 блока 4 сравне1гая поступают на блок 7 выдач1{ признака результата. Опрос блока 7 осуществляется при наличии сигнала считывания на ишне 18 и его кода адреса на шине адреса. Появление сигнала на выходе 29 блока 7 признака вида ячейки свиедетельству- ет о том, что коды операций считывания совпали. Появление сигнала на выходе 28 этого блока свидетельствует о том, что адреса операндов первой и второй команды совпали, С этого момента начинается процесс восстановления сбившейся информации, т,е, информация с ячейки блока 9 оперативной памяти, соответствующая адресу второго операнда, переписывается в ячейку по адресу первого операнда. После этого процессор 15 по Ш1не 18 управления выдает команду сброса, которая приходит на вход блока 7 и при наличии кода адреса на шине 19 выхода 30 блока 7 вьща- ется сигнал на приведение в исходное состояние триггеров 12 и 10. После вос5 становления информации в дублированных ячейках процессор 15 проверяет правильность восстановления считывания информации с каждой ячейки блока 9 оперативной памяти и отсутQ ствие при этом сигнала запроса прерывания на выходе элемента ИЛИ 13.

Если же при опросе блока 7 с выхода 29 снимается сигнал, эквивалентный логическому нулю, что свидетельствует о неравенстве кодов операций считывания в блоке 4 сравнения, про- цессор 15 переписывает информацию со своего внутреннего регистра во второй внутренний регистр, Информа5

0

5

716

ция с блока 5 считывается на шину 20 данных в процессор 15. Процессор 15 эту информацию переписывает в блок 6. Далее процессор 15 уменьшает адрес кода считывания второй команды на (циницу и записывает команду в свой, первый внутренний регистр. Теперь по этому адресу считывается информация из блока 8 постоянной памяти и записывается в блок 5. После этого повторяется процесс сравнения в блоке 4 сравнения. Если при повторном опросе блока 7 нет сигнала, эквивалентного логической единице на выходе 9, значит обращение было не к дублированным ячейкам и восстановление информации невозможно. Аналогичный вывод делается, если нет сравнения адресов операндов, т.е. нет сигнала, эквивалентного логической единице, на выходе 28 блока 7 признака вида ячейки при повторном опросе.

Если же сигналы, эквивалентные логической единице,на выходе 28 и 29 блока 7 при повторном опросе имеются, то начинается процесс восстановления информации аналогично описанному.

Формула изобретения

Устройство для контроля ЭВМ, содержащее первый блок буферной памяти, блок сравнения, первый элемент ИЛИ, отличающееся тем, что, с целью повышения достоверности контроля за счет восстановления искаженной информации, оно содержит блок контроля по модулю, первый и второй триггеры, второй и третий блоки буферной памяти, сумматор, блок выдачи признака результата, блок задания смещения, второй элемент ИЛИ,

адресный вход первого блока буферной ..с ционным входом блока сравнения, выпамяти является входом устройства для соединения с шиной адреса ЭВМ, а входы записи и чтения являются входами устройства для подключения к шине управления ЭВМ, первый выход первого блока буферной памяти соединен с первым информационным входом блока сравнения, информационный вход- выход первого блока буферной памяти является входом-выходом устройства для подключения к шине данных ЭВМ, разрешаю1чий вход - к инверсному выходу первого триггера, а второй информационный выход - к первым йнфор50

55

ходы сравнения кодов операции и срав нения адресов операторов блока сравнения соединены соответственно с пер вым и вторым информационными входами блока вьщачи признака результата, адресный и разрешающй входы блока выдачи признака результата являются входами устройства для подключения к шинам адреса и управления ЭВМ, первый и второй информационные выходы блока выдачи признака результата являются выходами устройства для подключения к шине данных ЭВМ, а выход сброса соединен с входами сброса пер

8

0

n

5

5

0

5

0

мационным входам второго и третьего блоков буферной памяти, информационные вход и выход блока контроля по модулю являются входом и выходом устройства для подключения к шине, данных ЭВМ, а контрольные вход и выход - входом и выходом устройства для подключения к шине контрольных разрядов ЭВМ, адресный и управляюпщй входы блока контроля по модулю являются входами устройства для подключения соответственно к шинам адреса и управления ЭВМ, выход блока контроля по модулю соединен с установочным входом первого триггера и первым входом первого элемента ИЛИ, второй вход которого соединен с выходом сравнения кодов команд блока сравне- ,ния, выход первого элемента ИЖ является выходом устройства для подключения к шине прерывания ЭВМ, прямой и инверсный выходы второго триггера соединены с первым и вторым разрешающими входами второго и третьего блоков буферной памяти, вторые информационные входы которых являются входами устройства для подключения к шине данных ЭВМ, адресные и режимные вхо-т ды второго и третьего блоков буферной памяти являются входами устрой- ства дпя подключения к шинам адреса и управления ЭВМ, первые выходы второго и третьего блоков буферной памяти соединены соответственно с вторым и третьим информационными входами блока сравнения,а вторые выходы являются выходами устройства для подключения к шине данных ЭВМ, третий выход второго блока буферной памяти соединен с первым входом сумматора, второй вход и выход которого соединены соответственно с выходом блокад задания смещения и четвертым информа0

5

ходы сравнения кодов операции и сравнения адресов операторов блока сравнения соединены соответственно с первым и вторым информационными входами блока вьщачи признака результата, адресный и разрешающй входы блока выдачи признака результата являются входами устройства для подключения к шинам адреса и управления ЭВМ, первый и второй информационные выходы блока выдачи признака результата являются выходами устройства для подключения к шине данных ЭВМ, а выход сброса соединен с входами сброса первого и второго триггеров, первый и ВТ эрой входы второго элемента ИЛИ со- efliHBHU соответственно с выходом срав- нелкя кодов команд блока сравнения и трямым выходом первого триггера, а

выход - с установочным входом второго триггера, инверсный выход первого триггера соединен с разрешающим входом блока сравнения.

| Дуплексная система вычислительных машин | 1977 |

|

SU752343A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для подачи сигарет | 1978 |

|

SU923359A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-11-23—Публикация

1987-01-16—Подача