шя1.

4

оо

Изобретение относится к вычислительной технике и может быть исполь- .зовано в системах автоматического управления на базе

Цель изобретения - увеличение объема памяти для хранения программы ЭВМ, повышение быстродействия ЭВМ и расширение области его приг-шнения.

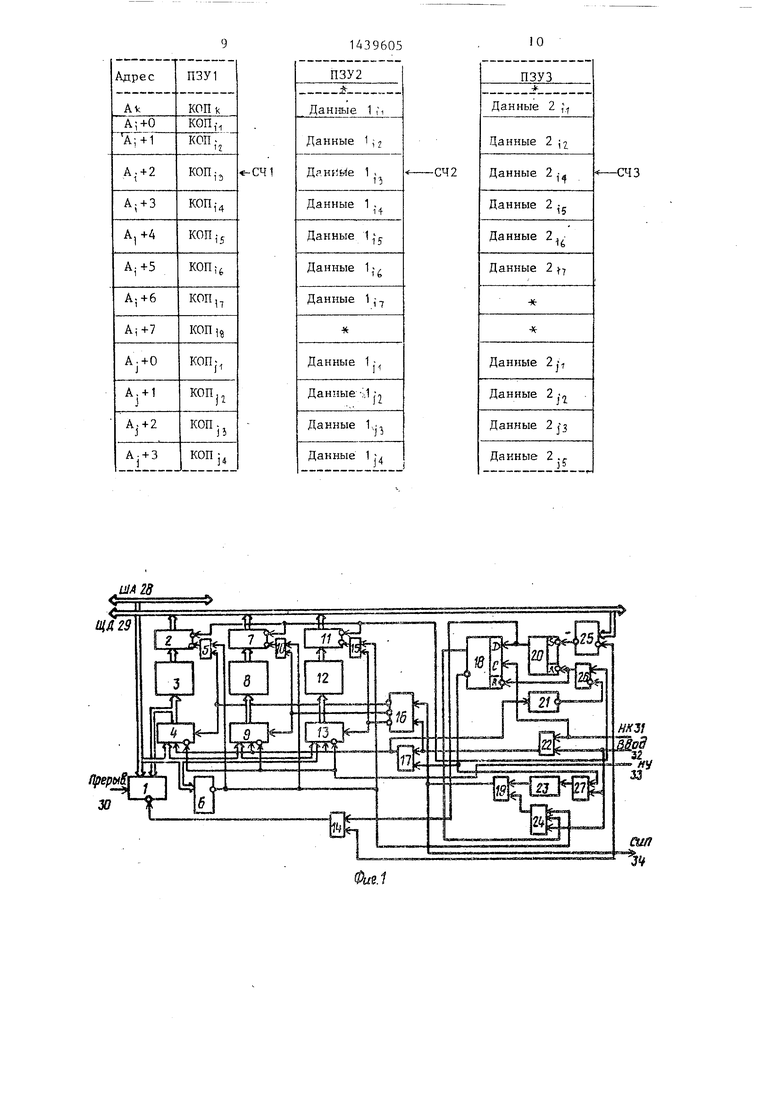

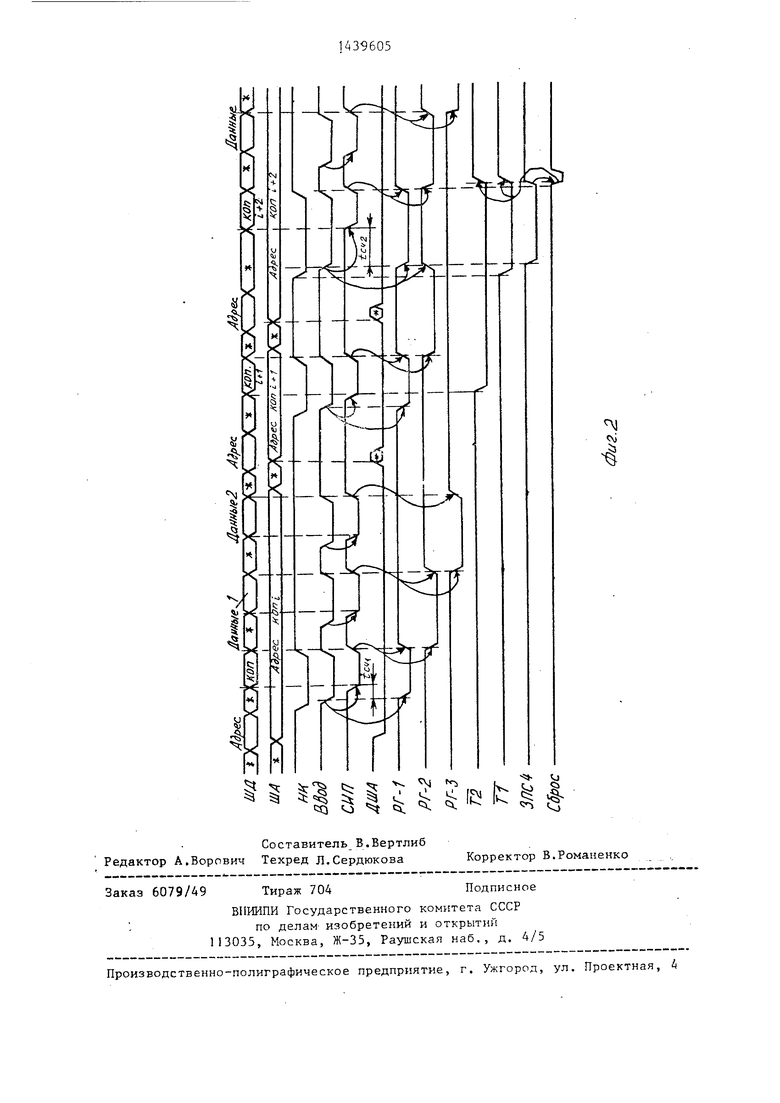

На фиг.1 представлена функциональная блок- схема устройства5 на фиг,2 - временная диагра1-1ма работы устройства.

Устройство содержит (фиго1)-блок 1 сравнения, первый буферный регистр 2, первый блок 3 постоянной памяти, первый 4 счетчик, третий элемент ИЛИ 5, дешифратор 6 адреса, второй буферный регистр 7, второй блок 8 постоянной памяти, второй счетчик 9, четвертый элемент ИЛИ 10, третий буферный регистр 11, третий блок 12 постоянной памяти, третий счетчик 13, восьмой элемент ИЛИ 14, пятый.элемент ИЛИ 15, сдвиговый регистр 16, второй элемент ИЛИ 17, первый триггер 18. первый элемент И 19, второй триггер 20, формирователь 21 и myльca (ждз пдай мультивибратор) , седьмой элемент ИЛИ 22, . элемент 23 задернжи, первый элемент ИЛИ 24, блок 25 постоянной программируемой памяти, второй элемент И 26,, хйестой элемент ИЛИ 27, шина 28 адре-- са (ША), тнна 29 данных (ШД)j линия

30сигнала прерывания (npepbfa), линия

31сигнала начала комавды .(НК) « линия

32сигнала Ввод, Линия 33 сигнала начальной установки (НУ), линия 34 сигнала синхронизации пассивного устройства (СИП).

На фиг.2 представлена временная диаграмма работы устройства, где ШД - информация на шине 29 данных § М - информация на шине 28 адреса; НК - сигнал начала команды на линии 315 Ввод - сигнал ввода информащи в процессор ЭВМ на линии 32| СИП - сигнал синхронизации пассивный на линии 34; ДШЛ - сигнал на выходе де

шифратора 6; РГ - 1, РГ 2, РГ 3

50

сигналы на первом, втором, третьем выходах сдвигового регистра 16, Т2 - сигнал на инверсном выходе триггера 20, Т1 - сигнал на инверсном выходе триггера. 18; ЗП 04 - сигнал записи информации в первыйэ второй, третий 55 счетчики СЧГ 4, СЧ2 9, СЧЗ 13 на выходе элемента ИЛИ 17, Сброс - сигнал сброса первого 18 и второго

,

5

0

5

20 триггеров на выходе ждущего мультивибратора 21; КОП - код операции текущей команды программы ЭВМ; tcq )зремя считывания информации из буферных регистров (ББ1)2, ББ2 7, ББЗ lij время считывания информации из первого блока постоянной памяти . (ПЗУ1) 3,

Расположение информации в блоках 3j 8 и 12. иллюстрируется таблицей, где Ак.5 А-5 Ai - относительные адреса соответствующие kj i, j-м линейным участкам программы ЭВМ.

Устройство работает следующим образом,

В основе функционирования устройства лезкит тот факт, что команды в современных микроЭВМ бьшают одно-, двух- и трехсловными. При этом словом является код операции, а вторым и третьими словами - данные команды (адресные слова операндов или константы) , При этом следует отметить, что использование многословных команд в программах значительно повышает удобство в подготовке программы, но при этом снижает быстродействие за счет более частного обращения к запоминающим устройствам и увеличивает объем памяти для хранения программ из-за необходимости хранения дополнргтепькык слов команд,

В микропрограммах, реали зующих команды ЭВМ, ввод слов команды ведется последовательно; ввод первого слова; ввод второго слова ввод третьего слова (.для трехслойной команды) j после чего вьтолняется операция над операндами и формируется адрес следующей команды. Это позволяет вводить в состав памяти ЭВМ дополнительные блоки функциональной памяти (для данных второго слова команд и для данных третьего слова команд) и иокт пючить фазы передачи адреса для ввода второго и третьего спов команды, а также ввести контроль исполнения линейных участков программы ЭВМ с целью выявления сбоевJ приводящих к несанкционированным переходам ЭВМ внутри линейных последовательностей команд программы.

Устройство сопрягается Ь процессором ЭВМ следующим образом.

Информационный вход-выход устройства подключается к шине 29 данных, адресный вход устройства подключается к шине 28 адреса9 вход 31 подключается к линии сигнала начала команды (НК) процессора, причем сигнал НК вырабатывается на время ввода кода выполняемой команды в процессор ЭВМ, активным уровнем сигнала НК-является логический О.

В линии 32 сигнал Висд вырабатывается процессором во время ввода информации в процессор ЭВМ, активный

процесса сравнения в блоке 1 сравн ния адреса текущей ячейки памяти, выдаваемого счетчиком команд проце сора ЭВМ на шину 27, и адреса ячей ПЗУ1 3, выдаваемого счетчиком. А. П несовпадении этих адресов блок 1 в дает сигнал Прерыв, который перед ется в процессор ЭВМ по линии 30, Этот сигнал может вызвать прерыван

10

15

программы прерывания, восстанавлива щей вычислительный процесс. Дешифра тор 6 настроен на поле адресов, зан маемых блоком памяти ПЗУ1 3, Г13У2 8 и ПЗУЗ 12.

Линейные участки програьгмы закан

20

.1да : друго

коман i 3 neoGx

- J . Uij с КОТ

25

уровень сигнала Ввод - О, на вход ЭВМ, которая перейдет к обработке 33 при включении питания подается сигнал начальной установки (НУ), активный уровень сигнала НУ - О, в линии 30 сигнала прерывания (Прерыв) процессора активный уровень сигнала Прерыв - О, в линии 34 процессор сигнал ОТП вырабатывает в ответ на сигнал Ввод устройством на время -вывода информации из памяти, активный уровень сигнала СИП - О.

Память в предлагаемом устройстве функционально разделена: блок (ПЗУ 1) 3 хранит первое слово (коды операций) команд, блок (ПЗУ 2) 8 - второе слово команд (данные 1), блок (ПЗУ 3) 12 - третье слово команд (данные 2),-, ЦЗУ по сравнению с буферными блоками обладают более значительным временем выборки, и для сокращения цикла выборки из памяти информация из ПЗУ1 3, ПЗУ2 8, ПЗУЗ 12 поступает на шину 29 через буферные регистры ББ1 2, ББ2 7, ББЗ 11 соответственно. Последовательность подключения буферных регистров 2,7,11 к ШД 29 определяет сдвиговый регистр 16. Сигналы с выходов регистра 16 обеспечивают также наращивание счетчиков 4, 9 и 13.

В таблице показано размещение информации в ПЗУ1 3, ПЗУ2 8, ПЗУЗ 12 и для примера показано, что после выборки из памяти i-й трехсловной команды произошло наращивание не единицу счетчиков 4, 9, 13, которые указывают на соответствующие ячейки ПЗУ1 3, ПЗУ2 8, ПЗУЗ 12. В этих ячейках хранятся соответственно в ПЗУ1 3в

30

КОП-;,, в ПЗУ2 8 - данные 1нз и

чивают,ся командами iie - i му линейному учгтстку :;; этому после выборки ля перехода в счетчики ч, димо загрузить адрес кс рой начинается линейпь;: участок про граммы. Для этого блок ПОСТОЯННО

программируемой памяти (НИЗУ) 25 пр грамируется таким образом, -м-о если на пшне 29 появляется код ко Тапды п рехода, то сигнал с выхоп ; ППЗУ 25 устанавливает Б един лчное состояние триггер 20, который (-: ,, -п;яяр : в единичное состояние трг.ггегп 18 м формирование с выхода элсмег.та ИЛИ

17сигнала записи в счетчь-ки 4. 9, 13 с шины 28 адреса перехола,

Сигналом НУ обнуляются триггеры

18и 20 через элемент И 26 и счетчи ки 4, 9, СЧЗ 13. Таким образом, уст ройство приводится в началг-пое состояние.

Рассмотрим выполйение i-ii трехсловной команды, затем ()-й команды перехода (фиг.2). После выпол нения (1-1)-й команды процессор ЭВМ передает по пшне 29 адрес ячейки ПЗУ, в которой хранится код операци 5 i-й команды (КОП;), после выставлеп этого адреса на шине 28 процессор ЭВМ вырабатывает сигналы НК, затем Ввод, передаваемые по линиям 31 . и 32. Эти сигналы поступают на вход

35

40

ПЗУЗ 12 - данные 2-J4 так как 13-я

команда - двухсловная и СЧЗ 13 указы- 50 элемента ИЛИ 22, на выходе которого

вает на данные 2-;д -и команды. устанавливается уровень О. Этим

Так как программа, хранящаяся в памяти, состоит из участков линейных последовательностей команд, то это позволило также смоделировать на счетчике 4 счетчик команд процессора ЭВМ. Последнее обстоятельство позволило ввести контроль вычислительного

396054

процесса сравнения в блоке 1 сравнения адреса текущей ячейки памяти, выдаваемого счетчиком команд процессора ЭВМ на шину 27, и адреса ячейки ПЗУ1 3, выдаваемого счетчиком. А. При несовпадении этих адресов блок 1 выдает сигнал Прерыв, который передается в процессор ЭВМ по линии 30, Этот сигнал может вызвать прерывание

10

ЭВМ, которая перейдет к обработке

программы прерывания, восстанавливающей вычислительный процесс. Дешифратор 6 настроен на поле адресов, занимаемых блоком памяти ПЗУ1 3, Г13У2 8 и ПЗУЗ 12.

Линейные участки програьгмы закан-

ЭВМ, которая перейдет к обработке

0

.1да : друго:-М; ти команд i 3 neoGxo- J . Uij с КОТО5

ЭВМ, которая перейдет к обработке

0

чивают,ся командами iie - i му линейному учгтстку :;; этому после выборки ля перехода в счетчики ч, димо загрузить адрес кс рой начинается линейпь;: участок программы. Для этого блок ПОСТОЯННО

программируемой памяти (НИЗУ) 25 про- грамируется таким образом, -м-о если на пшне 29 появляется код ко Тапды перехода, то сигнал с выхоп ; ППЗУ 25 устанавливает Б един лчное состояние триггер 20, который (-: ,, -п;яяр : в единичное состояние трг.ггегп 18 м формирование с выхода элсмег.та ИЛИ

17сигнала записи в счетчь-ки 4. 9, 13 с шины 28 адреса перехола,

Сигналом НУ обнуляются триггеры

18и 20 через элемент И 26 и счетчики 4, 9, СЧЗ 13. Таким образом, устройство приводится в началг-пое состояние.

Рассмотрим выполйение i-ii трехсловной команды, затем ()-й команды перехода (фиг.2). После выполнения (1-1)-й команды процессор ЭВМ передает по пшне 29 адрес ячейки ПЗУ, в которой хранится код операции 5 i-й команды (КОП;), после выставлепия этого адреса на шине 28 процессор ЭВМ вырабатывает сигналы НК, затем Ввод, передаваемые по линиям 31 . и 32. Эти сигналы поступают на входы

5

0

сигналом сдвиговьиЧ регистр 16 устанавливается в исходное состояние, при котором на первом выходе его - О, 55 на втором и третьем выходах - 1, Это означает, что блок 2 открыт через элемент ИЛИ 5. Сигнал Впод также через элемент ИЛИ 24 и первый злемент И 19 формирует сигнал СИП, который передается по линии 34 в процессор ЭВМ. Сигнал СИП ф ормируется с некоторой задержкой на время считыва ния информации из блока 2.

Сигнал Ввод одновременно поступает на входы блоков 2, -7 и 11, на

шине 29 появляется информация, считывания из блока 2 - КОП-;, В процессор ЭВМ информация с шины 29 запишется с приходом сигнала СИП на линии 34. После ввода в процессор ЭВМ КОП необходимо ввести второе и третье слов команды (данные 1 и 2). После этого процессор выполняет введенную команду. По фронту сигнала СИП происходит сдвиг о на один разряд и сдвиговом регистре 16 и на втором выходе его появляется О, теперь через элемент ИЛИ 10 открыт блок 7. По форнту сигнала регистра 16 содержимое счетчика увеличивается на единицу, т,е, формируется адрес следующей ячейки блока (ПЗУ1 (3), С появлением сигнала Ввод на шине 29 появляется информацияj считанная из регистра 7 - данные 1, С появлением сигнала на линии 34 процессор ЭВМ считывает информацию с шины 29. По фронту сигнала СИП происходит сдвиг О в сдвиговом регистре 16, открывается регистр 11, также по фронту увеличивается на единицу содержимое счетчика 9, Затем с появлением сигнала Ввод также считывается содержимое ПЗУ2 12 (данные 2) через регистр 11, после чего увеличивается на ед,иницу содержимое счетчика 13. Таким образом, из памяти считывается i-я трехсловная команда. После ее выполнения процессор ЭВМ передает по шине 29 адрес следующей ячейки блока (ПЗУ1) 3, в которой хранится (1-(-1)-я однословная команда перехода. После того, как этот адрес выставится на шине 28, процессор ЭВМ также вырабатывает сигналы НК и Бвод которые устанавливают сдвиговый регистр 16 в исходное состояние, появляется сигнал РГ-1 , Затем также считывается содержимое ПЗУ1 3 через блок 2 и шину 29 в процессор ЭВМ. С появлением на .шине 29 .KCПi4 в единичное состояние устанавливается триггер 20 сигналом с, выход ПИЗУ 25, которое синхронизируется сигналом НК. Также по фронту сигнала СЖ1 происходит сдвиг О в

0

5

0

30

S5

сдвиговом регистре 16 и появляется сигнал РГ-2. Но с выработкой сигналов НК и Ввод после выставления адреса ячейки ПЗУ1 3, в которой хранится код сдвиговый регистр 16 уста-, навливается в исходное состояние. Вместе с тем по фронту сигнала НК в единичное состояние устанавливается первый триггер 18 и сигналом с инверсного выхода (Т1) открываются элементы 1-ШИ 17 и 27. С йря- мого выхода триггера 18 1 поступает на вход элемента ИЛИ 24. С появлением сигнала Ввод на выходе элемента ИЛИ 22 появляется сигнал 0 который поступает на вход элемента ШШ, 17, на выходе которого появляется О (ЗП СЧ) . По фронту -( сигнала ЗП СЧ в счетчики 4, 9 и 13 эаписывв ется информация с шины 28 - адрес КОП 1.2.

Сигнал Ввод формирует сигнал СИП в. этом случае через элемент ИЛИ 27, 25 элемент 23 задержки и элемент И 19. Элемент задержки задерживает появление сигнала СИА на время срабатывания блока ПЗУ1 3 (tc4), так как процессор ЭВМ считывает информацию с : шины 29 с приходом сигнала СИП.

По фронту сигнала СИП происходит сдвиг о в сдвиговом регистре 16 и появляется сигнал РГ-2.

С окончанием сигнала НК и Ввод снимается с выхода элемента ИЛИ 17 сигнал ЗП СЧ , и по фронту этого сигнала запускается ждущий мультивибратор 21 , который вырабатывает импульс сброса триггеров 18 и 20.

Работа блока 1 тактируется сигналом НК, но при считывании и:з блока 3 кода команды перехода и её выполнении элемент ИЛИ 14 закрывается сигналом с выхода триггера 20, что блоки Прерыв 35

40

45

50

рует выработку сигнала Формула изобретения

Устройство для сопряжения процессора с памятью, содержащее блок постоянной программируемой памяти, два элемента И, два элемента ШШ и триггер, прямым выходом соединенный с первым входом первого элемента ШШ, отличающееся тем, что, с целью увеличения объема памяти программ, повышения быстродействия ЭВМ и расширения области применения.

в устройство введены блок сравнения, три буферных регистра, три блока постоянной памяти, три счетчика, дешифратор адреса, шесть элементов 1-ШИ сдвиговый регистр, элемент задержки, формирователь импульса и второй триггер, причем выходы первого, второго и тр етьего счетчиков соединены соответственно с адресными входами перво го, второго и третьего блоков постоянной памяти, выходы которых подключены соответственно к информационным входам первого, второго и третьего буферных регистров, выходы которых и адресный вход блока постоянной программируемой памяти образуют вход- выход устройства для подключения к шине данных процессора и памяти, информационные входы дешифратора адреса первого-третьего счетчиков являются входом устройства для подключения к шине адреса процессора и памяти и соединены с первым информационным

Q

5

0

входом устройства для подключения к шине начальной установки процессора и памяти, входы разрешения первого - третьего счетчиков соединены соответственно с первым - третьим выходами регистра сдвига и первыми входами третьего, четвертого и пятого элементов ИЛИ, вторые входы которых соединены с выходом дешифратора адреса и вторым входом первого элемента ШШ, а выходы - соответственно с входами записи первого-третьего буферных регистров, входы считывания которых соединены с первыми входами шестого и седьмого элементов ИЛИ, третьим входом первого элемента ШШ i: входом устройства для подключения к шине режима ввода процессора и памяти, &ЫХОД блока постоянной программируемой памяти соединен с установочным входом второго триггера, выходом соединенного с первым входом восьмого элемента ИЛИ и информационным входом

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1522216A1 |

| Устройство для контроля выполнения программ на эвм | 1986 |

|

SU1383371A1 |

| Устройство для контроля управляющей ЭВМ | 1988 |

|

SU1619280A1 |

| Устройство для сопряжения ведущей и N ведомых цифровых вычислительных машин | 1988 |

|

SU1531104A1 |

| Микропрограммный процессор | 1984 |

|

SU1211746A1 |

| Процессор для обработки массивов данных | 1985 |

|

SU1293737A1 |

| Устройство для временного контроля сигналов интерфейса | 1986 |

|

SU1324028A1 |

| Устройство сопряжения между процессором верхнего уровня и группой процессоров нижнего уровня иерархической мультипроцессорной системы | 1990 |

|

SU1789988A1 |

| Устройство для ввода в ЭВМ стартовой информации | 1988 |

|

SU1569839A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к вычислительной технике и может быть использо вано в системах авточлтпческого управления на базе 3)5. Цель изобретения - увеличение объема памяти программ, повышение быстродеГ-с гвил ЭВМ и расширение области приме ;ения. В. устройство для сопряжения процессора с памятью, содержащее два элемента И, триггер, два элемента ИЛИ и блок постоянной программируемой памяти, пве- дены блок сравнения, ТРИ буферг-гых регистра, три блока пссчогап .сй ти, три счетчика, де11П фратор адреса, шесть элементов КПП, сдгпговы регистр, элемент задержки, фор шрова тель импульса (ждущий мультивибра- тор), триггер. 2 ил., 1 табл, «5

30

входом блока сравнения, вторьм инфор- 25 первого триггера, инверсный выход мационным входом соединенного с вы- которого подключен к второму входу ходом первого счетчика, и выходом шестого элемента ИЛИ и первому входу

.с выходом устройства для подключения к входу прерывания процессора, первый вход первого элемента И соединен с выходом первого элемента ИЛИ, а выход - с синхровходом регистра сдв ига и выходом устройства для подключения к шине синхронизации процессора и памяти, выход второго элемента И сое;динен с входом сброса первого и второго триггеров, а первый вход - через формирователь импульса с выходом :

второго элемента ИЛИ и счетным вхо дом первого - третьего счетчиков,

.входы сброса которых соединены с вторым входом второго элемента И и

35

40

второго элемента ИЛИ, вторым входом соединенного с входом сброса регистра сдвига и выходом седьмого элемента ШШ, вьпкод шестого элемента ИЛИ соединен через элемент задержки с вторым входом первого элемента И, управляющий вход блока сравнения соединен с выходом восьмого элемента ИЛИ, второй вход которого соединен с синхро- входами первого триггера и блока постоянной программируемой памяти, вторым входом седьмого элемента ИЛИ и входом устройства для подключения к выходу сигнала начала команды процессора .

второго элемента ИЛИ, вторым входом соединенного с входом сброса регистра сдвига и выходом седьмого элемента ШШ, вьпкод шестого элемента ИЛИ соединен через элемент задержки с вторым входом первого элемента И, управляющий вход блока сравнения соединен с выходом восьмого элемента ИЛИ, второй вход которого соединен с синхро- входами первого триггера и блока постоянной программируемой памяти, вторым входом седьмого элемента ИЛИ и входом устройства для подключения к выходу сигнала начала команды процессора .

,lJJA2d

5 ill isfc:

C3

| Авторское свидетельство СССР № 1177820, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для адресации памяти микро-ЭВМ | 1980 |

|

SU991427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-11-23—Публикация

1987-03-31—Подача