ел

со

Изобретение птнсзсится к вычислительной технике и может быть использовано для повышения надежности опе- рлтивньп злпоминающих устройств.

Целью изобретения является повьше- ние достоверности контроля оперативно памяти.

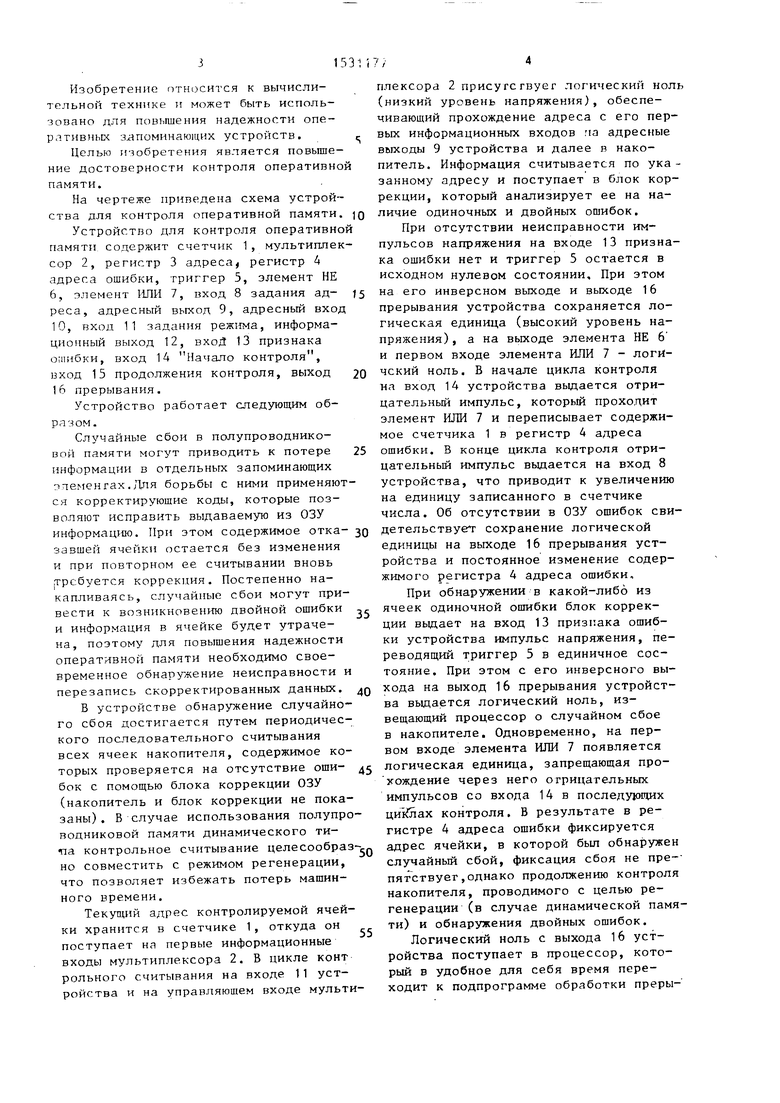

На чертеже приведена схема устройства для контроля оперативной памяти.

Устройство для контроля оперативно памяти содержит счетчик 1, мультиплексор 2, регистр 3 адреса, регистр 4 адреса ошибки, триггер 5, элемент НЕ 6, элемент ИЛИ 7, вход 8 задания ад- реса, адресный выход 9, адресный вход 10, вход 11 задания режима, информационный выход 12, вхоД 13 признака огпибки, вход 14 Начало контроля, вход 15 продолжения контроля, выход 16 прерывания.

Устройство работает следующим образом.

Случайные сбои в полупроводниковой памяти могут приводить к потере информации в отдельных запоминающих элементах.Для борьбы с ними применяются корректирующие коды, которые позволяют исправить выдаваемую из ОЗУ информацию. При этом содержимое отка- завшей ячейки остается без изменения и при повторном ее считывании вновь требуется коррекция. Постепенно накапливаясь, случайные сбои могут привести к возникновению двойной ошибки и информация в ячейке будет утрачена, поэтому для повышения надежности оперативной памяти необходимо своевременное обнаружение неисправности и перезапись скорректированных данных,

В устройстве обнаружение случайного сбоя достигается путем периодического последовательного считывания всех ячеек накопителя, содержимое которых проверяется на отсутствие оши- бок с помощью блока коррекции ОЗУ (накопитель и блок коррекции не показаны) . В случае использования полупроводниковой памяти динамического типа контрольное считывание целесообраз но совместить с режимом регенерации, что позволяет избежать потерь машинного времени.

Текущий адрес контролируемой ячейки хранится в счетчике 1, откуда он поступает на первые информационные входы мультиплексора 2. В цикле конт рольного считывания на входе 11 устройства и на управляющем входе мультиплексора 2 присугсгвуег логический но (низкий уровень напряжения), обеспечивающий прохождение адреса с его первых информационных входов па адресные выходы 9 устройства и далее в накопитель. Информация считывается по ука занному адресу и поступает в блок коррекции, который анализирует ее на наличие одиночных и двойных ошибок.

При отсутствии неисправности импульсов напряжения на входе 13 признака ошибки нет и триггер 5 остается в исходном нулевом состоянии. При этом на его инверсном выходе и выходе 16 прерывания устройства сохраняется логическая единица (высокий уровень напряжения), а на выходе элемента НЕ 6 и первом входе элемента ИЛИ 7 - логИ- чский ноль. В начале цикла контроля на вход 14 устройства выдается отрицательный импульс, который проходит элемент ИЛИ 7 и переписывает содержимое счетчика 1 в регистр 4 адреса ошибки. В конце цикла контроля отрицательный импульс выдается на вход 8 устройства, что приводит к увеличению на единицу записанного в счетчике числа. Об отсутствии в ОЗУ ошибок свидетельствует сохранение логической единицы на выходе 16 прерывания устройства и постоянное изменение содержимого регистра 4 адреса ошибки.

При обнаружении в какой-либо из ячеек одиночной ошибки блок коррекции выдает на вход 13 признака ошибки устройства импульс напряжения, переводящий триггер 5 в единичное состояние. При этом с его инверсного выхода на выход 16 прерывания устройства вьщается логический ноль, извещающий процессор о случайном сбое в накопителе. Одновременно, на первом входе элемента ИЛИ 7 появляется логическая единица, запрещающая про- хождение через него отрицательных импульсов со входа 14 в последу1ощих ци1Й1ах контроля. В результате в регистре 4 адреса ошибки фиксируется адрес ячейки, в которой был обнаружен случайный сбой, фиксация сбоя не препятствуег,однако продолжению контроля накопителя, проводимого с целью регенерации (в случае динамической памяти) и обнаружения двойных ошибок.

Логический ноль с выхода 16 устройства поступает в процессор, который в удобное для себя время переходит к подпрограмме обработки преры515

вания по сбою. При этом он вначале считывает с выхода 12 содержимое регистра 4 адреса ошибки, определяя тпм самым отказавшую ячейку накопителя, затем процессор выполняет ее чтение, выставляя полученное с регистра 4 адреса ошибки число в качестве адреса на вход 10, который записывается в регистр 3 адреса. В циклах записи или чтения при внешних обращениях на входе 11 устройства и на управляющем входе мультиплексора 2 присутствует логическая единица, поэтому на выходы 9 и далее в накопитель проходит адрес с регистра 3 адреса. Блок коррекции производит исправление считанного по данному адресу числа, в результате чего он выдается на ОЗУ без искажений.

В дальнейшем процессор выполняет запись этого числа по тому же самому адресу, что обеспечивает восстановление информации в ячейке, содержимое которой было искажено случайным сбоем

В конце подпрограммы прерывания процессор обнуляет триггер 5 путем подачи отрицательного импульса на вход 15 продолжения контроля 15 устройства после чего на выход 16 может быть выдан новый сигнал прерывания. Если при повторном считывании регистра 4 адреса ошибки оказывается, что в нем записан тот же адрес, то это означает, что данная ячейка вышла из строя и ОЗУ необходимо ремонтировать. Перезапись информации при этом не производится.

Таким образом, предлагаемое устройство не только обеспечивает оперативное обнаружение и устранение случайных сбоев в накрпителе оперативной памяти, но и отделяет их от устойчивы отказов в ячейках, что может быть использовано для статистической оценки вероятности случайных сбоев БИС ОЗУ и выявления наименее надежных микросхем

11776

Учитывая, что для полупроводнши иой в особенности динамической, памяти случайные сбои являются основным и принципиально неустранимым источником ошибок, их своевременное обнаружение и устранение значительно повьппает ее надежность.

10 Формула изобретения

Устройство для контроля оперативной памяти, содержащее счетчик, муль- тиП(Пексор, регистр адреса и регистр адреса ошибки, причем счетный вход счетчика является входом задания адреса устройства, выходы счетчика соединены с первыми информационными вхо- дами мультиплексора, выходы которого являются адресными выходами устройства, вторые информационные входы мультиплексора соединены с выходами регистра адреса, информационные входы ко- торого являются адресными входами устройства, управляющий вход мультиплексора является входом задания режима устройства, выход регистра адреса ошибки является информационным вы- ходом устройства, отличающееся тем, что, с целью повьппения достоверности контроля, в устройство введены триггер, элемент НЕ и элемент ИЛИ, причем вход синхронизации триггера является входом признака ошибки устройства, инверсный выход триггера соединен с входом элемента НЕ и являем . выходом прерывания устройства, вьлод элемента НЕ соединен с первым входом элемента ИЛИ, второй вход которого является входом Начало контроля устройства, выход элемента ИЛИ соединен с входом записи регистра адреса ошибки, информационные входы которого соединены с выходами счетчика, вход сброса триггера является входом продолжения контроля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Устройство для контроля управляющей вычислительной машины | 1987 |

|

SU1464163A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

Изобретение относится к вычислительной технике и может быть использовано в оперативных запоминающих устройствах. Целью изобретения является повышение достоверности контроля оперативной памяти. Устройство содержит счетчик 1, мультиплексор 2, регистр адреса 3, регистр адреса ошибки 4. Введение в устройство триггера 5, элемента НЕ 6 и элемента ИЛИ 7 позволяет не только обнаруживать и исправлять случайные сбои в оперативной памяти, но и разделять ошибки, происшедшие из-за случайных сбоев, и ошибки, вызванные устойчивыми отказами микросхем, с целью их своевременной замены. 1 ил.

| Авторское свидетельство СССР 760194, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1989-12-23—Публикация

1988-02-05—Подача