Изобретение относится к вычисли- тельной технике и может быть использовано при разработке оперативных запоминающих устройств.

Целью изобретения является повышение быстродействия за счет ускоренной выдачи данных, и сигнала Ответ при отсутствии ошибок и улучшение качества проверки, надежности и ремонтопригодности за счет расширения диагностических возможностей.

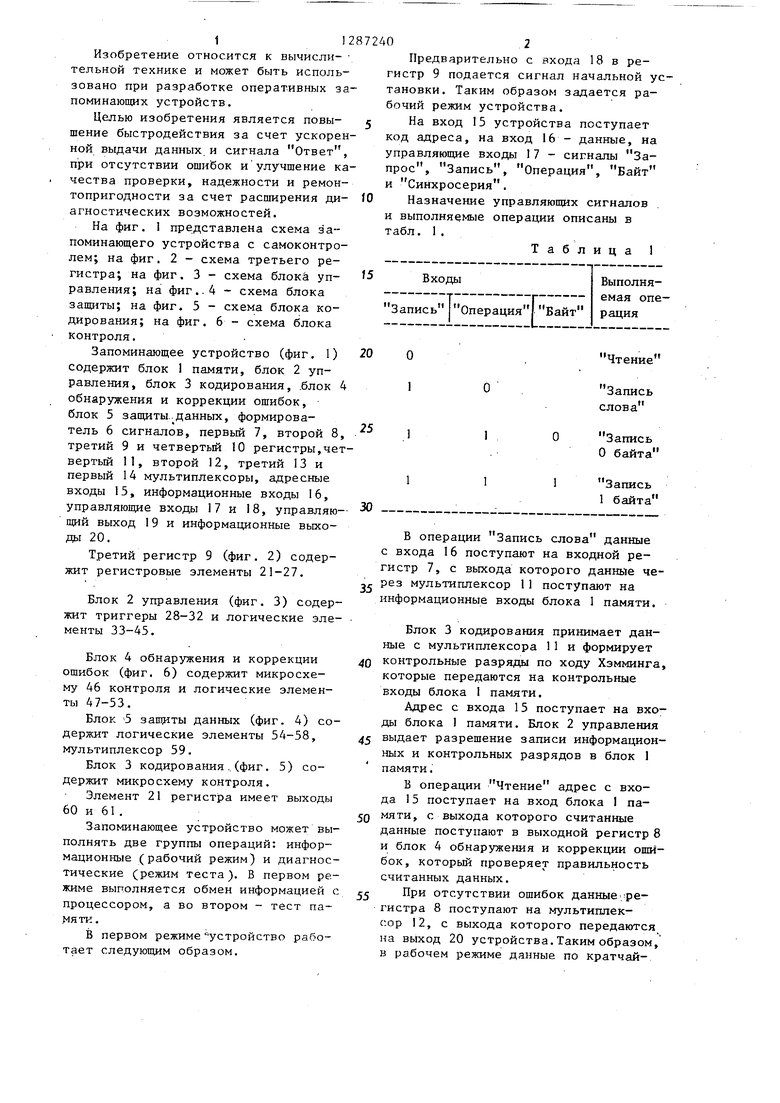

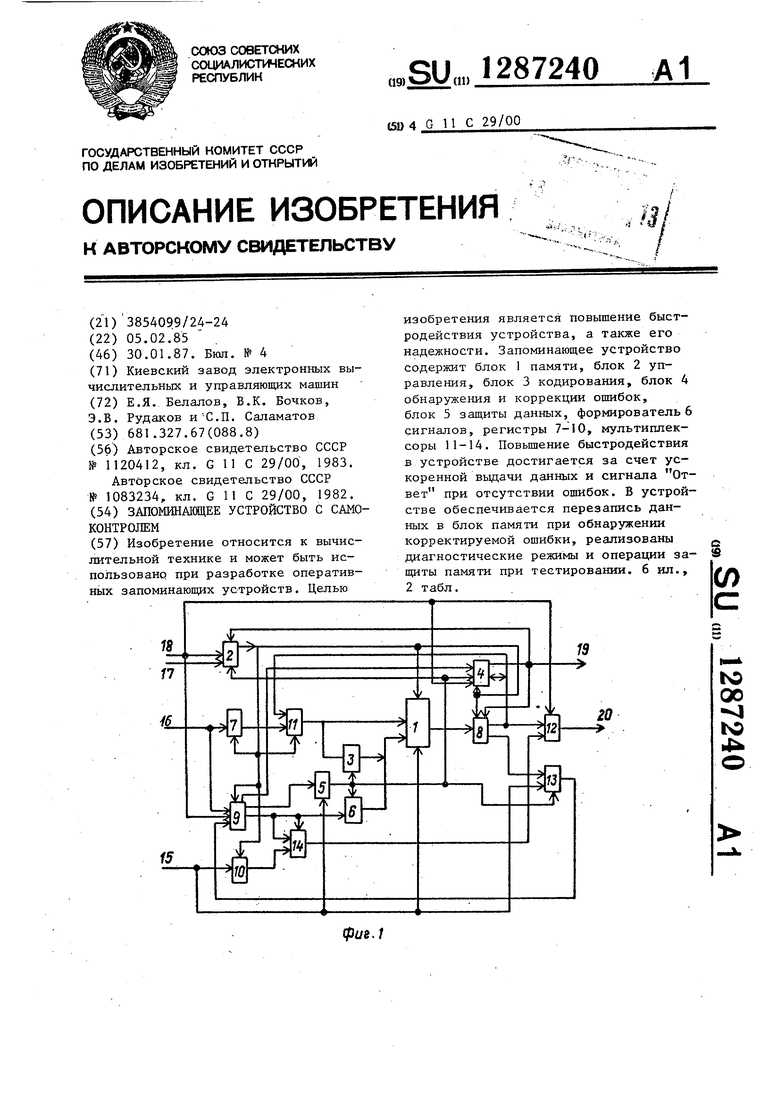

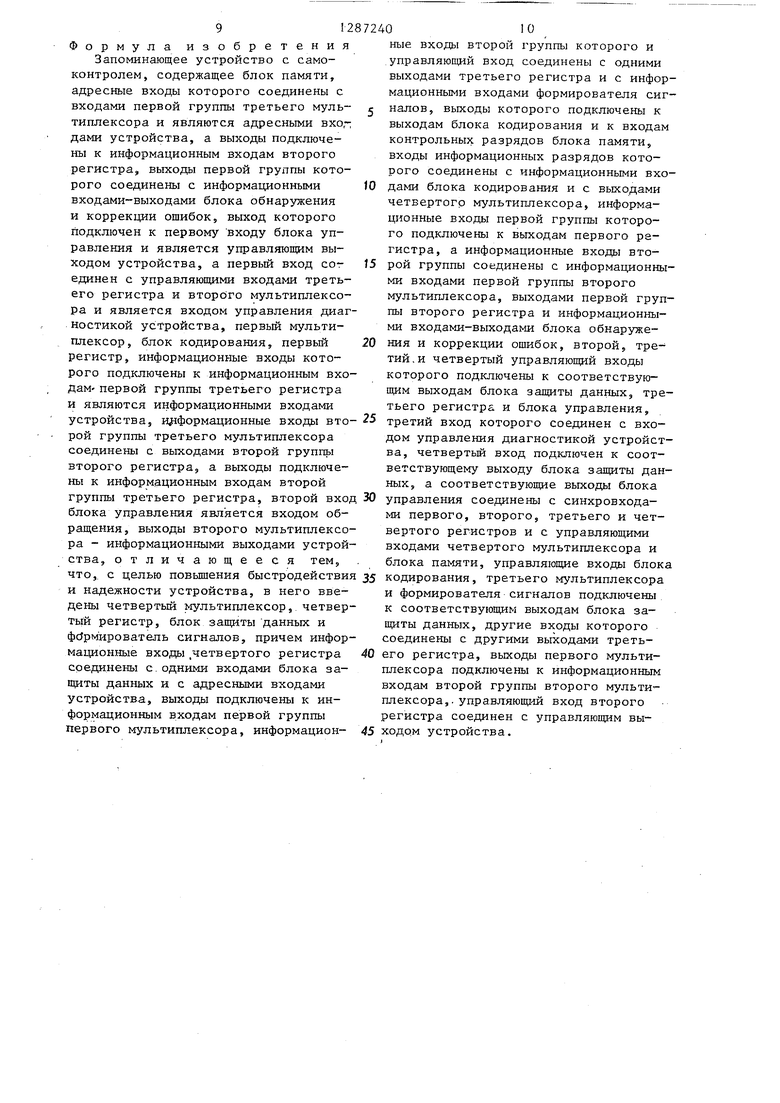

На фиг. I представлена схема запоминающего устройства с самоконтролем; на фиг. 2 - схема третьего регистра; на фиг. 3 - схема блоки управления; на фиг..4 - схема блока защиты; на фиг. 5 - схема блока кодирования; на фиг. 6 - схема блока контроля.

Запоминающее устройство (фиг. 1) содержит блок 1 памяти, блок 2 управления, блок 3 кодирования, .блок 4 обнаружения и коррекции ошибок, блок 5 защиты..данных, формирователь 6 сигналов, первый 7, второй 8 третий 9 и четвертьм 10 регистры,четвертый 11, второй 12, третий 13 и первый 14 мультиплексоры, адресные входы 15, информационные входы I6, управляющие входы 17 и 18, управляющий выход 19 и информационные выходы 20.

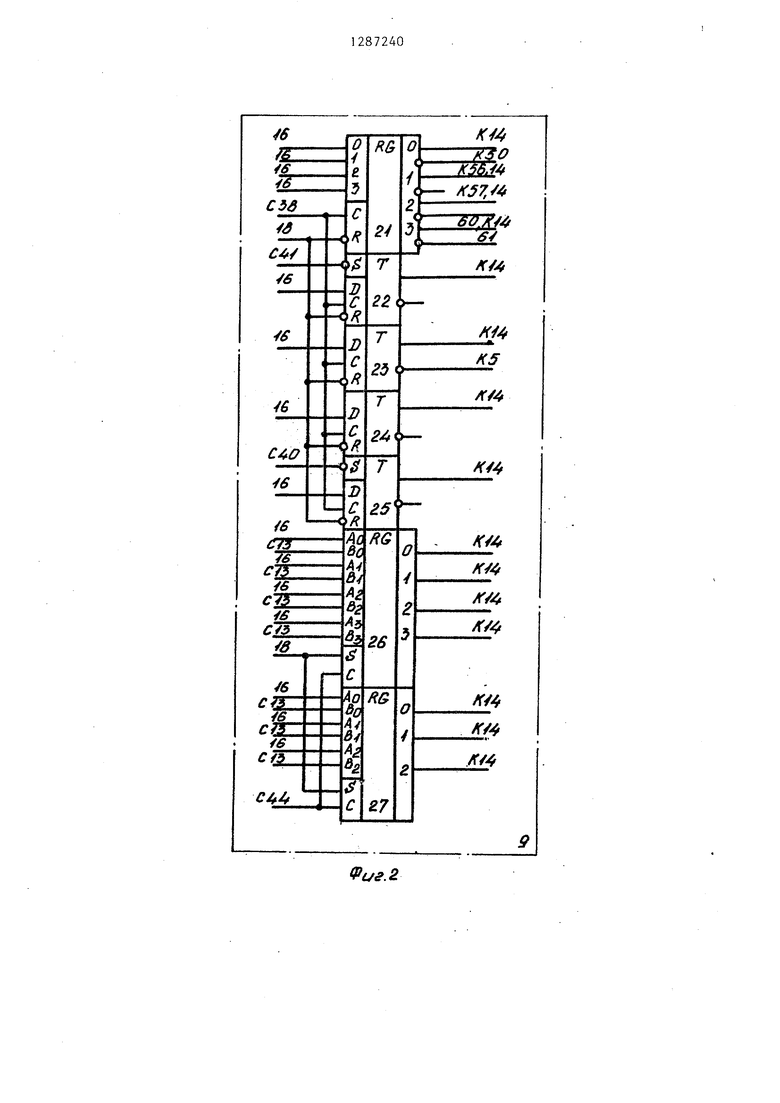

Третий регистр 9 (фиг. 2) содержит регистровые элементы 21-27.

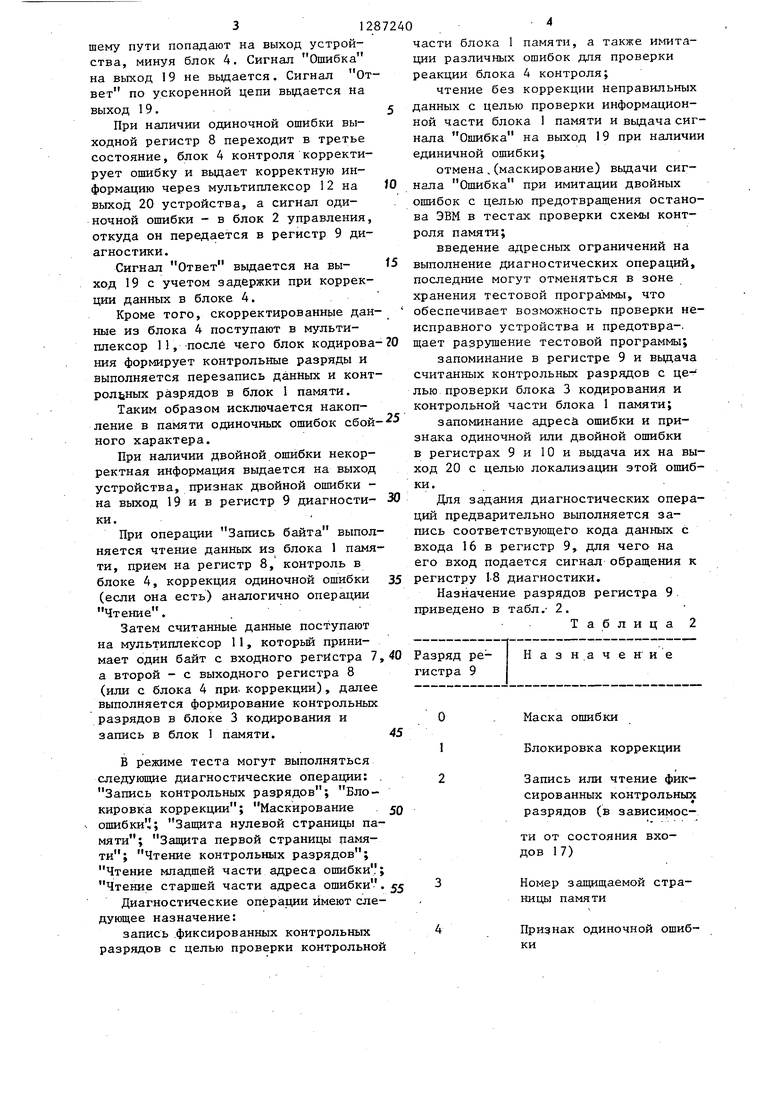

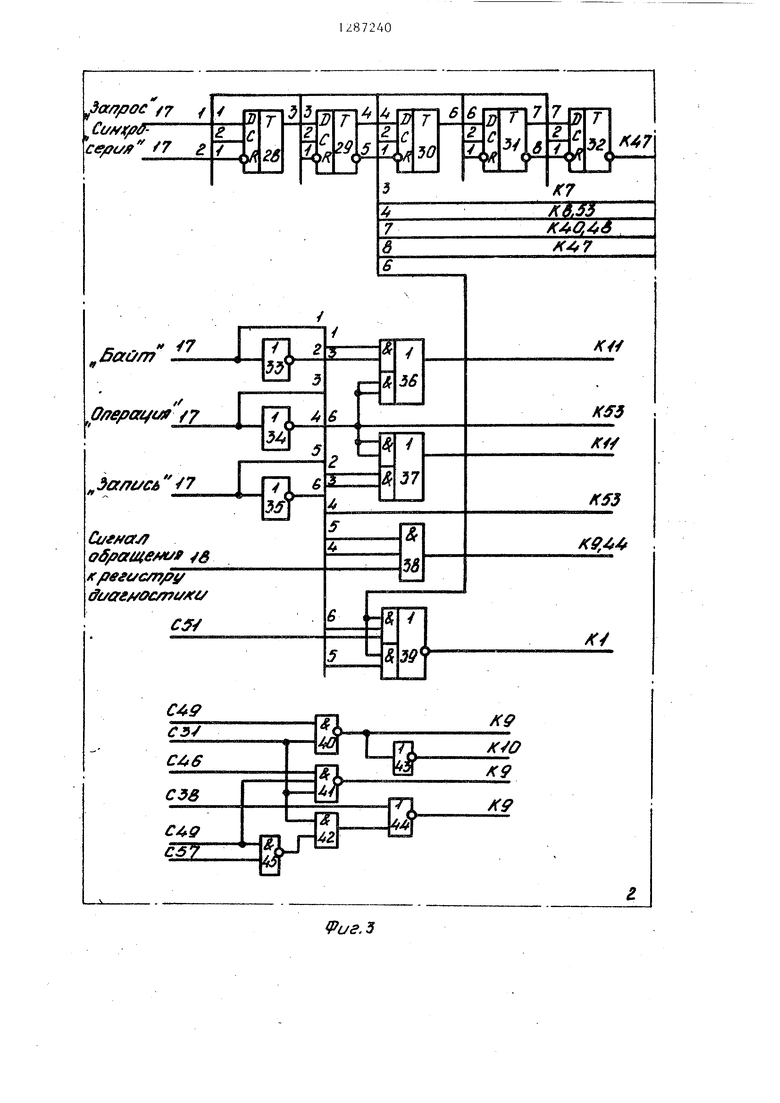

Блок 2 управления (фиг. 3) содержит триггеры 28-32 и логические элементы 33-45.

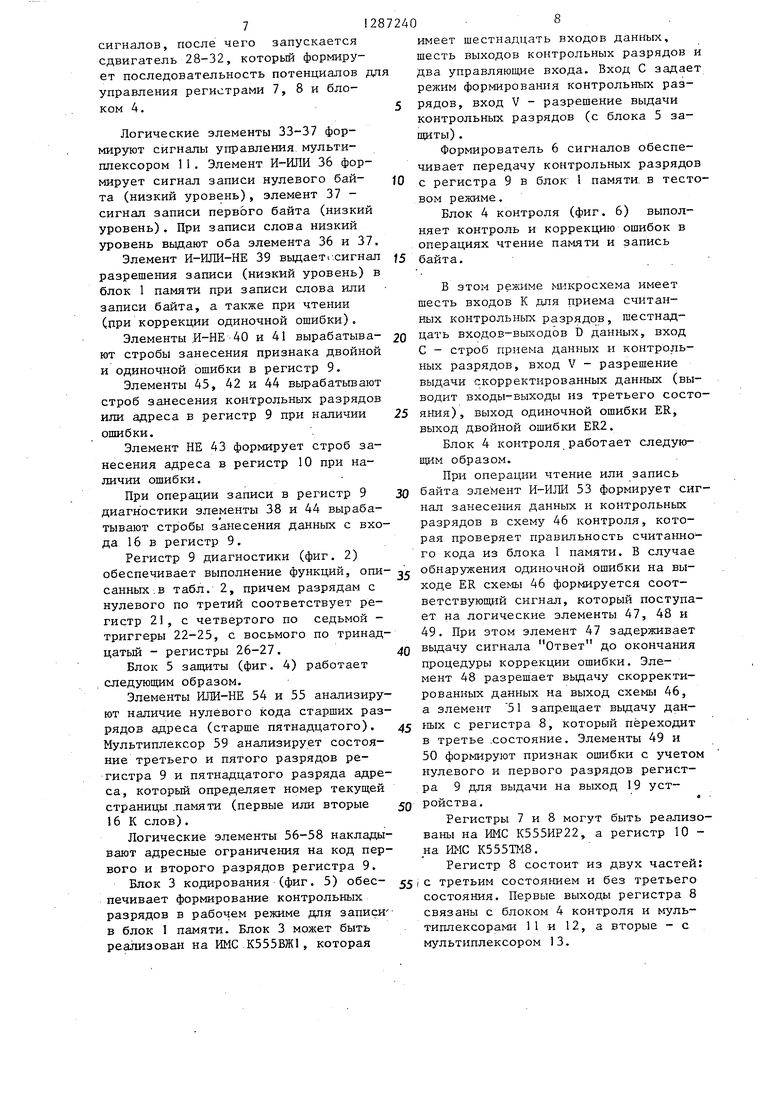

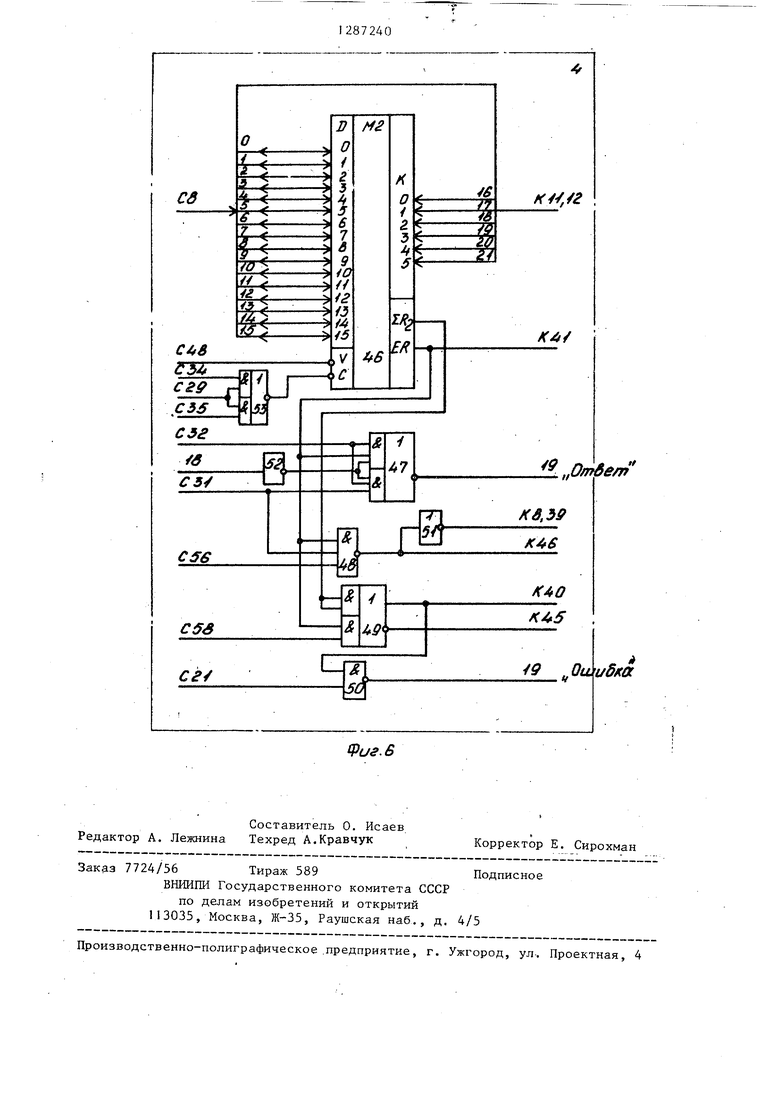

Блок 4 обнаружения и коррекции ошибок (фиг. 6) содержит микросхему 46 контроля и логические элементы 47-53.

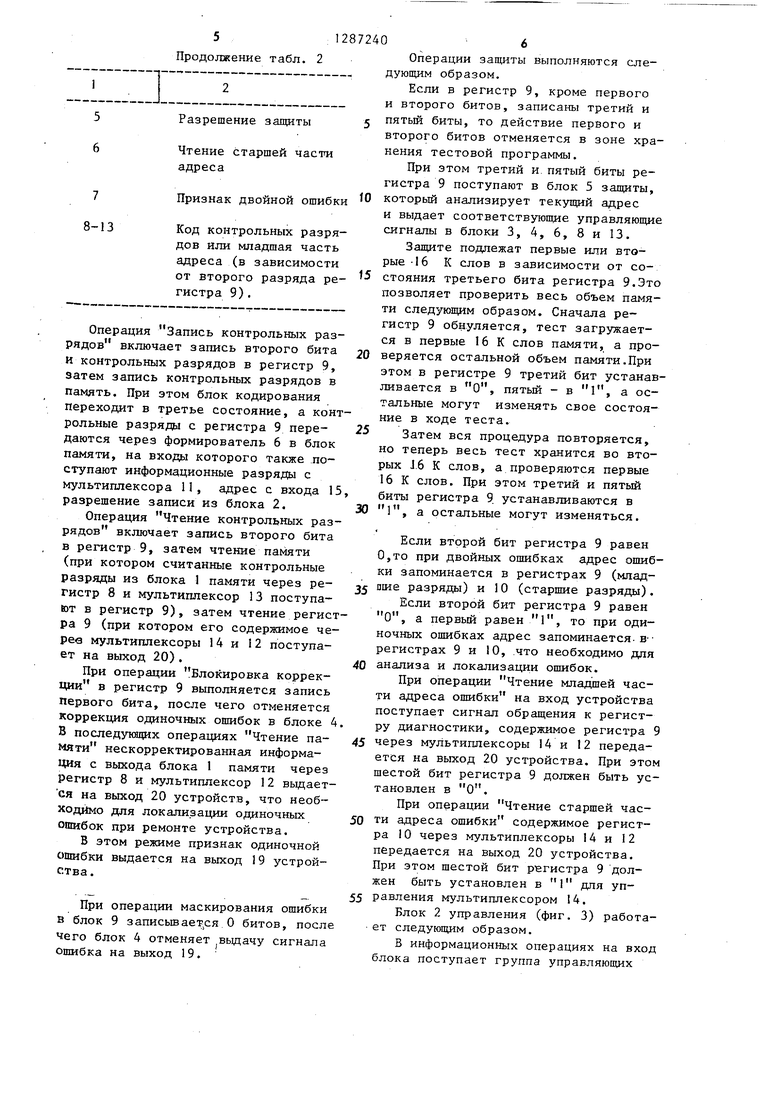

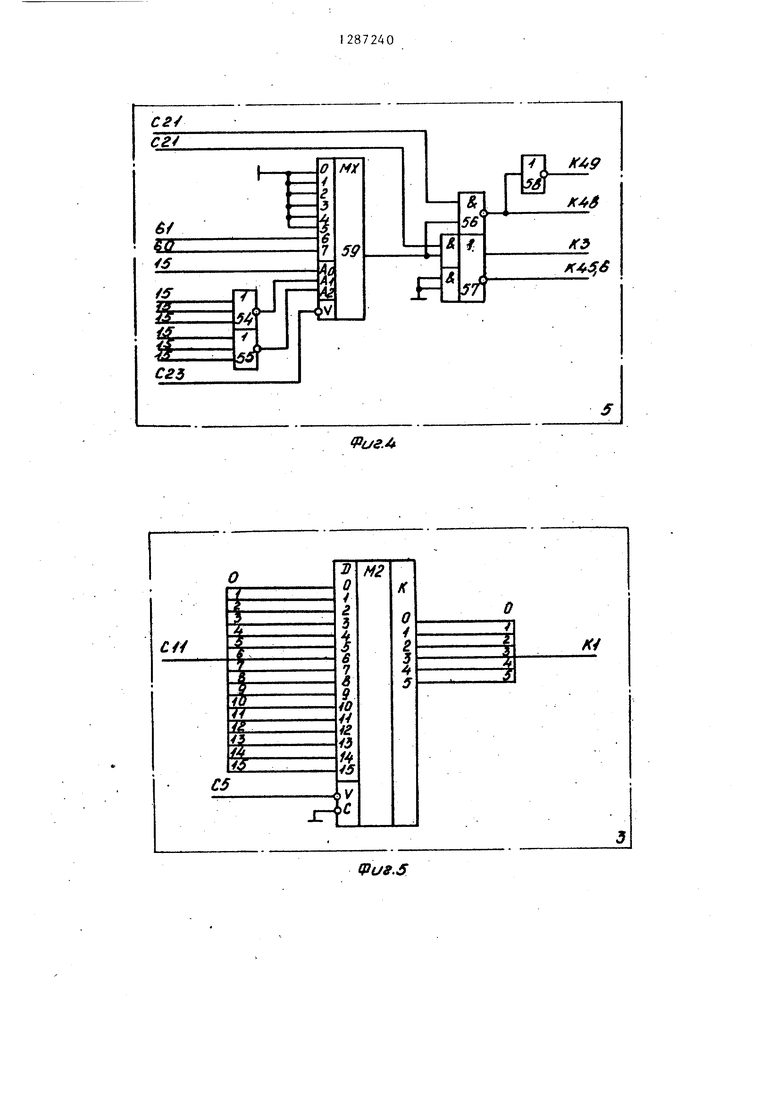

Блок б защиты данных (фиг. 4) содержит логические элементы 54-58, мультиплексор 59,

Блок 3 кодирования , (фиг. 5) содержит микросхему контроля.

Элемент 21 регистра имеет выходы 60 и 61.

Запоминающее устройство может выполнять две группы операций: информационные (рабочий режим) и диагностические (режим теста). В первом режиме выполняется обмен информацией с процессором, а во втором - тест памяти.

В первом режиме устройство работает следующим образом.

Предварительно с входа 18 в регистр 9 подается сигнал начальной установки. Таким образом задается рабочий режим устройства.

На вход 15 устройства поступает код адреса, на вход 16 - данные, на управляющие входы 17 - сигналы Запрос, Запись, Операция, Байт и Синхросерия.

Назначение управляющих сигналов и выполняемые операции описаны в табл. 1.

Таблица 1

20

Чтение

В операции Запись слова данные с входа 16 поступают на входной регистр 7, с выхода которого данные че- рез мультиплексор 11 поступают на информационные входы блока 1 памяти.

Блок 3 кодирования принимает данные с мультиплексора 11 и формирует

контрольные разряды по ходу Хэмминга, которые передаются на контрольные входы блока 1 памяти.

Адрес с входа 15 поступает на входы блока 1 памяти. Блок 2 управления

выдает разрешение записи информационных и контрольных разрядов в блок 1 памяти.

В операции Чтение адрес с входа 15 поступает на вход блока I памяти, с выхода которого считанные данные поступают в выходной регистр 8 и блок 4 обнаружения и коррекции ошибок, который проверяет правильность считанных данных.

При отсутствии ошибок данные--регистра 8 поступают на мультиплексор Г2, с выхода которого передаются на выход 20 устройства. Таким образом, в рабочем режиме данные по кратчайтему пути попадают на выход устройства, минуя блок 4. Сигнал Ошибка на выход 19 не выдается. Сигнал Ответ по ускоренной цепи выдается на выход 19.

При наличии одиночной ошибки выходной регистр 8 переходит в третье состояние, блок 4 контроля корректирует опшбку и вьщает корректную информацию через мультиплексор 12 на выход 20 устройства, а сигнал одиночной ошибки - в блок 2 управления, откуда он передается в регистр 9 диагностики.

Сигнал Ответ выдается на вы- ход 19 с учетом задержки при коррекции данных в блоке 4.

Кроме того, скорректированные дан- ные из блока 4 поступают в мультиплексор 1 Г, после чего блок кодирования формирует контрольные разряды и выполняется перезапись данных и контрольных разрядов в блок 1 памяти.

Таким образом исключается накопление в памяти одиночных ошибок сбойного характера.

При наличии двойной.ошибки некорректная информация выдается на выход устройства, признак двойной ошибки - на выход 19 и в регистр 9 диагности- ки.

При операции Запись байта выполняется чтение данных из блока 1 памяти, прием на регистр 8, контроль в блоке 4, коррекция одиночной ошибки (если она есть) аналогично операции Чтение.

Затем считанные данные поступают на мультиплексор 11, которьй принимает один байт с входного регистра 7 а второй - с выходного регистра 8 (или с блока 4 при. коррекции), далее выполняется формирование контрольных разрядов в блоке 3 кодирования и запись в блок 1 памяти.

В режиме теста могут выполняться следующие диагностические операции: Запись контрольных разрядов ; Блокировка коррекции ; Маскирование . ошибки ; Защита нулевой страницы памяти ; Защита первой страницы памяти ; Чтение контрольнь:х разрядов ; Чтение младшей части адреса ошибки ; Чтение старшей части адреса ошибки

Диагностические операции имеют следующее назначение:

запись .фиксированных контрольных разрядов с целью проверки контрольной

части блока 1 памяти, а также имитации различных ошибок для проверки реакции блока 4 контроля;

чтение без коррекции неправильных данных с целью проверки информационной части блока 1 памяти и выдача сигнала Ошибка на выход 19 при наличи единичной ошибки;

отмена , (маскирование) вьщачи сигнала Ошибка при имитации двойных ошибок с целью предотвращения останова ЭВМ в тестах проверки схемы контроля памяти;

введение адресных ограничений на выполнение диагностических операций, последние могут отменяться в зоне хранения тестовой програ ммы, что обеспечивает возможность проверки неисправного устройства и предотвра-. щает разрушение тестовой программы;

запоминание в регистре 9 и выдача считанных контрольных разрядов с це- лью проверки блока 3 кодирования и контрольной части блока 1 памяти;

запоминание адреса ошибки и признака одиночной или двойной ошибки в регистрах 9 и 10 и вьщача их на выход 20 с целью локализации этой ошибки.

Для задания диагностических операций предварительно вьшолняется запись соответствующего кода данных с входа 16 в регистр 9, для чего на его вход подается сигнал обращения к регистру 1-8 диагностики.

Назначение разрядов регистра 9. приведено в табл.- 2.

Таблица 2

Маска ошибки Блокировка коррекции

Запись или чтение фиксированных контрольных разрядов (в зависимости от состояния входов 17)

Номер защищаемой страницы памя ти

Признак одиночной ошибки

адреса

3-13

Признак двойной ошибки

Код контрольных разрядов или младшая часть адреса (в зависимости от второго разряда регистра 9) .

Операция Запись контрольных разрядов включает запись второго бита и контрольных разрядов в регистр 9, затем запись контрольных разрядов в память. При этом блок кодирования переходит в третье состояние, а контрольные разряды с регистра 9 передаются через формирователь 6 в блок памяти, на входы которого также поступают информационные разряды с мультиплексора 11, адрес с входа 15, разрешение записи из блока 2.

Операция Чтение контрольных разрядов включает запись второго бита в регистр 9, затем чтение памяти (при котором считанные контрольные разряды из блока 1 памяти через регистр 8 и мультиплексор 13 поступают в регистр 9), затем чтение регистра 9 (при котором его содержимое черев мультиплексоры 14 и 12 поступает на выход 20).

При операции Блокировка коррекции в регистр 9 выполняется запись Первого бита, после чего отменяется коррекция одиночных ошибок в блоке 4. В последукндих операциях Чтение памяти нескорректированная информация с выхода блока 1 памяти через регистр 8 и мультиплексор 12 вьщает- ся на выход 20 устройств, что необходимо для локализации одиночных ошибок при ремонте устройства.

В этом режиме признак одиночной ошибки выдается на выход 19 устройства .

При операции маскирования ошибки в блок 9 записьшается О битов, после чего блок 4 отменяет вьщачу сигнала Ошибка на выход 19.

287240 6

Операции защиты выполняются следующим образом.

Если в регистр 9, кроме первого и второго битов, записаны третий и пятьй биты, то действие первого и второго битов отменяется в зоне хранения тестовой программы.

При этом третий и. пятый биты регистра 9 поступают в блок 5 защиты, который анализирует текущий адрес и выдает соответствующие управляющие сигналы в блоки 3, 4, 6, 8 и 13.

Защите подлежат первые или вторые -16 К слов в зависимости от состояния третьего бита регистра 9.Это позволяет проверить весь объем памяти следующим образом. Сначала регистр 9 обнуляется, тест загружается в первые 16 К слов памяти, а проверяется остальной объем памяти.При этом в регистре 9 третий бит устанавливается в О, пятый - в I, а остальные могут изменять свое состояние в ходе теста.

Затем вся процедура повторяется, но теперь весь тест хранится во вторых J.6 К слов, а проверяются первые 16 К слов. При этом третий и пятый биты регистра 9. устанавливаются в 1, а остальные могут изменяться.

15

20

25

30

Если второй бит регистра 9 равен О,то при двойных ошибках адрес ошибки запоминается в регистрах 9 (млад- 35 П1ие разряды) и 10 (старшие разряды). Если второй бит регистра 9 равен О, а первый равен 1, то при одиночных ошибках адрес запоминается-В регистрах 9 и 10, .что необходимо для 40 анализа и локализации ошибок.

При операции Чтение младшей части адреса ошибки на вход устройства поступает сигнал обращения к регистру диагностики, содержимое регистра 9 45 через мультиплексоры 14 и 12 передается на выход 20 устройства. При этом шестой бит регистра 9 должен быть установлен в О.

При операции Чтение старшей час- 50 ти адреса ошибки содержимое регистра 10 через мультиплексоры 14 и 12 передается на выход 20 устройства. При этом шестой бит рвгистра 9 должен быть установлен в 1 для уп- 55 равления мультиплексором 14.

Блок 2 управления (фиг. 3) работа- ет следующим образом.

В информационных операциях на вход блока поступает группа управляющих

Если второй бит регистра 9 равен О,то при двойных ошибках адрес ошибки запоминается в регистрах 9 (млад- П1ие разряды) и 10 (старшие разряды). Если второй бит регистра 9 равен О, а первый равен 1, то при одиночных ошибках адрес запоминается-В регистрах 9 и 10, .что необходимо для анализа и локализации ошибок.

При операции Чтение младшей части адреса ошибки на вход устройства поступает сигнал обращения к регистру диагностики, содержимое регистра 9 через мультиплексоры 14 и 12 передается на выход 20 устройства. При этом шестой бит регистра 9 должен быть установлен в О.

При операции Чтение старшей час- ти адреса ошибки содержимое регистра 10 через мультиплексоры 14 и 12 передается на выход 20 устройства. При этом шестой бит рвгистра 9 должен быть установлен в 1 для уп- равления мультиплексором 14.

Блок 2 управления (фиг. 3) работа- ет следующим образом.

В информационных операциях на вход блока поступает группа управляющих

712

сигналов, после чего запускается сдвигатель 28-32, который формирует последовательность потенциалов дл управления регистрами 7, 8 и блоком 4.

Логические элементы 33-37 формируют сигналы управления мультиплексором 11. Элемент И-ИЛИ 36 формирует сигнал записи нулевого бай- та (низкий уровень), элемент 37 - сигнал записи первого байта (низкий уровень). При записи слова низкий уровень выдают оба элемента 36 и 37.

Элемент И-ИЛИ-НЕ 39 выдает с-сигнал разрешения записи (низкий уровень) в блок 1 памяти при записи слова или записи байта, а также при чтении (при коррекции одиночной ошибки).

Элементы .И-НЕ 40 и 41 вырабатыва- ют стробы занесения признака двойной и одиночной ошибки в регистр 9.

Элементы 45, 42 и 44 вырабатывают строб занесения контрольных разрядов или адреса в регистр 9 при наличии ошибки.

Элемент НЕ 43 формирует строб занесения адреса в регистр 10 при наличии ошибки.

При операции записи в регистр 9 диагностики элементы 38 и 44 вырабатывают стробы занесения данных с входа 16 в регистр 9.

Регистр 9 диагностики (фиг. 2)

40

обеспечивает выполнение функций, опи- or обнаружения одиночной ошибки на выходе ER схемы 46 формируется соответствующий сигнал, который поступает на логические элементы 47, 48 и 49. При этом элемент 47 задерживает выдачу сигнала Ответ до окончания процедуры коррекции ошибки. Элемент 48 разрешает вьщачу скорректированных данных на выход схемы 46, а элемент 51 запр.ещает выдачу данных с регистра 8, который переходит в третье .состояние. Элементы 49 и 50 формируют признак ошибки с учетом нулевого и первого разрядов регистра 9 для выдачи на выход 19 уст- страницы .памяти (первые или вторые п ройства. 16 К слов).

Логические элементы 56-58 накладывают адресные ограничения на код первого и второго разрядов регистра 9.

Блок 3 кодирования (фиг. 5) обеспечивает формирование контрольных

санных.в табл. 2, причем разрядам с нулевого по третий соответствует регистр 21, с четвертого по седьмой - триггеры 22-25, с восьмого по тринад- цатьш - регистры 26-27.

Блок 5 защиты (фиг. 4) работает следующим образом.

Элементы ИЖ-НЕ 54 и 55 анализируют наличие нулевого кода старших разрядов адреса (старше пятнадцатого). Мультиплексор 59 анализирует состояние третьего и пятого разрядов регистра 9 и пятнадцатого разряда адреса, который определяет номер текущей

45

50

Регистры 7 и 8 могут быть реализованы на ИМС К555ИР22, а регистр 10 - на ИМС К555ТМ8.

Регистр 8 состоит из двух частей: 55I с третьим состоявшем и без третьего состояния. Первые выходы регистра 8

разрядов в рабочем режиме для записи в блок 1 памяти. Блок 3 может быть реализован на ИМС К555ВЖ1, которая

имеет шестнадцать входов данных, шесть выходов контрольных разрядов и два yпpaвляюш e входа. Вход С задает режим формирования контрольных разрядов, вход V - разрешение выдачи контрольных разрядов (с блока 5 за- шдты).

Формирователь 6 сигналов обеспечивает передачу контрольных разрядов с регистра 9 в блок 1 памяти, в тестовом режиме.

Блок 4 контроля (фиг. 6) выполняет контроль и коррекцию ошибок в операциях чтение памяти и запись байта.

В этом режиме м1- кросхема имеет шесть входов К для приема считанных контрольных разрядов, шестнадцать входов-выходов D данных, вход С - строб приема данных и контрольных разрядов, вход V - разрешение выдачи скорректированных данных (выводит входы-выходы из третьего состояния) , выход одиночной ошибки ER, выход двойной ошибки ER2.

Блок 4 контроля работает следующим образом.

При операции чтение или запись байта элемент И-ИЛИ 53 формирует сигнал занесезтя данных и контрольных разрядов в схему 46 контроля, которая проверяет правильность считанного кода из блока 1 памяти. В случае

40

or п

or п

45

or обнаружения одиночной ошибки на выходе ER схемы 46 формируется соответствующий сигнал, который поступает на логические элементы 47, 48 и 49. При этом элемент 47 задерживает выдачу сигнала Ответ до окончания процедуры коррекции ошибки. Элемент 48 разрешает вьщачу скорректированных данных на выход схемы 46, а элемент 51 запр.ещает выдачу данных с регистра 8, который переходит в третье .состояние. Элементы 49 и 50 формируют признак ошибки с учетом нулевого и первого разрядов регистра 9 для выдачи на выход 19 уст- п ройства.

0

Регистры 7 и 8 могут быть реализованы на ИМС К555ИР22, а регистр 10 - на ИМС К555ТМ8.

Регистр 8 состоит из двух частей: 5I с третьим состоявшем и без третьего состояния. Первые выходы регистра 8

связаны с блоком 4 контроля и мультиплексорами 11 и 12, а вторые - с мультиплексором 13.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее блок памяти, адресные входы которого соединены с входами первой группы третьего муль- типлексора и являются адресньши входами устройства, а выходы подключены к информационным входам второго регистра, выходы первой группы которого соединены с информационными входами-выходами блока обнаружения и коррекции ошибок, выход которого подключен к первому входу блока управления и является управляющим выходом устройства, а первый вход cor единен с управляющими входами третьего регистра и второго мультиплексора и является входом управления диагностикой устройства, первый мультиплексор, блок кодирования, первый регистр, информационные входы которого подключены к информационным входам- первой группы третьего регистра и являются информационными входами устройства, информационные входы вто рой группы третьего мультиплексора соединены с выходами второй группь второго регистра, а выходы подключены к информационным входам второй

группы третьего регистра, второй вход 30 управления соединены с синхровхода-

ми первого, второго, третьего и четвертого регистров и с управляющими входами четвертого мультиплексора и блока памяти, управляющие входы блока

блока управления является входом обращения, выходы второго мультиплексора - информационными выходами устройства, отличающееся тем.

что, с целью повышения быстродействия 35 кодирования, третьего мультиплексора

и надежности устройства, в него введены четвертьй мультиплексор, четвертый регистр, блок защиты данных и формирователь сигналов, причем информационные входы /четвертого регистра соединены с.одними входами блока защиты данных и с адресными входами устройства, выходы подключены к информационным входам первой группы

первого мультиплексора, информацион- 45 ходом устройства.

ные входы второй группы которого и .управляющий вход соединены с одними выходами третьего регистра и с информационными входами формирователя сигналов, выходы которого подключены к выходам блока кодирования и к входам контрольных разрядов блока памяти, входы информационных разрядов которого соединены с информационньши входами блока кодирования и с выходами четвертого мультиплексора, информационные входы первой группы которого подключены к выходам первого регистра, а информационные входы второй группы соединены с информационными входами первой группы второго мультиплексора, выходами первой группы второго регистра и информационными входами-выходами блока обнаружения и коррекции ошибок, второй, третий, и четвертый управляющий входы которого подключены к соответствующим выходам блока защиты данных, третьего регистра и блока управления, третий вход которого соединен с входом управления диагностикой устройства, четвертьй вход подключен к соответствующему выходу блока защиты данных, а соответствующие выходы блока

и формирователя сигналов подключены к соответствующим выходам блока защиты данных, другие входы которого соединены с другими выходами третьего регистра, выходы первого мультиплексора подключены к информационным входам второй группы второго мультиплексора,, управляющий вход второго регистра соединен с управляющим вы(Риг.

IPU8,3

ФиеЛ

Фиг.5

сг

&

56

(иг.6

Редактор А. Лежнина

Составитель О. Исаев Техред А.Кравчук

Заказ 7724/56 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое .предприятие, г. Ужгород, ул-. Про1ктная Т

1..0тбет

II

9 Ot t/дла

Корректор Е. Сирсхман

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство | 1987 |

|

SU1481865A1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1649614A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1092569A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке оперативных запоминающих устройств. Целью изобретения является повышение быстродействия устройства, а также его надежности. Запоминающее устройство содержит блок 1 памяти, блок 2 управления, блок 3 кодирования, блок 4 обнаружения и коррекции ошибок, блок 5 защиты данных, формирователь 6 сигналов, регистры 7-10, мультиплексоры 11-14. 11овьш1ение быстродействия в устройстве достигается за счет ускоренной выдачи данных и сигнала Ответ при отсутствии ошибок. В устройстве обеспечивается перезапись данных в блок памяти при обнаружении корректируемой ошибки, реализованы диагностические режимы и операции защиты памяти при тестировании. 6 ил., 2 табл. . с S (Л 18 to 00 ГС 4 фие.1

| Запоминающее устройство с контролем | 1983 |

|

SU1120412A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для тестового контроля памяти | 1982 |

|

SU1083234A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-30—Публикация

1985-02-05—Подача