| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1987 |

|

SU1529284A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

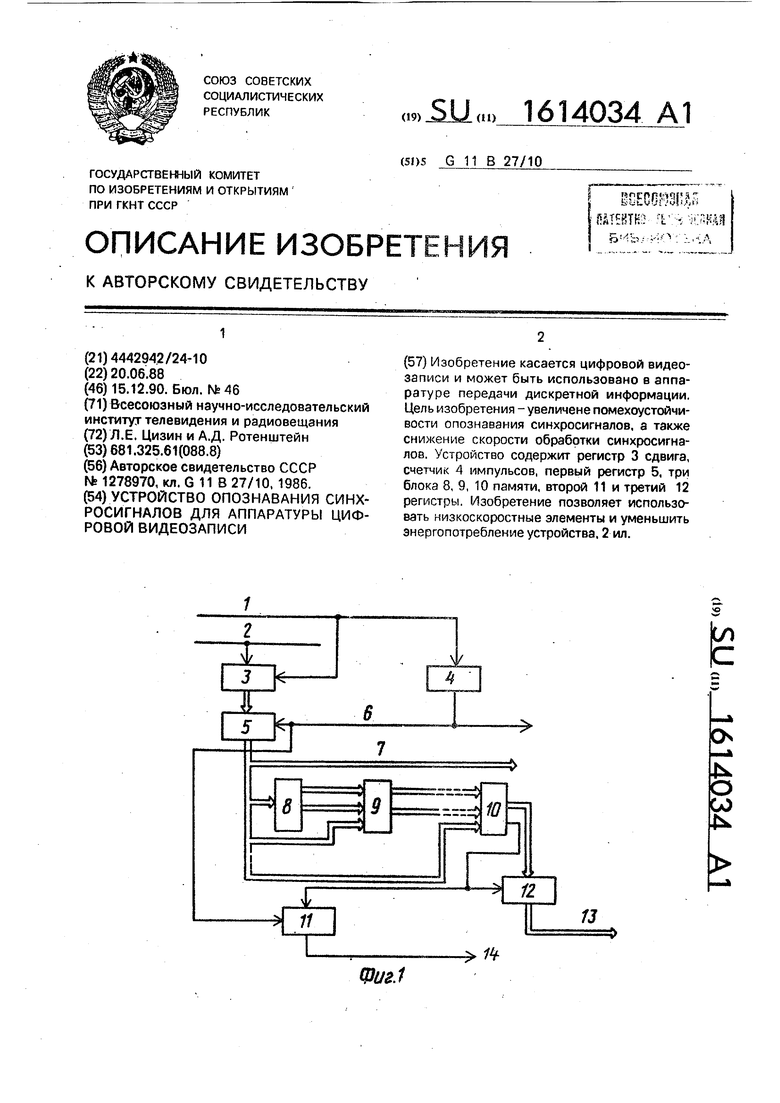

Изобретение касается цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации. Цель изобретения - увеличение помехоустойчивости опознавания синхросигналов, а также снижение скорости обработки синхросигналов. Устройство содержит регистр 3 сдвига, счетчик 4 импульсов, первый регистр 5, три блока 8, 9, 10 памяти второй 11 и третий 12 регистры. Изобретение позволяет использовать низкоскоростные элементы и уменьшить энергопотребление устройства. 2 ил.

о

5 о

со

li

Фиг.1

Изобретение касается цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации.

Цель изобретения - увеличение помехоустойчивости опознавания синхросигналов, а также снижение скорости обработки синхросигналов, позволяющее использовать низкоскоростные элементы и уменьшить энергопотребление устройства,

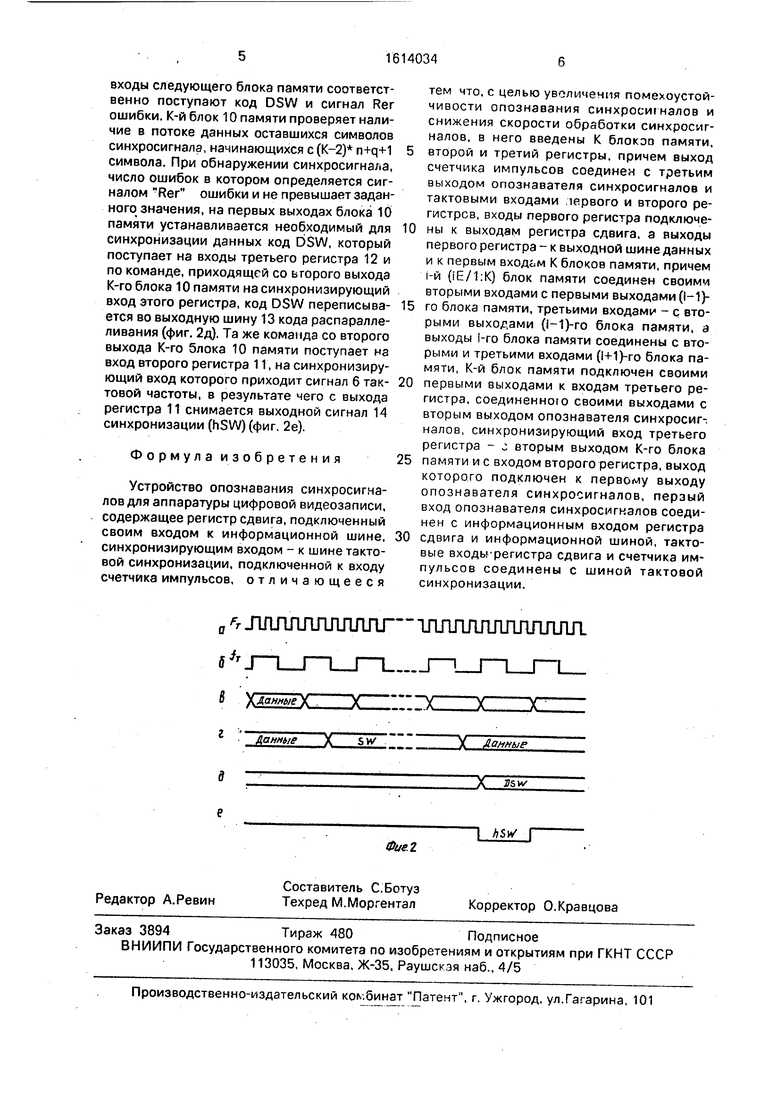

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - диаграммы сигналов, поясняющие работу устройства.

Устройство содержит шину 1 тактовой синхронизации, информационную шину 2, регистр 3 сдвига, счетчик 4 импульсов, первый регистр 5, сигнал 6 тактовой частоты, выходную шину 7 данных, первый блок 8 памяти, второй блок 9 памяти, К-й блок 10 памяти, второй регистр 11, третий регистр 12, выходную шину 13 кода распараллеливания и выходной сигнал 14 синхронизации.

Регистр 3 сдвига подключен своим ахо- дом к информационной шине 2, а синхронизирующим входом - к шине 1 тактовой синхронизации, подключенной к входу счетчика 4 импульсов, соединенного своим выходом с выходом сигнала б тактовой частоты, подключенным к синхронизирующему входу второго регистра 11 и к синхронизирующему входу первого регистра 5, подключенного своими входами к выходам регистра 3 сдвига, а своими выходами - к выходной шине 7 данных, к входам первого блока 8 памяти, к первым входам всех, кроме первого, блоков памяти, причем второй блок 9 памяти соединен своими вторыми входами с первыми выходами первого блока 8 памяти, третьими входами - с вторыми выходами первого блока 8 памяти, первыми входами - с вторыми входами третьего блока памяти, вторыми выходами - с третьими входами третьего блока памяти, который соединен своими первыми и вторыми выходами соответственно ей вторыми и третьими входами следующего по порядковому номеру блока памяти, причем (К-1)-й блок памяти соединен своими вторыми входами с первыми выходами (К-2)-го блока памяти, третьими входами со вторыми выходами (К-2)-го блока памяти, своими первыми выходами со вторыми входами К-го блока 10 памяти, вторыми выходами с третьими входами К-го блока 10 памяти, подключенного своими первыми выходами к входам третьего реги- evpa 12, соединенного своими выходами с выходг-:ой шмной 13 кода распараллеливания, а синхронизирующим входом - с вторым выходом третьего блока 10 памяти и с входом второго регистра 11, с выхода которого снимается выходной сигнал 14 синхронизации.

Устройство работает следующим образом.

На регистр 3 сдвига воспроизводимые

данные поступают по информационной шине 2, а импульсы воспроизводимой тактовой частоты FT - по шине 1 тактовой синхронизации (фиг. 2а). Счетчик 4 импульсов формИ0 рует сигнал 6 тактовой частоты fi (фиг. 26) делением частоты FT на п, где п - число символов в словах воспроизводимых данных, который поступает на синхронизирующие входы первого регистра 5 и второго

5 регистра 11. На перво( регистре 5 осуществляется перетактировй ние распараллельных входнь х данных тактовой частотой (фиг. 2в), которые поступают в выходную шину 7 данных и на первые входы всех блоков памяти

0 8, 9 и 10, общее число которых при обнаружении синхросигналов длиной m символов определяется как ((n). Каждый блок памяти проверяет наличие своего п- символьного сегмента синхросигнала в по5 токе данных, определяет расположение первого символа сегмента в п-битном слове данных (код DSW распараллеливания) и формирует значение DSW При наличии в потоке данных синхроинформации SW (фиг. 2г) пер0 вый блок 8 памяти фиксирует первые q символов синхросигнала (где q п в связи с произвольностью распараллеливания входных данных) и на своих первых выходах устанавливает код DSW распараллеливания,

5 который определкэтся значением n-q и поступает на вторые входы второго блока 9 памяти, на третьи входы которого со вторых выходов первого блока 8 памяти приходит сигнал Rer наличия и количества ошибок,

0 используемый для обнаружения синхросигнала, символы которого поражены ошибками. На следующий такт сигнала 6 тактовой частоты второй блок 9 памяти анализирует п-символьный сегмент синхросигнала, на5 чинающийся с q+1 символа, и производит необходимую коррекцию DSW, значение которого устанавливается на первых выходах блока 9 памяти и поступает на вторые входы следующего блока памяти, на третьи

0 входы которого со вторых выходов второго блока 9 памяти приходит сигнал Rer ошибки, в результате чего i-й блок памяти /1 i К/ определяет наличие сегмента синхросигнала, начинающегося с (i-2)ri4-q+1 символа синх5 ронизации, причем на его вторые входы.поступает код DSW с первых выходов предыдущего блока памяти, а на его третьи входы - сигнал/ Rer ошибки со вторых выходов предыдущего блока памяти, с его первых и вторых выходов на вторые и третьи

входы следующего блока памяти соответственно поступают код DSW и сигнал Rer ошибки. К-й блок 10 памяти проверяет наличие в потоке данных оставшихся символов синхросигнала, начинающихся с (К-2) n+q+1 символа. При обнаружении синхросигнала, число oujvsboK в котором определяется сигналом Rer ошибки и не превышает заданного значения, на первых выходах блока 10 памяти устанавливается необходимый для синхронизации данных код DSW, который поступает на входы третьего регистра 12 и по команде, приходящей со ьгорого выхода К-го блока 10 памяти на синхронизирующий вход этого регистра, код DSW переписыва- ется во выходную шину 13 кода распараллеливания (фиг. 2д). Та же команда со второго выхода К-го блока 10 памяти поступает на вход второго регистра 11, на синхронизирующий вход которого приходит сигнал б так- товой частоты, в результате чего с выхода регистра 11 снимается выходной сигнал 14 синхронизации (hSW) (фиг. 2е).

Формула изобретения

Устройство опознавания синхросигналов для аппаратуры цифровой видеозаписи, содержащее регистр сдвига, подключенный своим входом к информационной шине, синхронизирующим входом - к шине тактовой синхронизации, подключенной к входу счетчика импульсов, отличающееся

р гЛялллплллги-тплллллллллл.

Аанные X SW

тем что, с целью уволиченмя помехоустойчивости опознавания синхросигналов и снижения скорости обработки синхросигналов, в него введены К блоков памяти, второй и третий регистры, причем выход счетчика импульсов соединен с третьим выходом опознавателя синхросигналов и тактовыми входами первого и второго регистров, входы первого регистра подключены к выходам регистра сдвига, а выходы первого регистра - к выходной шине данных и к первым входам К блоков памяти, причем 1-й (iE/1:K) блок памяти соединен своими вторыми входами с первыми выходами (1-1)- го блока памяти, третьими входами - с вторыми выходами (1-1)-го блока памяти, а выходы 1-го блока памяти соединены с вторыми и третьими входами ( блока памяти, К-й блок памяти подключен своими первыми выходами к входам третьего регистра, соединенного своими выходами с вторым выходом опознавателя синхросиг-. налов, синхронизирующий вход третьего регистра - о вторым выходом К-го блока памяти и с входом второго регистра, выход которого подключен к первому выходу опознавателя синхросигналов, перзый вход опознавателя синхросигналов соединен с информационным входом регистра сдвига и информационной шиной, тактовые ВХОДЫ регистра сдвига и счетчика импульсов соединены с шиной тактовой синхронизации.

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1985 |

|

SU1278970A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-12-15—Публикация

1988-06-20—Подача