1

(21)4498705/24-24

(22)28.10.88

(46) 15.08.90. Бюл. № 30

(72) О.М. Поваренке, В.Д. Пысин

и В.Н. Чернышев

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 1221651, кл. G 06 F 7/548, 1984.

Авторское свидетельство СССР № 1273920, кл. G 06 F 7/548, 1985.

(54)УСТРОЙСТВО ВЫЧИСЛЕНИЯ ФУНКЦИИ АРКТАНГЕНС ОТНОШЕНИЯ

(57)Изобретение относится к вычислительной технике и предназначено для аппаратурной реализации вычисления

функции f arctg у/х в быстродействующих цифровых специализированных вычислительных устройствах и системах. Работа устройства основана на. кусочно-линейной аппроксимации функции (О arctg у/х. Для повьшзения быстродействия за счет использования арифметических устройств, работающих с фиксированной запятой, и распараллеливания вычислительного процесса в устройство введены два регистра, два преобразователя дополнительгюго кода, блок памяти констант, два блока памяти коэффициентов, схема сравнения знаков, о-мматор, регистр результата 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

| Устройство для вычисления функций Z @ = @ @ @ / @ и Z @ = @ @ @ / @ | 1988 |

|

SU1539771A1 |

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Вычислительное устройство | 1989 |

|

SU1691837A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

Изобретение относится к вычислительной технике и предназначено для аппаратурной реализации вычисления функции φ=ARCTG Y/X в быстродействующих цифровых специализированных вычислительных устройствах и системах. Работа устройства основана на кусочно-линейной аппроксимации функции φ=ARCTG Y/X. Для повышения быстродействия за счет использования арифметических устройств, работающих с фиксированной запятой, и расспараллеливания вычислительного процесса в устройство введены два регистра, два преобразователя дополнительного кода, блок памяти констант, два блока памяти коэффициентов, схема сравнения знаков, сумматор, регистр результата. 1 ил.

Изобретение относится к вычислительной технике и предназначено для аппаратурной реализации устройств вычисления функции 1 arctg у/х в быстродействующих цифровых специализированных вычислительных устройствах и системах.

Целью изобретения является повышение быстродействия.

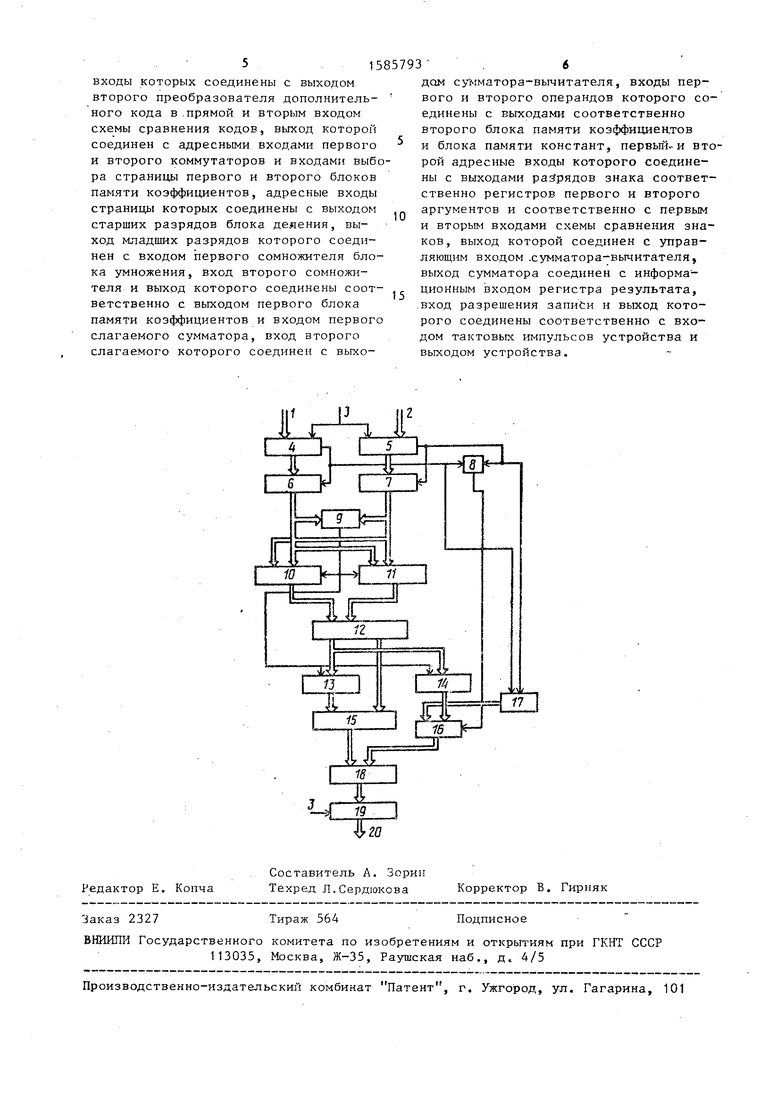

На чертеже изображена блок-схема устройства.

Устройство содержит входы 1 и 2 первого и второго аргументов, тактовый вход 3, регистры 4 и 5 первого и второго аргументов, первый 6 и второй 7 преобразователи дополнительного кода в прямой,схему 8 сравнения знаков, схему 9 сравнения кодов, первьй 10 и второй 11 коммутаторы, блок 12 .деления, блоки 13 и 14 памяти коэффициентов, блок 15 умножения, сумматорвычитатель 16, блок 17 памяти констант, сумматор 18, регистр 19 результата, выход 20 устройства.

Устройство позволяет вычислять функцию (f arfctg у/х в диапазоне 0,2..

Работа устройства основана на кусочно-линейной аппроксимации функции о( arctg Z в диапазоне главного значения арктангенса (О о 7Г/2) следу- юшлм выражением:

o(K.(z - г,) + ,. . (1)

Рассмотрим i-интервал аппроксимации.

Задавшись условием, что число интервалов аппроксимации кратно 2 и максимум ошибки аппроксимации в каждом из интервалов не превьшает заданную, можно определить число интервалов аппроксимации М, а также значения

СП 00

ел

со оо

V - ( i

- -i:, arctg Zj . (2)

Для расчета значения функции tf в интервале 0,21Г j необходимо дополнить главное значение функции постоянной величиной ITp, где р 0,1,2 в зависимости от знаков операндов х и у, т.е.

Cf K.z - z .) + , + р. (3)

Обозначив значения ,+ Тр через 1/ 5 получили

О + . , если X , у : 0;

(4)

И

5 если X О, у 5-0) , если X О, у 0; , если X : О, у О,

Устройство работает следующим образом.

Операнды входных чисел у и х, представленные в виде двоичного параллельного дополнительного кода с фиксированной запятой, поступают соответственно на входы 1 и 2 устройства и заносятся в регистры А и 5 соответст- венно по переднему фронту импульса на тактовом входе 3. С выхода регистров 4 и 5 мантиссы чисел у и х поступают на информационные входы соответственно первого 6 и второго 7 преобразователей, управляют работой которых знаковые разряды операндов у и х. Операнды чисел у и X поступают соответственно на информационные входы пер- Boi o 10 и второго 11 коммутаторов и на входы схемь 9 сравнения, которая управляет работой обоих коммутаторов и блока 17, так что при |у | ( х | через первый 10 коммутатор на входы делимого блока 12 деления поступает значение операнда у, а через второй коммутатор 11 на входы делителя блока 12 деления поступает значение операнда X, а при у I I X I через первый коммутатор 10 на вход делимого поступает значение операнда Xj через второй коммутатор 1 1 на вход делителя блока 12 деления поступает значение операнда у. На выходе блока деления значение z представлено в виде N-двоичных разрядов, из которых старшие N-L поступают на адресньш вход блоков 13 и 14 памяти коэффициентов, а L разрядов с выхода блока 12 - на вход углножителя 15 и представляют собой значение (z - z ), на другой вход умножителя с блока 13 поступает значение К;. С выхода блока 14 значе

0

5

0

5

0

5 5

0

45

0

ние , поступает на вход сумматора- вычитателя 16, на другой вход которо- |го поступает значение О, If , 21Г в соответствии с формулбй (4). Управление сумматором-вычитателем 16 осуществляется результатом сравнения знаков, формируемых схемой 8 сравнения знаков в соответствии с формулой (4). С выхода сумматора-вычитателя 16 значение fX |- + IT р поступает на вход сумматора 18, на другой вход которого поступает значение K.(z - Z;) с учетом масштабирования, т.е. со сдвигом на 2 разряда в сторону младших. С выхода сумматора 18 значение if поступает на информационные входь регистра 19 результата, где записывается по заднему фронту сигнала тактового входа 3 и поступает на выход устройства 20.

Формула изобретения Устройство вычисления функции арктангенс отношения, содержащее схему сравнения кодов,, первый и второй коммутаторы, блок деления, блок умножения и сумматор-вычитатель, причем выход первого коммутатора соединен с входом делимого блока деления, вьпсод второго коммутатора соединен с входом делителя блока деления, отличающееся тем, что, с целью повьшге- ния быстродействия, в него введены регистры первого и второго аргументов, регистр результата, первый и второй преобразователи дополнительного кода в прямой, схема сравнения знаков, первый и второй блоки памяти коэффициентов, блок памяти констант и сумматор, причем входы первого и второго аргументов устройства соединены с информационными входами соответственно регистра первого аргумента и регистра второго аргумента, входы разрешения записи которых -соединены с входом тактовых импульсов устройства, выходы регистров первого и второго аргументов соединены с информационными входами соответственно первого и второго преобразователей дополнительного кода в прямой, управляющие входы которых соединены с выходами знака регистров соответственно первого и второго аргументов, выход первого преобразователя дополнительного кода в прямой соединен с первым входом схемы сравнения кодов и первыми информационными входами первого и второго коммутаторов, вторые информационные

входы которых соединены с выходом второго преобразователя дополнитель- ного кода в .прямой и вторым входом схемы сравнения кодов, выход которой соединен с адресными входами первого и второго коммутаторов и входами выбора страницы первого и второго блоков памяти коэффициентов, адресные входы страницы которых соединены с выходом старших разрядов блока деления, выход младших разрядов которого соединен с входом первого сомножителя блока умножения, вход второго сомножителя и выход которого соединены соответственно с выходом первого блока памяти коэффициентов и входом первого слагаемого сумматора, вход второго слагаемого которого соединен с вьгхоТ .

1

Редактор Е. Копча

Составитель А. Зорин Техред Л.Сердюкова

Заказ 2327

Тираж 564

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

0

5

дом су 1матора-вьгчитателя, входы первого и второго операндов которого соединены с выходами соответственно второго блока памяти коэффициентов и блока памяти констант, перньш-и второй адресные входы которого соединены с выходами разрядов знака соответственно регистров первого и второго аргументов и соответственно с первым и вторым входами схемы сравнения знаков, выход которой соединен с управляющим входом .сумматора-вычитателя, выход сумматора соединен с информационным входом регистра результата, .вход разрешения записи и выход которого соединены соответственно с входом тактовых импульсов устройства и выходом устройства.

и.-.

г:

Корректор В. Гирняк

Подписное

Авторы

Даты

1990-08-15—Публикация

1988-10-28—Подача