Изобретение относится к вычислительной технике и предназначено для использования в специализированных ЦВМ для вычисления элементарных функций,,

Цель изобретения - повышение точности.

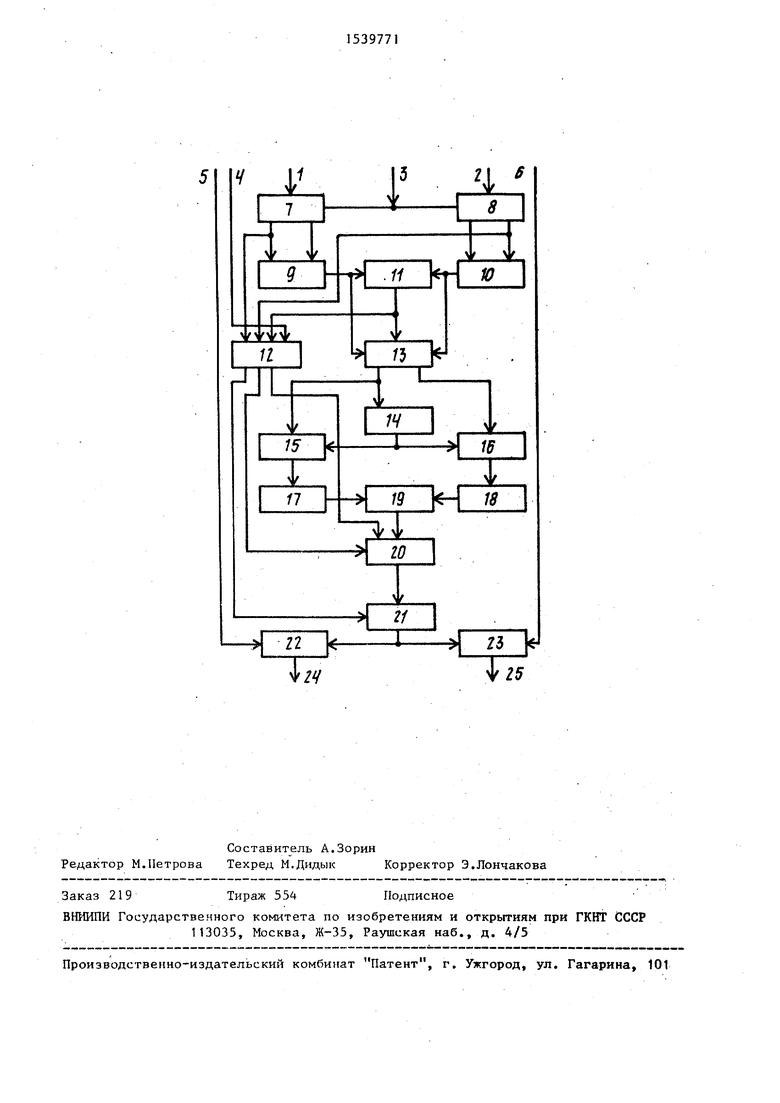

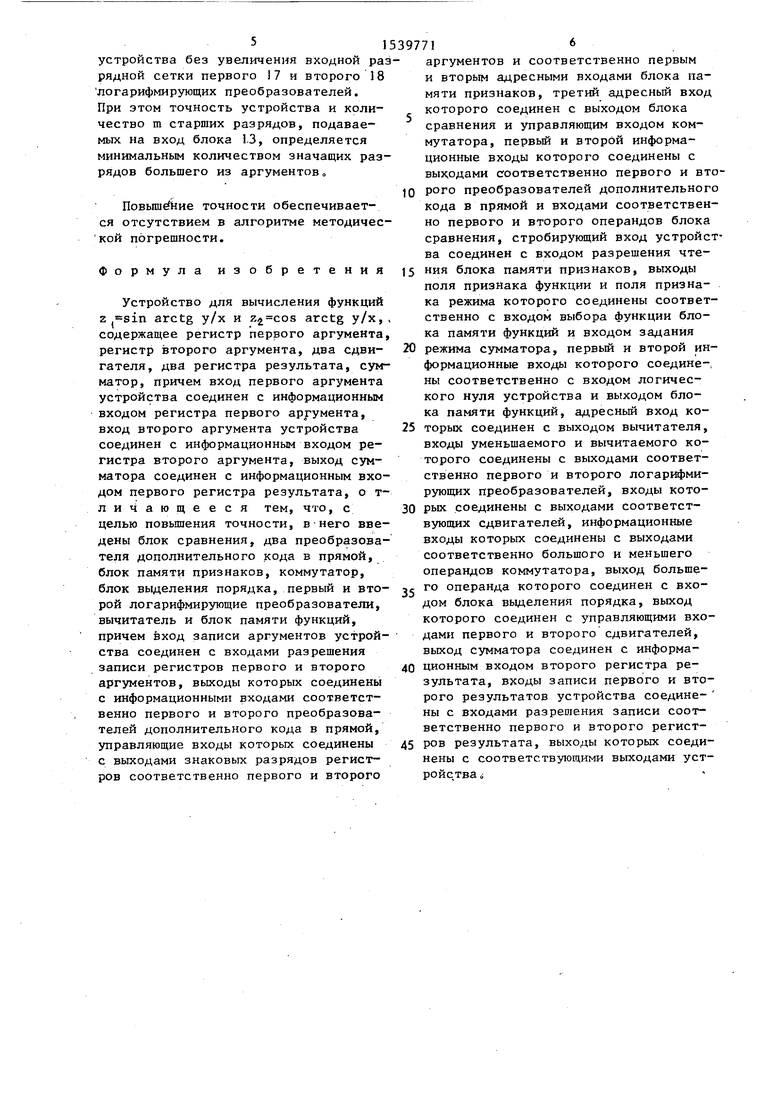

На чертеже представлена структурная схема устройства.

Устройство содержит первый 1 и второй 2 входы аргумента, вход 3 записи аргумента, вход 4 строба, входы записи первого 5 и второго 6 результатов, регистры первого 7 и второго 8 аргументов, первый 9 и второй 10 преобразователи дополнительного кода в прямой, блок 11 сравнения, блок 12 памяти признаков, коммутатор 13, блок 14 выделения порядка, первый 15

и второй 16 сдвигатели, первый 17 и второй 18 логарифмирующие преобразователи, вычитатель 19, блок 20 памяти функций, сумматор 21, первый 22 и второй 23 регистры результата, первый 24 и второй 25 выходы устройства.

Работа устройства описывается следующими математическими отношениями:

х , max

txl, I yi} ; у, min (| xl , 1:1};

v a b

a

b, с

A В

ent loga x,; x

-y, --v

1о8. а Iog2 b;

a- - Ь 9 с sin arctg /- ;

cos arctg 2.

0)

СД

00

со J J

-c

.

А В В А

-А -В

-В

-А

zz

В,если

А,если

-А,если

В,если

-В,если

-А,если

A,если

B,если

О, у 0, Ъ О, У 0, 0, у 0, 0, ,

0,,

О,у 0,

т О,у 0,

0,,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля и аргумента вектора | 1986 |

|

SU1403063A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Устройство для вычисления функции арктангенса отношения | 1988 |

|

SU1615709A1 |

| Устройство для вычисления функции | 1986 |

|

SU1348829A1 |

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Устройство для выполнения преобразования координат | 1987 |

|

SU1462299A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Устройство для вычисления функции арктангенса отношения | 1990 |

|

SU1751750A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления значений функций в специализированных ЦВМ. С целью повышения точности за счет устранения методической погрешности в устройство введены два регистра, два преобразователя дополнительного кода в прямой, блок сравнения, коммутатор, блок выделения приоритета, два сдвигателя, два логарифмирующих преобразователя, вычитатель, блоки памяти признаков и функций, сумматор. Устройство может использоваться для нахождения значений функций Z1 и Z2 в процессорах цифровой обработки сигналов. 1 ил.

Устройство работает следующим образом.

Операнды входных чисел х и у, представленные в виде двоичного параллельного дополнительного кода (п разрядов Мантиссы и 1 разряд знаковый) с фиксированной запятой, поступают соответственно на входы 1 и 2 устройства и заносятся в регистры 7 и 8 соответственно по сигналу с входа 3, с выходов регистров 7 и 8 мантиссы чисел х и у поступают на информационные входы соответственно первого 9 и второго 10 преобразователей дополнительного кода в прямой, управляют работой которых знаковые разряды операндов х и у„ С выходов первого 9 и второго 10 преобразователей дополнительного кода в прямой операнды чисел х и lyl поступают на входы блока 11 сравнения и информационный вход коммутатора 13. Блок 11 сравнения определяет, какое из чисел больше, и своим выходным сигналом управляет работой коммутатора 13. Последний построен так, что на его первом .выходе появлется операнд, соответствующий большему числу (х(), а на втором выходе - операнд, соответствующий меньшему числу (у ). С первого и второго выходов коммутатора 13 операнды чисел х и у, постуглют на информационные входы первого 15 и второго 16 сдвигателей соответственно„ Одновременно га старших разрядов числа х поступают на вход блока 14 выделения порядка, на выходе которого образуется двоичный параллельный код номера старшего значащего разряда числа х , который управляет работой первого 15 и второго 6 сдвигателей С выходов первого 15 и второго 16 сдвигателей k-разрядные операнды а и Ъ поступают на входы соответственно первого 17 и второго 18 логарифмирующих преобразователей, с выходов которых операнды чисел а, и Ь, по5

0

5

0

5

0

5

0

5

,ступают соответственно на входы вы- читателя 19„ Количество m старших разрядов числа х , поступающих на

вход блока 14J, определяется из соотношения

m п - ko

Блок 14 выделения порядка совместно с первым сдвигателем 15 производит сдвиг так, чтобы на выходе первого сдвигателя 15 старшая значащая цифра числа х( находилась в старшем разряде (за исключением случая, когда m или более старших разрядов числа х являются нулями, при этом сдвиг производится на m разрядов влево). С выходов знаков регистров 7 и 8 знаковые разряды чисел х и у поступают соответственно на первый и второй адресные входы блока 12 памяти признаков, на третий адресный и разрешающий входы которого поступают сигнал с выхода блока 11 сравнения и стробирующийсигнал с входа 4 соответственно С выхода вычитателя 19 операнд числа поступает на вход блока 20 памяти функций, который производит преобразование информации в соответствии с функциональными зависимостямиА sin arctg и В cos arctg в зависимости от сигнала блока 12„ Операнды чисел А и В (S разрядов) с выхода блока 20 памяти функций последовательно поступают на вход второго слагаемого сумматора 21, на вход первого слагаемого которого подается лог. О, а на вход режима - сигнал с выхода блока 12. Блоки 12, 20 и 21 работают в соответствии с выражением (2). Запись значений в регистры 22 и 23 производится по сигналам, поступающим на входы регистров с входов 5 и 6о Выходы регистров 22 и 23 соответственно являются синусным 24 и косинусным 25 выходами устройства

Введение в устройство блока 14 выделения порядка позволяет расширить диапазон представления входных чисел

устройства без увеличения входной разрядной сетки первого 7 и второго 18 логарифмирующих преобразователей. При этом точность устройства и количество m старших разрядов, подаваемых на вход блока 13, определяется минимальным количеством значащих разрядов большего из аргументов«,

Повышение точности обеспечивается отсутствием в алгоритме методической погрешности.

Формула изобретения

Устройство для вычисления функций z (sin arctg y/x и arctg у/х,, содержащее регистр первого аргумента, регистр второго аргумента, два сдви- гателя, два регистра результата, сумматор, причем вход первого аргумента устройства соединен с информационным входом регистра первого аргумента, вход второго аргумента устройства соединен с информационным входом регистра второго аргумента, выход сумматора соединен с информационным входом первого регистра результата, о т- личающееся тем, что, с целью повышения точности, в него введены блок сравнения, два преобразователя дополнительного кода в прямой, блок памяти признаков, коммутатор, блок выделения порядка, первый и второй логарифмирующие преобразователи, вычитатель и блок памяти функций, причем вход записи аргументов устройства соединен с входами разрешения записи регистров первого и второго аргументов, выходы которых соединены с информационными входами соответственно первого и второго преобразователей дополнительного кода в прямой, управляющие входы которых соединены с выходами знаковых разрядов регистров соответственно первого и второго

аргументов и соответственно первым и вторым адресными входами блока памяти признаков, третий адресный вход которого соединен с выходом блока сравнения и управляющим входом коммутатора, первый и второй информационные входы которого соединены с выходами соответственно первого и втоQ рого преобразователей дополнительного кода в прямой и входами соответственно первого и второго операндов блока сравнения, стробирующий вход устройства соединен с входом разрешения чте5 ния блока памяти признаков, выходы поля признака функции и поля признака режима которого соединены соответственно с входом выбора функции блока памяти функций и входом задания

0 режима сумматора, первый и второй информационные входы которого соединены соответственно с входом логического нуля устройства и выходом блока памяти функций, адресный вход ко5 торых соединен с выходом вычитателя, входы уменьшаемого и вычитаемого которого соединены с выходами соответственно первого и второго логарифмирующих преобразователей, входы кото0 рых соединены с выходами соответствующих сдвигателей, информационные входы которых соединены с выходами соответственно большого и меньшего операндов коммутатора, выход большего операнда которого соединен с входом блока выделения порядка, выход которого соединен с управляющими входами первого и второго сдвигателей, выход сумматора соединен с информа0 ционным входом второго регистра результата, входы записи первого и второго результатов устройства соедине- ны с входами разрешения записи соответственно первого и второго регист5 ров результата, выходы которых соединены с соответствующими выходами устройства о

5

Т

24

25

| Арифметическое устройство | 1979 |

|

SU798824A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1979 |

|

SU798821A1 |

Авторы

Даты

1990-01-30—Публикация

1988-02-23—Подача