ГО

Изобретение относится к автоматике и вычислительной технике, может быть использовано в устройствах отображения графической информации, уст- 5

ройствах числового программного управления оборудованием и является усовершенствованием интерполятора по авт. св.

№ 1423984.

Цель изобретения - повышение надеж- кости в работе интерполятора за счет контроля выдачи шаговых координатных приращений.

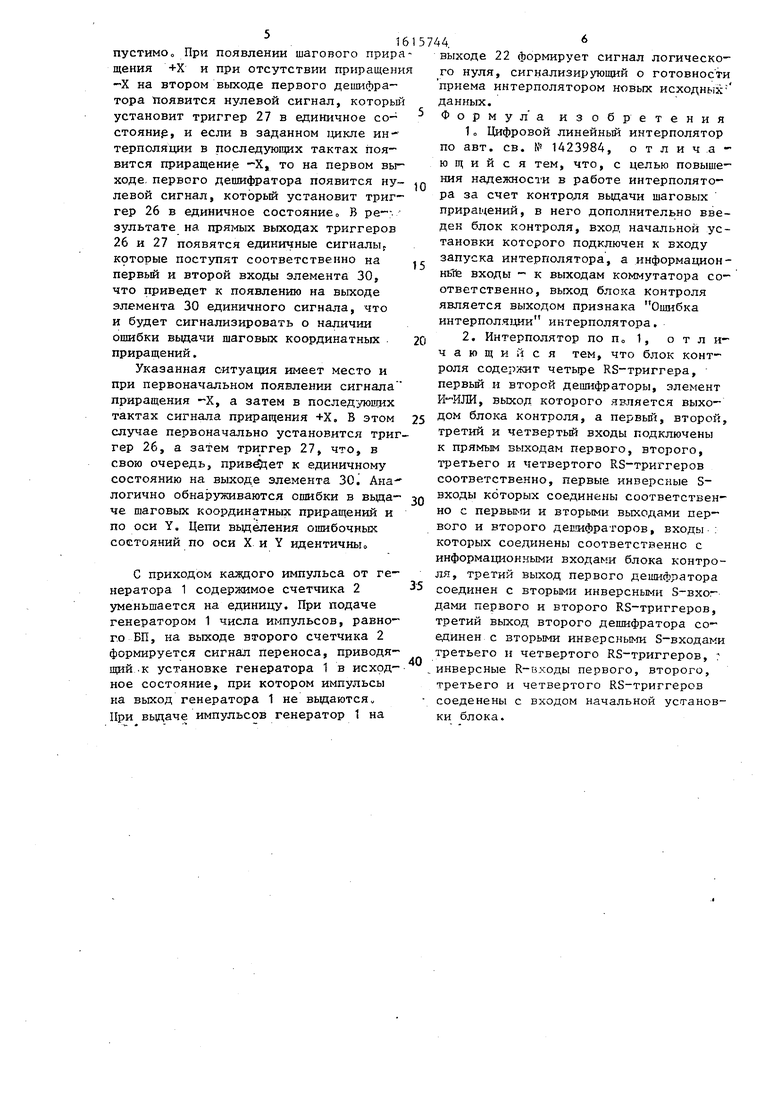

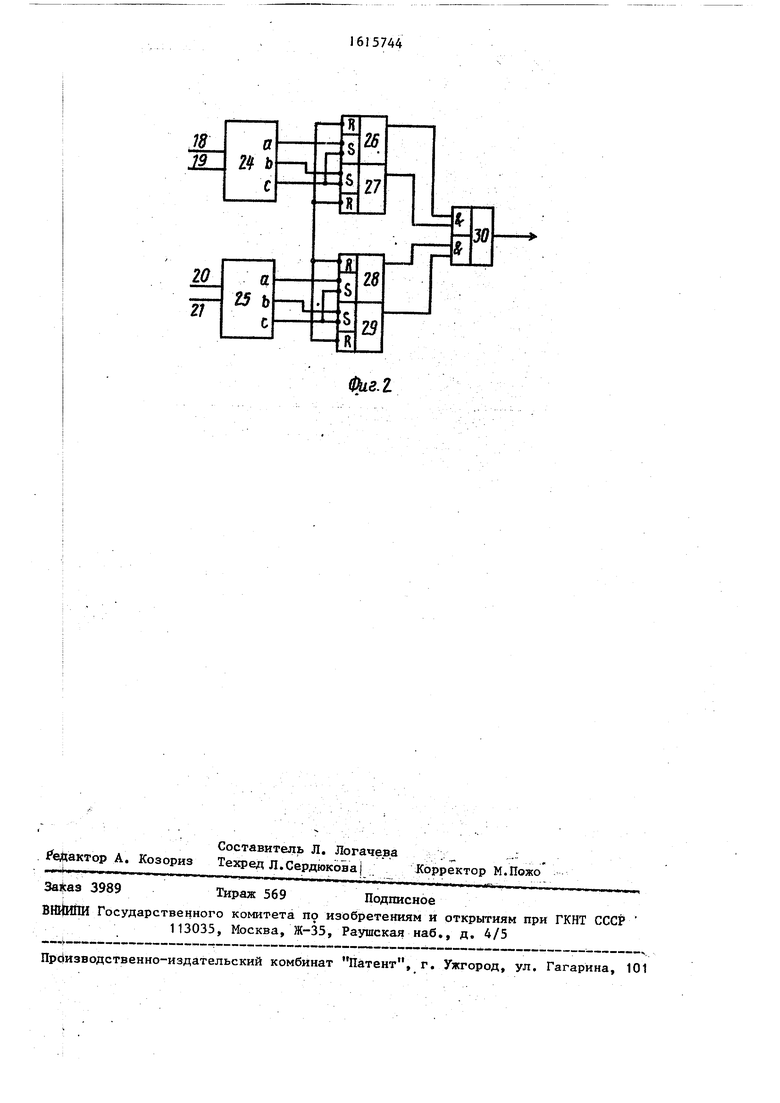

На фиг. 1 представлена структурная ,- схема цифрового линейного интерполятора; на фиг 2 - функциональная схема блока контроля.

Цифровой линейньй интерполятор содержит зт равляемьй генератор 1 импульсов, второй счетчик 2, первый ре-- гистр 3, узел 4 двоичного умножения, первьй счетчик 5, второй регистр 6, коммутатор 7, вход 8 начальной уста- ; новкй, вход 9 запуска, вход 10 зада- 25 ния большего приращения, вход 11 записи, вход 12 управляющего кода, вход 13 записи, входы.14-17 признаков ко- ординатной ориентации, входы 18-21 ша говых координатных приращений, в&ход 22 признака Окончание интерполяции и блок 23 контроля.

Блок 23 контроля (фиг. 2) содержит дешифраторы 24 и 25, КЗ-триггеры 26- 29 и элемент И-ИЛИ 30.

Штерполятор работает следующим об разом.

По включению питания на входе 8 начальной установки интерполятора от i внешнего устройства.поступает импульс устанавливающий управляемьй генерап тор 1 импульсов в исходное положение. На выходе генератора 1 импульсы не формируются. Во второй регистр 6 по активному уровню сигнала на входе 13 записывается значение признаков.

В первьй регистр 3 от входного устройства записывается значение управляющего кода, поступающего на вход 12 управляющего кода интерполятора. Запись в регистр осуществляется нуле- вым уровнем, подаваемым на вход 11 записи интерполятора. В счетчик 2 записывается значение большего приращения, поступающего на вход 10 интер- - полятора. Запись осуществляется нуле- вым уровнем сигнала, подаваемого йа вход 9 запуска интерполятора По переднему фронту указанного сигнала

40

45

-

5

0

5

запускается генератор 1 импульсов и на его выходе формируется последовательность импульсов заданной частоты. Указанная последовательность импульсов поступает на счетньй вход счетчика 5. При этом на выходе узла двоиЧ|НО- го умножения формируется последовательность импульсов, соответствующих меньшему приращению (по ведомой коор- динате). Коммутатор 7 осуществляет в зависимости от значения признаков, записанных в регистр 6, перекоммута- цню частотных потоков, поступаемых от генератора 1 и узла 4 двоичного умножения на один из входов +Х, -X, +Y, -Ч..

Контроль основан на следующем При интерполировании отрезка прямой в дискретном координатном пространсх- ве согласно восьмивекторньм алгоритмам линейной интерполяции вьщача шаго вых приращений осуществляется только по ведущей и ведомой координатам, т.во возможны следующие ситуации: шаговые приращения выдаются только по ведущей координате; выдача происходит по ведущей и ведомой координатам вместе, т.е. формируется диагональньй шаг. Нулевой уровень сигнала на вто- ром входе 9 интерполятора устанавливает триггеры 26-29 блока контроля в нулевое состояние.

Рассмотрим случай, когда в работе . интерполятора появляется запрещенная ситуация. Если по координатам +Х и -X сразу-. постзт1ит два единичных сигнала, то на третьем выходе первого де- шифратора появится сигнал нулевого уровня, которьй установит триггеры 26 и 27 в единичное состояние. Единичные уровни сигналов, снятые с прямых выходов триггеров 26 и 27, поступают ветственно на первьй и второй входы элемента 30, что приведет к появлению на его выходе единичного уровня сигнала, которьй будет сигнализировать о наличии ошибки в вьщаче шаговых координатных приращений.

Рассмотрим случай, когда по ведомой координате, например координате X, при интерполировании одного и того же отрезка прямой будут сформированы в различных интерполяционных тактах шаговые приращения, соответствующие различным направлениям (. приращения +Х, -X). Указанное при восьмивек- торных алгоритмах интерполяции недопустимОо При появлении шагового приращения +Х и при отсутствии приращени -X на втором выходе первого дешифратора появится нулевой сигнал, которьш установит триггер 27 в единичное со- стояние, и если в заданном щкяе ин- терполяции в последующих тактах появится приращение -X, то на первом выходе, первого дешифратора появится нулевой сигнал, который установит триггер 26 в единичное состояние, В ре-, зультате на пря1.1ых выходах триггеров 26 и 27 появятся единичные сигналы которые поступят соответственно на первый и второй входы элемента 30, что приведет к появлению на выходе элемента 30 единичного сигнала, что и будет сигнализировать о наличии ошибки вьщачи шаговых координатных приращений,

Указанная ситуация имеет место и при первоначальном появлении сигнала приращения -X, а затем в последующих тактах сигнала приращения +Х, В этом случае первоначально установится триггер 26, а затем триггер 27, что, в свою очередь, приврет к единичному состоянию на выходе элемента 30. Ана логично обна15уживаются ошибки в вьща- че шаговых координатных приращений и по оси Y. Цепи вьщеления онибочных состояний по оси X и Y идентичны

С приходом каждого импульса от генератора 1 содержимое счетчика 2 уменьшается на единицу. При подаче генератором 1 числа импульсов, равного БП, на выходе второго счетчика 2 формируется сигнал переноса, приводящий .к установке генератора 1 в исходное состояние, при котором импульсы на выход генератора 1 не выдаютсяv При вьщаче импульсов генератор 1 на

10

15

20

15744.

выходе 22 формирует сигнал логического нуля, сигнализирующий о готовности приема интерполятором новых исходных данных.

5 Форму л а изобретения 1 о Цифровой линейньй интерполятор по авт. св. № 1423984, отличающийся тем, что, с целью повышения надежности в работе интерполятора за счет контроля вьщачи шаговых приращений, в него дополнительно введен блок контроля, вход начальной установки которого подключен к входу запуска интерполятора, а информационный входы - к выходам коммутатора соответственно, выход блока контроля является выходом признака Ошибка интерполяции интерполятора.

2. Интерполятор по По 1, отличающийся тем, что блок контроля содержит четыре RS-триггера, первьй и второй дешифраторы, элемент И-ИЛИ, выход которого является выхо- 25 дом блока контроля, а первьш, второй, третий и четвертьй входы подключены к прямым выходам первого, второго, третьего и четвертого RS-триггеров соответственно, первые инверсные S- входы которых соединены соответственно с первыми и вторыми выходами первого и второго дешифраторов, входы ; которых соединены соответственно с информационными входами блока контроля, третий выход первого дешифратора соединен с вторыми инверсными S-вхог- дами первого и второго RS-триггеров, третий выход второго дешифратора соединен с вторыми инверсными S-входами третьего и четвертого RS-триггеров, : , инверсные R-входы первого, второго, третьего и четвертого RS-триггеров соеденены с входом начальной установки блока.

30

35

40

Фиг.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейно-круговой интерполятор | 1984 |

|

SU1215090A2 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Линейный интерполятор | 1988 |

|

SU1522157A1 |

| Цифровой линейный интерполятор | 1990 |

|

SU1805449A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Устройство для управления многокоординатным оборудованием | 1987 |

|

SU1427334A1 |

| Линейный интерполятор | 1989 |

|

SU1674064A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1675849A1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в выводных графических устройствах и системах с числовым программным управлением. Цель изобретения - повышение надежности работы интерполятора за счет контроля выдачи шаговых приращений. Линейный интерполятор содержит формирователь импульсов 1, первый счетчик 2, первый регистр 3, логическую схему 4 двоичного умножителя, второй счетчик 5, второй регистр 6, блок выходной логики 7, блок 23 контроля. Блоки 4 и 5 образуют интегратор последовательного переноса. В блоке 23 контроля при изменении направления выдачи элементарных приращений или изменении ведущего направления на выходе вырабатывается сигнал ошибки. 1 з.п. ф-лы, 2 ил.

Авторы

Даты

1990-12-23—Публикация

1989-01-02—Подача