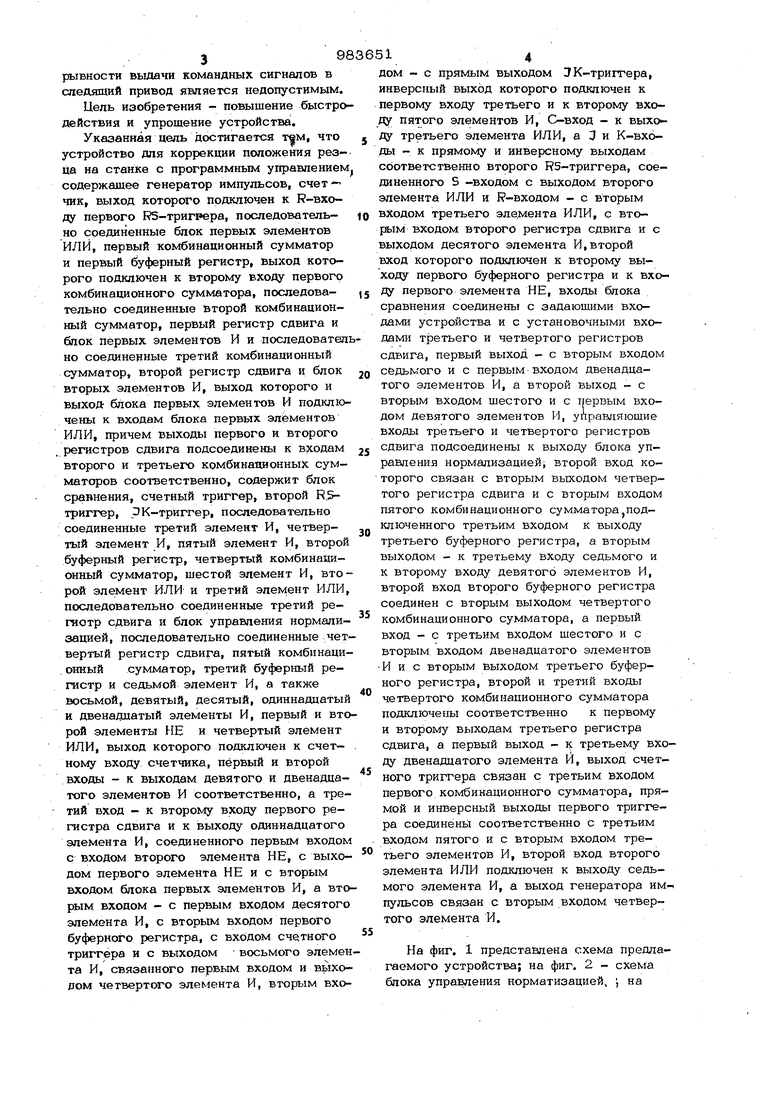

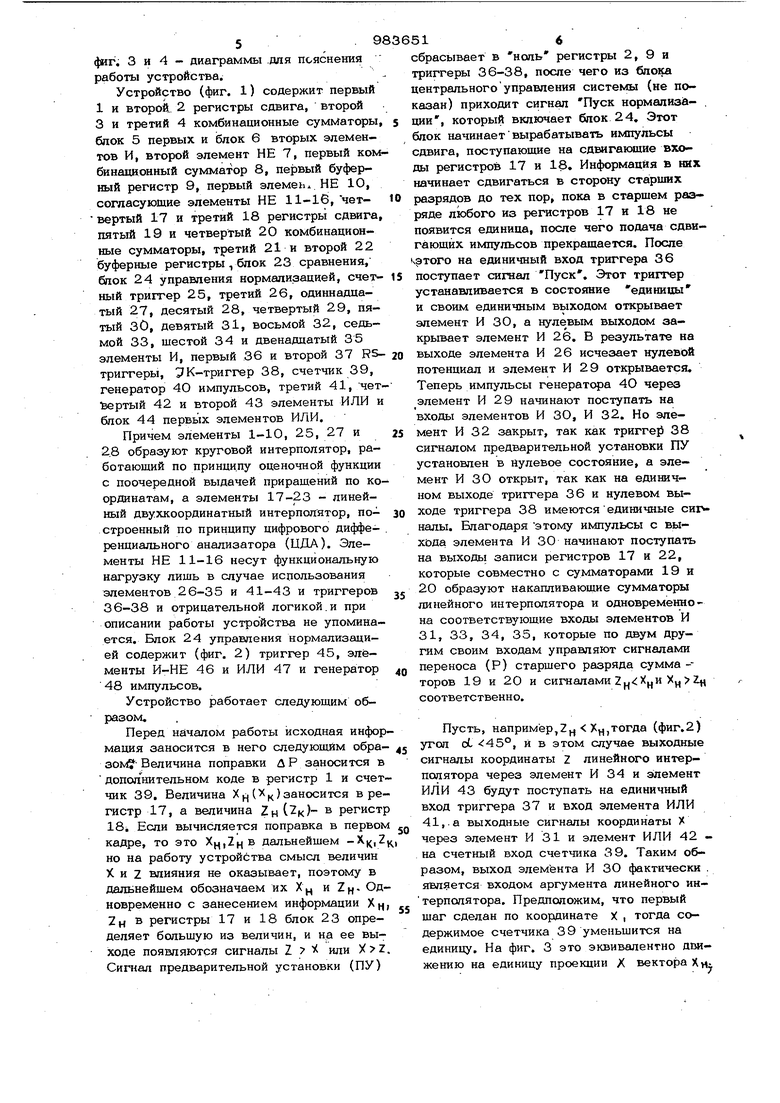

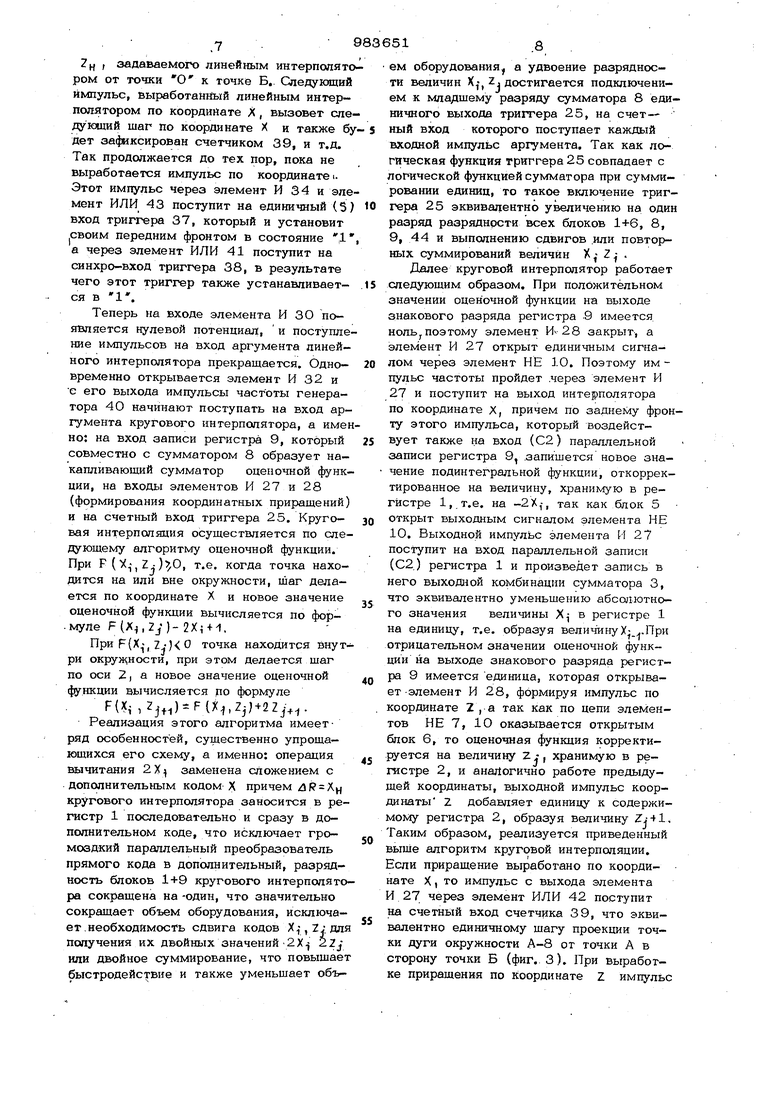

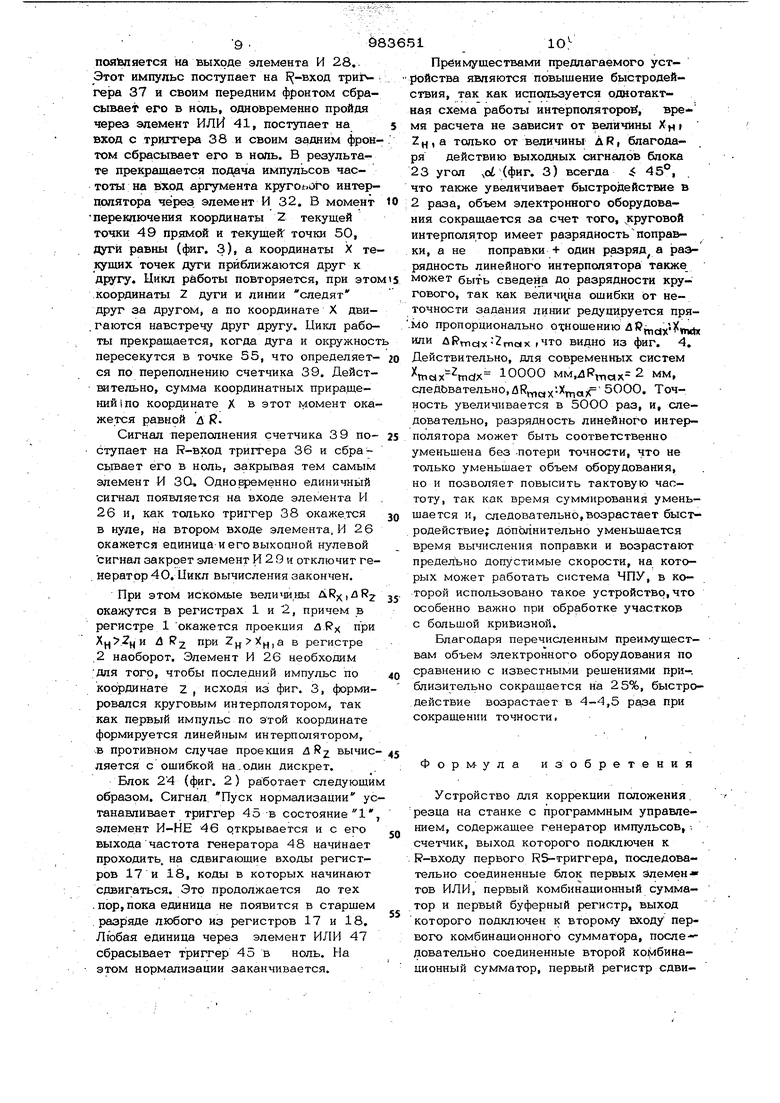

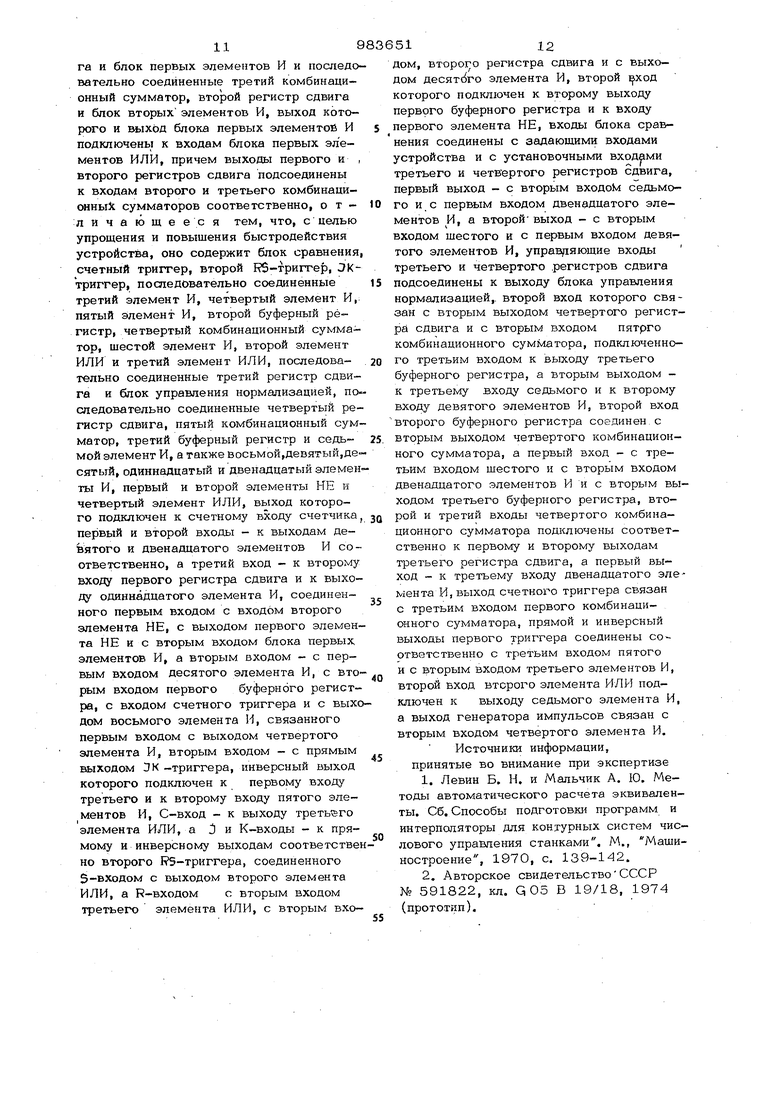

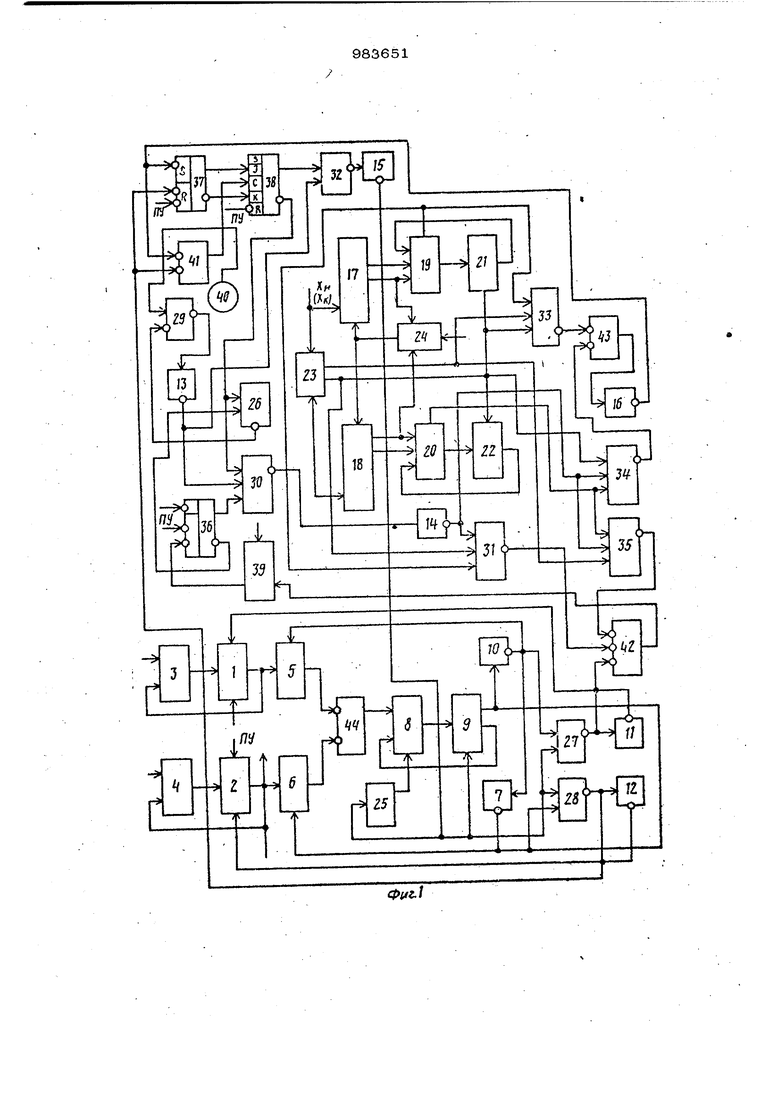

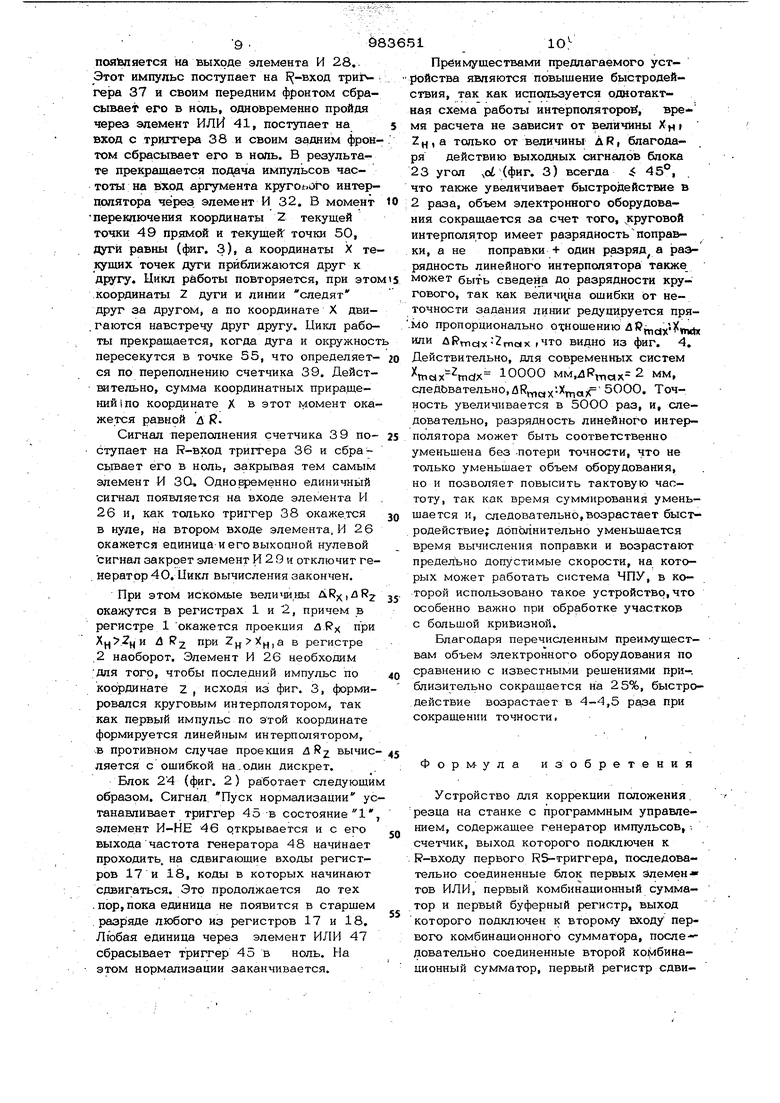

Изобретение относится к автоматике и вычислительной технике и может быть,; использовано в системах числового про-, граммного управления станками. Известно устройство для коррекции . эквидистанты, состоящие из двух цифровых квадратов, генератор тактовых им- . пульсов и счетчика, основанное на сравнении квадрата величины поправки ЛР с квадратами проекций поправки на координатные оси, что осуществляется путем сложных вычислений El. Недостатком этого устройства является сложность. Наиболее близким техническим решени ем к данному изобретению является устройство Для коррекции эквидистанты, содержащее блок задания программы, основной, линейно-круговой интерполятор, блок выделения нуля, генератор тактовых импульсов (ГТИ), блок регистраш1и окончания коррекции, логический блок и каналы связи. Это устройство позволяет сократить время нахождения координаты искомой точки путем олодновременного поворота заданного радиуса-вектора с координатами ХЦ,УН ( поправки дР Г2J. Недостатком указанного устройртва являются большой объем электронного оборудования ввиду использования двух круговых интерполяторов, построенных на цифровых дифференциальных анализиторах (ПДА), и значительные погрешности вычисления определяющиеся тем, что угловые цены импульсов аргумента интерполятора поправки AR и основной траектории оказываются далеко не одинаковыми и наконец, низкое быстродействие, определяемое максимально возможным радиусом основной траектории, который в токарных станках на оживальных поверхностях может составлять 10- м, что при цене импульса 0,О01 мм соответствует 9999999 отсчетам, поэтому время расчета, даже при быстродействии основного кругового интерполятора 500;000 кГц, составит 20 с, что по условиям непре- 9 рывности выдачи командных сигналов в сяешпций привод является недопустимым. Цель изобретения - повышение быстро действия и упрощение устройства. Указанная цель достигается тем, что устройство для коррекции положения резца на станке с программным управлением содержащее генератор импульсов, счет - чик, выход которого подключен к Г -вхо-ду первого RS-тригрера, последовательно соединенные блок первых элементов ИЛИ, первый комбинационный сумматор и первый буферный регистр, выход которого подключен к второму входу первого комбинационного сумматора, последовательно соединенные второй комбинационный сумматор, первый регистр сдвига и бпок первых элементов И и последоватезт но соединенные третий комбинационный сумматор, второй регистр сдвига и блок вторых элементов И, выход которого и выход блока первых элементов И подключены к входам блока первых элементов ИЛИ, причем выходы первого и второго регистров сдвига подсоединены к входам второго и третьего комбинационных сумматоров соответственно, содержит блок сравнения, счетный триггер, второй R,5триггер, рК-триггер, последовательно соединенные третий элемент И, четвертый элемент И, пятый элемент И, второй буферный регистр, четвертый комбинационный сумматор, шестой элемент И, второй элемент ИЛИ и третий элемент ИЛИ, последовательно соединенные третий регистр сдвига и блок управления нормализацией, последовательно соединенные чет вертый регистр сдвига, пятый комбинационный сумматор, третий буферный регистр и седьмой элемент И, а также восьмой, девятый, десятый, одиннадцатый и двенадцатый элементы И, первый и вто рой элементы НЕ и четвертый элемент ИЛИ, выход которого подключен к счет- ному входу счетчика, первый и второй входы - к выходам девятого и двенадцатого элементов И соответственно, а третий вход - к второму входу первого регистра сдвига и к выходу одиннадцатого элемента И, соединенного первым входом С входом второго элемента НЕ, с выходом первого элемента НЕ и с вторым входом блока первых элементов И, а вто рым входом - с первым входом десятого элемента И, с вторым входом первого буферного регистра, с входом счетного триггера и с выходом восьмого элемен та И, связанного первым входом и выходом четвертого элемента И, вторым вхо514дом - с пряк(ым выходом JK-триггера, инверсный выход которого подключен к первому входу третьего и к второму входу пятого элементов И, С-вход - к выходу третьего элемента ИЛИ, а 3 и К-входы - к прямому и инверсному выходам соответственно второго RS-TpHrrepa, соединенного S -входом с выходом второго элемента ИЛИ и R-входом - с вторым входом третьего элемента ИЛИ, с вторым входом второго регистра сдвига и с выходом десятого элемента И,второй вход которого подключен к второму выходу первого буферного регистра и к входу первого элемента НЕ, входы блока сравнения соединены с задающими входами устройства и с установочными входами третьего и четвертого регистров сдвига, первый выход - с вторым входом седьмого и с первым входом двенадцатого элементов И, а второй выход - с вторым входом шестого и с первым входом Девятого элементов И, управляющие входы третьего и четвертого регистров сдвига подсоединены к выходу блока управления нормализацией, второй вход которого связан с вторым выходом четвертого регистра сдвига и с вторым входом пятого комбинационного сумма тора.подключенного третьим входом к выходу третьего буферного регистра, а вторым выходом - к третьему входу седьмого и к второму входу девятого элементов И, второй вход второго буферного регистра соединен с вторым выходом четвертого комбинационного сумматора, а первый вход - с третьим входом шестого и с вторым входом двенадцатого элементов И и с вторым выходом третьего буферного регистра, второй и третий входы четвертого комбинационного сумматора подключены соответственно к первому и второму выходам третьего регистра сдвига, а первый выход - к третьему входу двенадцатого элемента И, выход счетного триггера связан с третьим входом первого комбинационного сумматора, прямой и инверсный выходы первого триггера соединены соответственно с третьим входом пятого и с вторым входом третьего элементов И, второй вход второго элемента ИЛИ подключен к выходу седьмого элемента И, а выход генератора импульсов связан с вторым входом четвертого элемента И. На фиг, 1 представлена схема предлагаемого устройства; на фиг. 2 - схема блока управления норматизацией, . на 5У 4иг. 3 и 4 - диаграммы .для пояснения работы устройства. Устройство (фиг. 1) содержит первый 1 и второй„ 2 регистры сдвига, второй 3 и третий 4 комбинационные сумматоры, блок 5 первых и блок 6 вторых элементов И, второй элемент НЕ 7, первый комбинационный сумматор 8, первый буферный регистр 9, первый элемеь НЕ Ю, согласующие элементы НЕ 11-16, четвертый 17 и третий 18 регистры сдвига, пятый 19 и четвертый 20 комбинационные сумматоры, третий 21 и второй 22 буферные регистры , блок 23 сравнения, блок 24 управления нормализацией, счетный триггер 25, третий 26, одиннадцатый 27, десятый 28, четвертый 29, пятый ЗО, девятый 31, восьмой 32, седьмой 33, шестой 34 и двенадцатый 35 элементы И, первый 36 и второй 37 RSтриггеры, 5К-триггер 38, счетчик 39, генератор 40 импульсов, третий 41, четЪертый 42 и второй 43 элементы ИЛИ и блок 44 первых элементов ИЛИ. Причем элементы 1-10, 25, 27 и 2.8 образуют круговой интерполятор, работающий по принципу оценочной функции с поочередной выдачей приращений по координатам, а элементы 17-23 - линейный двухкоординатный интерполятор, построенный по принципу цифрового дифференциального анализатора (ЦДЛ). Элементы НЕ 11-16 несут функциональную нагрузку лишь в случае использования элементов 26-35 и 41-43 и триггеров 36-38 и отрицательной логикой.и при описании работы устройства не упоминается. Блок 24 управления нормализацией содержит (фиг. 2) триггер 45, элементы И-НЕ 46 и ИЛИ 47 и генератор 48 импульсов. Устройство работает следующим образом. Перед началом работы исходная инфор мация заносится в него следующим образом Величина поправки ДР заносится в дополнительном коде в регистр 1 и счетчик 39, Величина Х (Х) заносится в регистр 17, а величина ZH регистр 18i Если вычисляется поправка в первом кадре, то это Хц,2цВ дальнейшем -К|,2 но на работу устройства смысл величин KHZ влияния не оказывает, поэтому в дальнейшем обозначаем их Х и ZH- Одновременно с занесением информации XH, 2н S регистры 17 и 18 блок 23 определяет большую из величин, и на ее выходе появляются сигналы 2 ч или . Сигнал предварительной установки (ПУ) 9 51 516 сбрасывает в ноль регистры 2, 9 и триггеры 36-38, после чего из блока центрального управления системы (не показан) приходит сигнал Пуск нopмaпизia- , ции, который включает блок 24, Этот блок начинаетвырабатывать импульсы сдвига, поступающие на сдвигающие входы регистров 17 и 18. Информация в них начинает сдвигаться в сторону старщих разрядов до тех пор, пока в старшем разряде любого из регистров 17 и 18 не появится единица, после чего подача сдвигающих импульсов прекращается. После того на еда1ничный вход триггера 36 поступает сигнал Пуск. Этот триггер устанавливается в состояние единицы и своим единичным выходом открывает элемент И 30, а выходом закрывает элемент И 26. В результате на выходе элемента И 26 исчезает нулевой потенциал и элемент И 29 открывается, Теперь импульсы генератора 4О через элемент И 29 начинают поступать на ВХОДЫ элементов И ЗО, И 32. Но элемент И 32 закрыт, так как тригге 38 сигналом предварительной установки ПУ установлен в нулевое состояние, а элемент И ЗО открыт, так как на единичном выходе триггера 36 и нулевом выходе триггера 38 имеютсяединичные налы. Благодаря этому импульсы с выхода элемента И 30 начинают поступать на выходь записи регистров 17 и 22, которые совместно с сумматорами 19 и 2О образуют накапливающие сумматоры линейного интерполятора и одновремешона соответствующие входы элементов И 31, 33, 34, 35, которые по двум другим своим входам управляют сигналами переноса (Р) старшего разряда сумма -торов 19 и 20 и сигналами 2 н соответственно. Пусть, например,Z XH,тогда (фиг.2) d- 45°, и в этом случае выходные сигналы координаты 2 линейного интерполятора через элемент И 34 и элемент ИЛИ 43 будут поступать на единичный вход триггера 37 и вход элемента ИЛИ 41,.а выходные сигналы координаты X через элемент И 31 и элемент ИЛИ 42 на счетный вход счетчика 39. Таким образом, выход элемента И ЗО фактически . является входом аргумента линейного интерполятора. Предположим, что первый шаг сделан по координате X , тогда содержимое счетчика 39 уменьшится на единицу. На фиг. 3 это эквивалентно движению на единицу проекции X вектора XHI 2 , задаваемого линейным интерполято ром от точки О к точке Б.. Следующий импульс, выработан1{ы(й линейным интерполятором по координате X , вызовет сле дующий шаг по координате X и также бу дет зафиксирован счетчиком 39, и т.д. Так продолжается до тех пор, пока не выработается импульс по координате i. Этот импульс через элемент И 34 и эле мент ИЛИ 43 поступит на единичный (5) вход триггера 37, который и установит своим передним фронтом в состояние а через элемент ИЛИ 41 поступит на синхро-вход триггера 38, в результате чего этот триггер также устанавливается в . Теперь на входе элемента И ЗО появляется нулевой потенциал, и поступле ние импульсов на вход аргумента линейного интерполятора прекращается. Одновременно открывается элемент И 32 и С его выхода импульсы частоты генератора 40 начинают поступать на вход аргумента кругового интерполятора, а имен но: на вход записи регистра 9, который совместно с сумматором 8 образует накапливающий сумматор оценочной функции, на входы элементов И 27 и 28 (формирования координатных приращений) и на счетный вход триггера 25. Круговая интерполяция осуществляется по следующему алгоритму оценочной функции. При F (X.;, Z..-)0, т.е. когда точка находится на или вне окружности, шаг делается по координате X и новое значение оценочной функции вычисляется по фор.муле F(X,2j)-2Xi+1, При F(, Zу) О точка находится Внутри окружности, при этом Делается шаг по оси 2, а новое значение оценочной функции вычисляется по формуле F(X. ,Zj,,)F(,,. Реализация этого алгоритма имеетряд особенностей, существенно упрощающихся его схему, а именно: операция вычитания 2Х заменена сложением с дополнительным кодом X причем ЛР Х кругового интерполятора заносится в регистр 1 последовательно и сразу в дополнительном коде, что исключает громоздкий параллельный преобразователь прямого кода в дополнительный, разрядность блоков 1+9 кругового интерполято ра сокращена на -один, что значительно сокращает объем оборудования, исключает, необходимость сдвига кодов Х|,2;. для получения их двойных значений 2Х 22j или двойное суммирование, что повышает быстродействие и также уменьшает объ518ем оборудования, а удвоение разрядности величин X,-, Z, достигается подключением к младшему разряду сумматора 8 единичного выхода триггера 25, на счет- ный вход которого поступает каждый входной импульс аргумента. Так как логнческая функция триггера 25 совпадает с логической функцией сумматора при суммировании единиц, то такое включение триггера 25 эквивалентно увеличению на один разряд разрядности всех блоков 1+6, 8, 9, 44 и выполнению сдвигов .или повторных суммирований величин Х,- . Далее круговой интерполятор работает следующим образом. При положительном значении оценочной функции на выходе знакового разряда регистра -9 имеется нолЬу поэтому элемент И-28 закрыт, а элемент И 27 открыт единичным сигналом через элемент НЕ 10. Поэтому им пульс частоты пройдет .через элемент И 27 и поступит на выход интерполятора по координате X, причем по заднему фронту этого импульса, который воздейст- вует также на вход (С2) парал-пельной записи регистра 9, .запишется новое значение подинтегральной функции, откорректированное на величину, хранимую в регистре 1, т.е. на -2Х,-, так как блок 5 открыт выходным сигналом элемента НЕ 10. Выходной импульс элемента Н 27 поступит на вход параллельной записи (С2,) регистра 1 и произведет запись в него выходной комбинации сумматора 3, что эквивалентно уменьшению абсолютного значения величины Х в регистре 1 на единицу, т.е. образуя величи г/Х-...При отрицательном значении оценочной функции на выходе знакового разряда регист- ра 9 имеется единица, которая открывает -элемент И 28, формируя импульс по координате 2 , а так как по цепи элементов НЕ 7, 1О оказывается открытым блок 6, то оценочная функция корректируется на величину Z :, хранимую в регистре 2, и аналогично работе предыдущей координаты, выходной импульс координаты Z добавляет единицу к содержимому регистра 2, образуя величину Zj-fl, Таким образом, реализуется приведенный выше алгоритм круговой интерполяции. Если приращение выработано по координате X, то импульс с выхода элемента И 27 через элемент ИЛИ 42 поступит на счетный вход счетчика 39, что эквивалентно единичному шагу проекции точки дуги окружности А-8 от точки А в сторону точки Б (фиг. 3). При выработке приращения по координате Z импульс 9 .9 появляется на выходе элемента И 28,. Этот импупьс поступает на Р -вход триггера 37 и своим передним фронтом сбрасывает его в ноль, одновременно пройдя через элемент ИЛИ 41, поступает на вход с триггера 38 и своим задним фронтом сбрасывает его в ноль. В результате прекращается поДиача импульсов частоты на вход аргумента кругоього интерполятора через, элемент И 32. В момент переключения координаты 2 текущей точки 49 прямой и текущей точки 50, дуги равны (фиг. 3), а координаты X те кущих точек дуги приближаются друг к другу. Цикл работы повторяется, при это координаты 2 дуги и линии следят друг за другом, а по координате X дни. гаются навстречу друг другу. Цикл работы прекращается, когда дуга и окружност пересекутся в точке 55, что определяется по переполнению счетчика 39. Деиствительно, сумма координатных приращений по координате X в этот момент окажется равной д f. Сигнал переполнения счетчика 39 по ступает на R-вход триггера 36 и сбрасьгаает его в ноль, закрывая тем самым элемент И ЗО. Одновременно единичный сигнал появляется на входе элемента И 26 и, как только триггер 38 окаже.тся в нуле, на втором входе элементами 26 окажется единица и его выхоаной нулевой сигнал закроет элемент И 2 9 и отключит ге. нератор40. Цикл вычисления закончен. При этом искомые велигш,иы окажутся в регистрах 1 и 2, причем в регистре 1 окажется проекция л RX при и При ь регистре .2 наоборот. Элемент И 26 необходим ДЛЯ того, чтобы последний импульс по координате 2 , исходя из фиг. 3, формировался круговым интерполятором, так как первый импульс по этой координате формируется линейным интерполятором, .в противном случае проекция дК вычисляется с ошибкой на.один дискрет.. Блок 24 (фиг. 2) работает следующим образом. Сигнал Пуск нормализации ус танавливает триггер 45 в состояние , элемент И-НЕ 46 рткрывается и с его выхода частота генератора 48 начинает проходить, на сдвигающие входы регистров 17 и 18, коды в которых начинают сдвигаться. Это продолжается до тех . пор, пока единица не появится в старшем . разр1яде любого из регистров 17 и 18. Любая единица через элемент ИЛИ 47 сбрасывает триггер 45 в ноль. На этом нормализации заканчивается. 110,Преимуществами предлагаемого устройства являются повышение быстродействия, так как используется однотакт- ная схема работы интерпопяторой, время расчета не зависит от величины XH Z ц , а только от величины А R, благодаря действию выходных сигналов блока 23 угол oi (фиг. 3) всегда 45°, что также увеличивает быстродействие в 2 раза, объем электронного оборудования сокращается за счет того, Jкpyгoвoй интерполятор имеет разрядность поправки, а не поправки + один разряд а разрядность линейного интерполятора также может быть сведена До разрядности кругового, так как величи,на ошибки от неточности задания линии редуцируется пряUo пропорционально отношению л Р,,|„. или ЛРгпсях- тах (Что видно из фиг. 4. Действительно, для современных систем tncfx mcfx 1000О MM,4R|ncix f cлeдbвaтeльнo,(., 5ООО. Точность увеличивается в 50ОО раз, и, следовательно, разрядность линейного интерполятора может быть соответственно уменьшена без -потери точности, что не только уменьшает объем оборудования, но и позволяет повысить тактовую частоту, так как время суммирования уменьшается и, следовательно,возрастает быстродействие; дополнительно уменьшается время вычисления поправки и возрастают предельно допустимые скорости, на которых может работать система ЧПУ, в использовано такое устройство, что особенно важно при обработке участков с большой кривизной. Благодаря перечисленным преимуществам объем электронного оборудования по сравнению с известными решениями при-, близительно сокращается на 25%, быстродействие возрастает в 4-4,5 раза при сокращении точности, Формула изобретения Устройство для коррекции положения. резца на станке с программным управлением, содержащее генератор импульсов, -. счетчик, выход которого подключен к R-входу первого RS-триггера, последовательно соединенные блок первых Элемен- тов ИЛИ, первый комбинационный сумматор и первый буферный регистр, выход которого подключен к второму входу первого комбинационного сумматора, последовательно соединенные второй комбинационный сумматор, первый регистр сдви- га и блок первых элементов И и последо вательно соединенные третий комбинационный сумматор, второй регистр сдвига и блок вторых элементов И, выход которого и выход блока первых элементой И подключены к входам блока первых элементов ИЛИ, причем выходы первого и второго регистров сдвига подсоединены к входам второго и третьего комбинационный сумматоров соответственно, о т :л и ч а ю щ е е с я тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит блок сравнения счетный триггер, второй Б 5-триггер, ЭК триггер, поспедовательно соединенные третий элемент И, четвертый элемент И, пятый элемент И, второй буферный регистр, четвертый комбинационный сумматор, шестой элемент И, второй элемент ИЛИ и третий элемент ИЛИ, последовательно соединенные третий регистр сдвига и блок управления нормализацией, по следовательно соединенные четвертый регистр сдвига, пятый комбинационный сум матор, третий буферный регистр и седь мой элемент И, а также восьмой,девятый,десятый, одиннадцатый и двенадцатый элемен ты И, первый и второй элементы НЕ и четвертый элемент ИЛИ, выход которого подключен к счетному входу счетчика первый и второй входы - к выходам девятого и двенадцатого элементов И соответственно, а третий вход - к второму входу первого регистра сдвига и к выходу одиннадцатого элемента И, соединенного первым входом с входом второго элемента НЕ, с выходом первого элемента НЕ и с вторым входом блока первых элементов И, а вторым входом - с первым входом десятого элемента И, с вторым входом первого буферного регистра, с входом счетного триггера и с выхо дом восьмого элемента И, связанного первым входом с выходом четвертого элемента И, вторым входом - с прямым выходом JK -триггера, инверсный выход которого подключен к первому входу третьего и к второму входу пятого эле ментов И, С-вход - к выходу третьего элемента ИЛИ, а J и К-входы - к прямому и инверсному выходам соответствен но второго 1 5-триггера, соединенного 5-входом с выходом второго элемента ИЛИ, а R-входом с вторым входом третьего элемента ИЛИ, с вторым вхоДОМ, второго регистра сдвига и с выходом иесятбго элемента И, второй ход которого подключен к второму выходу первого буферного регистра и к входу первого элемента НЕ, входы блока сравнения соединены с задающими входами устройства и с установочными входами третьего и четвертого регистров сдвига, первый выход - с вторым входом седьмого и с первым входом двенадцатого элементов И, а второй выход - с вторым входом шестого и с первым входом девятого элементов И, управдяющие входы третьего и четвертого .регистров сдвига подсоединены к выходу блока управления нормализацией,, второй вход которого связан с вторым выходом четвертого регистра сдвига и с вторым входом пятрго комбинационного сумматора, подключенного третьим входом к выходу третьего буферного регистра, а вторым выходом к третьему входу седьмого и к второму входу девятого элементов И, второй вход второго буферного регистра соединен,с вторым выходом четвертого комбинационного сумматора, а первый вход - с третьим входом шестого и с вторым входом двенадцатого элементов И и с вторым выходом третьего буферного регистра, второй и третий входы четвертого комбинационного сумматора подключены соответственно к первому и второму выходам третьего регистра сдвига, а первый выход - к третьему входу двенадцатого элемента И, выход счетного триггера связан с третьим входом первого комбинационного сумматора, прямой и инверсный выходы первого триггера соединены соответственно с третьим входом пятого и с вторым входом третьего элементов И, второй вход второго элемента ИЛИ подключен к выходу седьмого элемента И, а выход генератора импульсов связан с вторым входом четвертого элемента И. Источники информации, принятые во внимание при экспертизе 1.Левин Б. Н. и Мальчик А. Ю. Методы автоматического расчета эквиваленты. Сб. Способы подготовки программ и интерполяторы для контурных систем числового управления станками. М., Машиностроение, 1970, с. 139-142. 2.Авторское свидетельствоСССР № 591822, кл. Q 05 В 19/18, 1974 (прото.тип).

Пуск H0/№t

Импульсы

f/6

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интерполятор | 1986 |

|

SU1310778A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Устройство для задания программы обработки в полярных координатах | 1987 |

|

SU1409974A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Цифровой интерполятор | 1981 |

|

SU1003022A1 |

| Устройство для программного управления захватом автооператора | 1982 |

|

SU1233103A1 |

| Круговой интерполятор | 1985 |

|

SU1359772A1 |

| Линейно-круговой интерполятор | 1978 |

|

SU807236A1 |

| Линейный интерполятор | 1986 |

|

SU1413603A1 |

Авторы

Даты

1982-12-23—Публикация

1981-06-18—Подача