динены с первыми выходами блоков про- дд коммутаторов соединены с выходами межуточных вычислений, управляющие входы блоков промежуточных вычислений соединены с вторым выходом блока управления, каждый блок промежуточных

соответствующих узлов инверсии и с вторыми входами соответствующих сх сравнения, выходы первой и второй схем сравнения соединены с управля

коммутаторов соединены с выходами

соответствующих узлов инверсии и с вторыми входами соответствующих схем сравнения, выходы первой и второй схем сравнения соединены с управляющи

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для моделирования разделительной операции процесса обогащения полезных ископаемых по дискретной сепарационной характеристике | 1989 |

|

SU1667092A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Вычислительное устройство для формирования маршрута сообщения | 1982 |

|

SU1037269A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

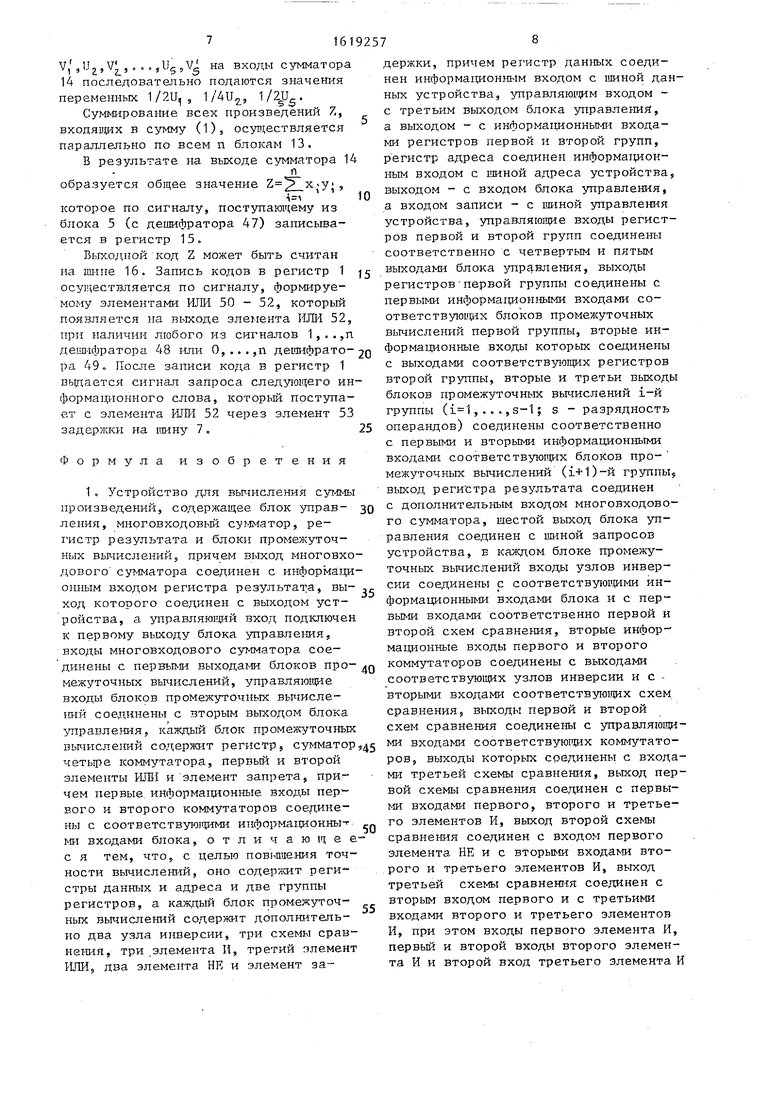

Изобретение относится к вычислительной технике и может быть использовано в специализированных устройствах цифровой обработки инЛормации. Целью изобретения является повышение точности вычислений. Устройство содержит регистр 1 данных, шину 2 данных, регистр 3 адреса, шину 4 адреса, блок 5 управления, шину 6 управления, шину 7 запроса, группу 8 регистров 9, группу 10 регистров 11, группы 12 блоков 13 промежуточных вычислений, много- входовый сумматор 14, регистр 15 результата, выход 16. 1 э.п, ф-лы, 3 ил, 2 табл. (Л

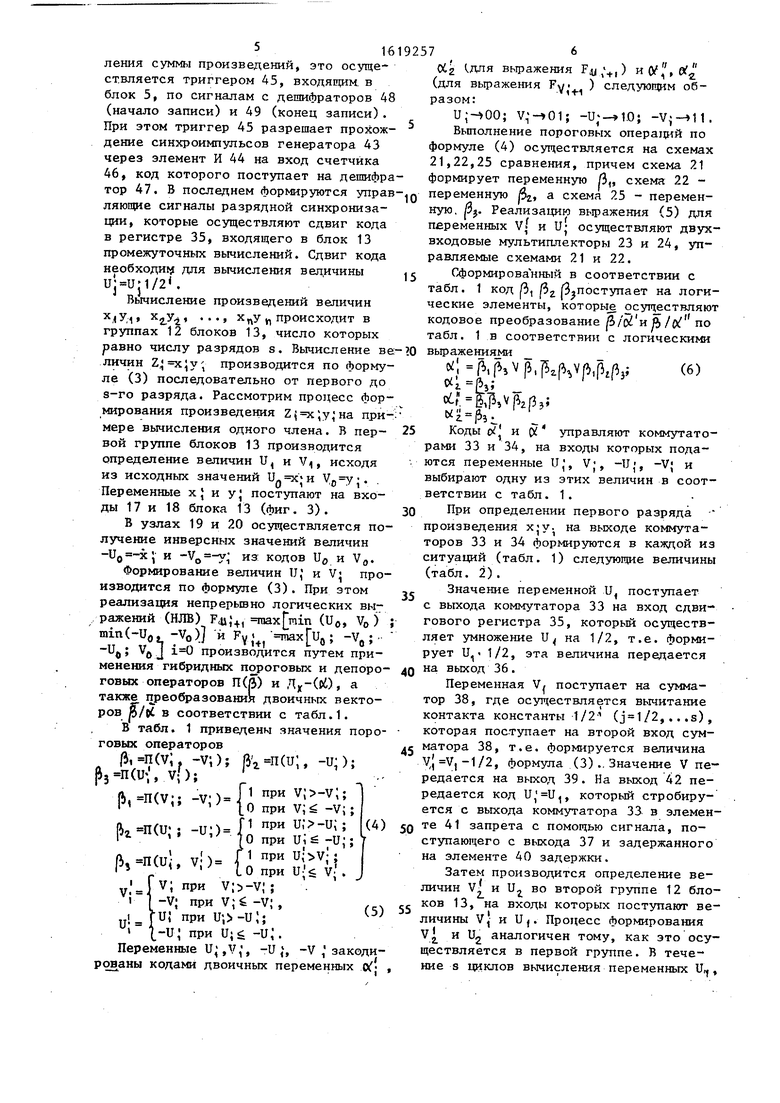

вычислений содержит регистр, сумматор, входами соответствующих коммутаточетыре коммутатора, первый и второй элементы ИЛИ и элемент запрета, причем первые информационные входы первого и второго коммутаторов соединены с соответствующими информационны--- ми входами блока, отличающее с я тем, что, с целью повышения точности вычислений, оно содержит регистры данных и адреса и две группы регистров, а каждый блок промежуточных вычислений содержит дополнительно два узла инверсии, три схемы сравнения, три элемента И, третий элемент ИЛИ, два элемента НЕ и элемент за0

5

ров, выходы которых соединены с входами третьей схемы сравнения, выход первой схемы сравнения соединен с первыми входами первого, второго и третьего элементов И, выход второй схемы сравнения соединен с входом первого элемента НЕ и с вторыми входами второго и третьего элементов И, выход третьей схемы сравнения соединен с вторым входом первого и с третьими входами второго и третьего элементов И, при этом входы первого элемента И, первый и второй входы второго элемента И и второй вход третьего элемента И

являются инверсными, выход первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, выход первого элемента ПЕ соединен с вторым входом второго элемента ИЛИ и с входом второго элемента НЕ, выходы второго и третьего элементов И соединены с соответствующими входами первсг

го элемента ИЛИ, выход которого соеди-jQ нен с выходом триггера, а выход - со

нен с первым управляющим входом третьего коммутатора, второй управляющий вход которого соединен с выходом третьей схемы сравнения, выход второго

элемента ИЛИ соединен с первым управ- j тальные - с вторым выходом блока и с

ляющим входом четвертого коммутатора, второй управляющий вход которого соединен с выходом второго элемента НЕ, первые, вторые, третьи и четвертые информационные входы третьего и чет- вертого коммутаторов попарно соединены с входами и выходами первого и второго узлов инверсии, выход третьего коммутатора соединен с информационным входом регистра и первым входом эле- мента запрета, второй вход которого соединен с выходом элемента задержки, а выход - с первым выходом блока промежуточных вычислений, третий выход которого соединен с выходом регистра, вход сдвига которого соединен с входом элемента задержки и с входом бло- ка, выход четвертого коммутатора сое

динен с первым входом сумматора, второй вход которого соединен с входом константы устройства, а выход - с вторым выходом блока.

1 -v;«Ј -и; 6U,- v;

и;

925710

ход которого соединен с шестым выходом блока, последний выход третьего дешифратора соединен с обнуляющим

входом счетчика.

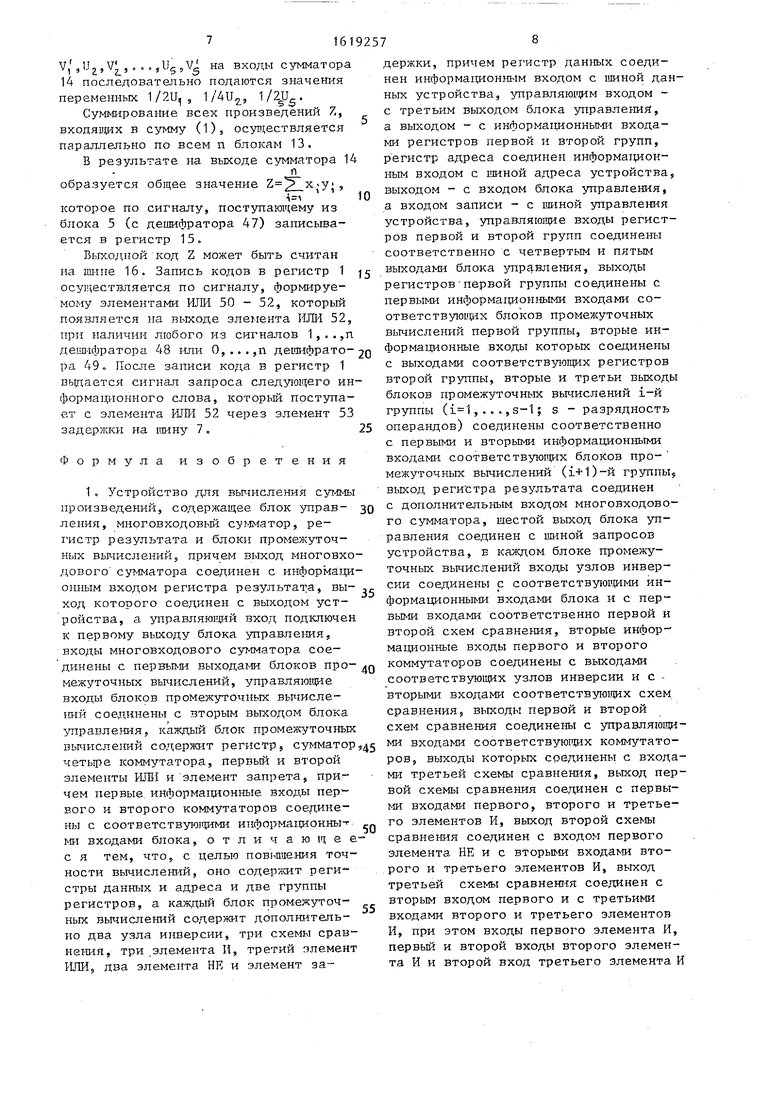

Таблица 1

Фю.г

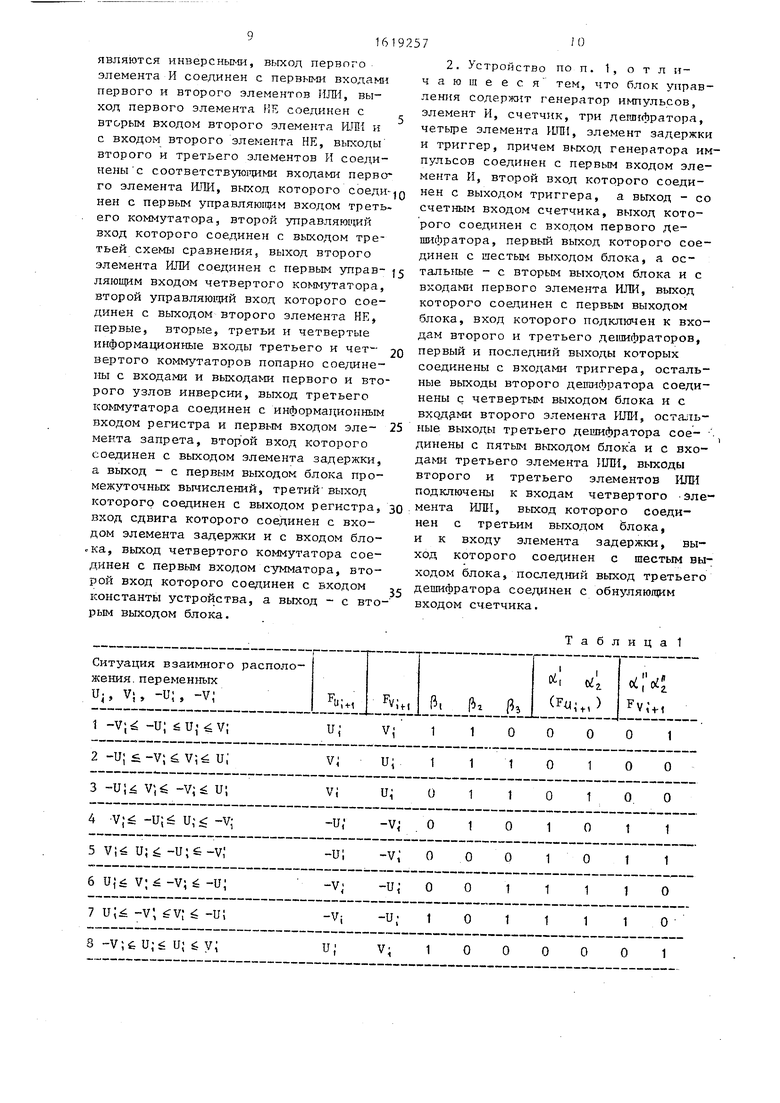

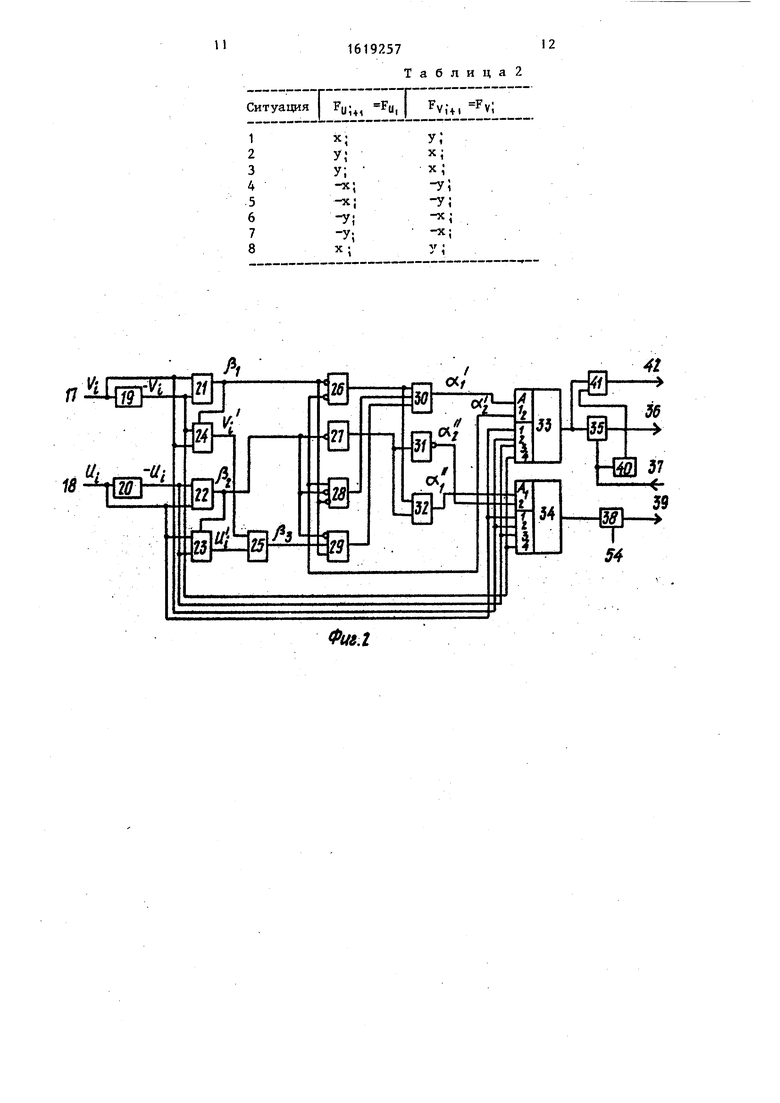

Таблица2

Фиг.З

| Рабинер Л., Гоулд Б | |||

| Теория и применение цифровой обработки сигналов | |||

| - М.: Мир, 1979, с | |||

| ШПАЛОРЕЗНЫЙ СТАНОК | 1922 |

|

SU607A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления суммы произведений | 1985 |

|

SU1283754A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-02-22—Подача