Изобретение относится к вычислительной технике, в частности к устройствам вычисления функций, и может быть использовано в ЭВМ, в качестве сопроцессора для вычисления функций или

как самостоятельное устройство в системах цифрового автоматического управления.

Целью изобретений является упроше- |ние преобразователя.

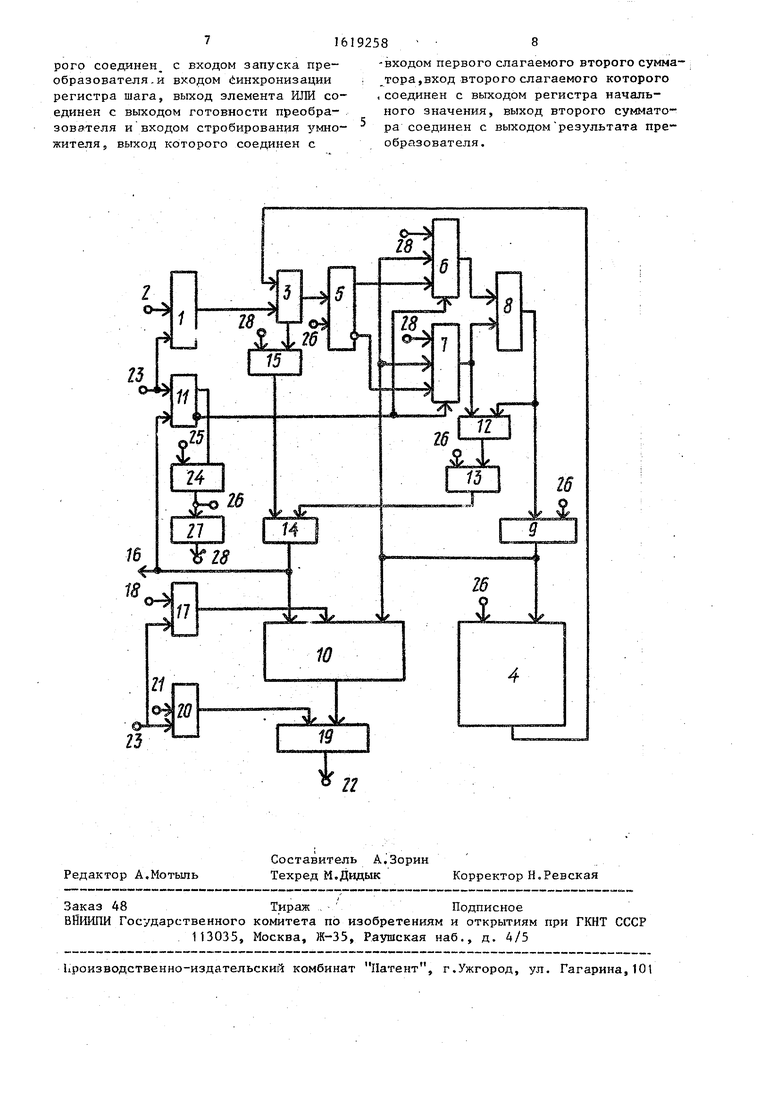

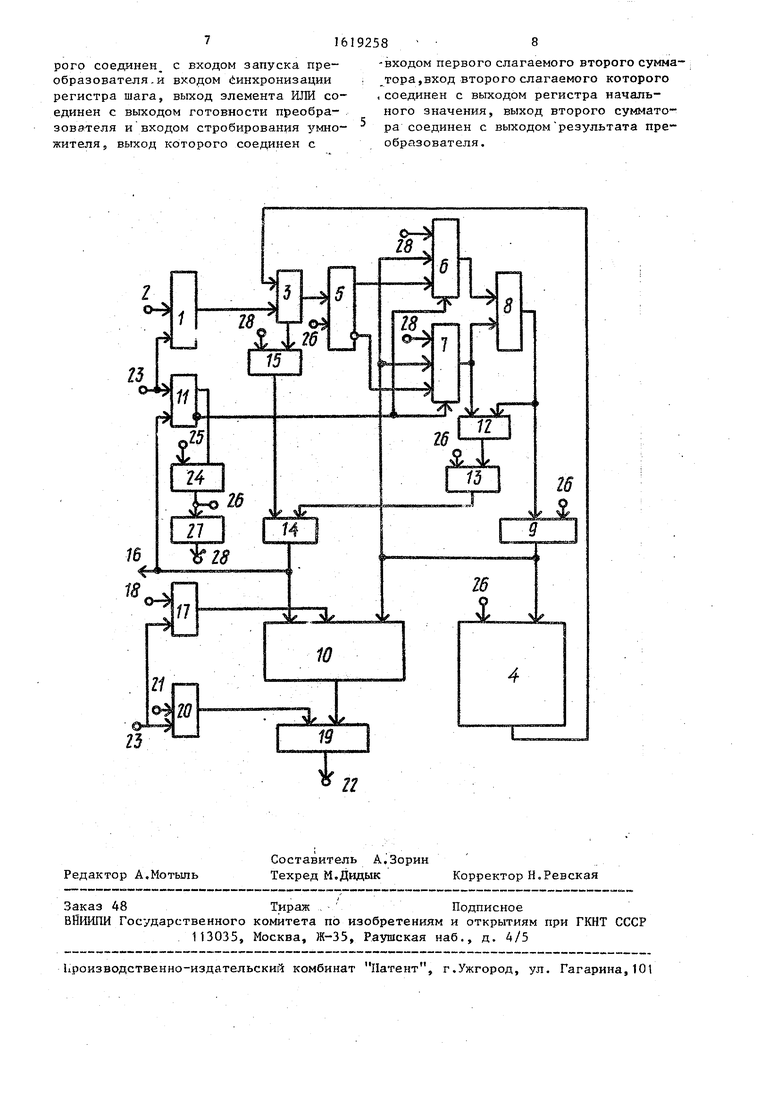

На чертеже представлена блок-схема преобразователя.

Функциональный преобразователь содержит регистр 1 аргумента, вход 2 аргумента, схему 3 сравнения., блок 4 памяти, триггер 5, регистр 6 верхней границы, регистр 7 нижней границы, сумматор 8, регистр 9 последовательных приближений, умножитель 10, триггер 11 схему 12 сравнения, элемент И 33, элемент ИЛИ 14, элемент И 15, выход 16 готовности, регистр 17 шага, вход 18 задания шага квантования, сумматор 19, регистр 20 началь- ноге значения, вход 21 начальных условий, выход 22 результата, вход 23 запуска, элемент И 24, тактовый вход 25, выход 26 элемента И 24, элемент 27 задержки, выход 28 элемента задержки.

Преобразователь работает следующим образом.

В исходном состоянии в блоке 4 памяти записаны дискретные значения ар- гумента, причем квантование выполнено таким образом, что интервалы между двумя соседними значениями функции одинаковы. Второй триггер 11 находится в нулевом состоянии, все разряды регистра 6 верхней границы в единичном состоянии, все разряды регистра 7 нижней границы в нулевом состоянии.

При необходимости вычисления функции на вход 2 подается код аргумента, на вход 18 задания шага квантования - код шага квантования функции, на вход 21 - код начального значения функции. Одновременно на вход 23 запуска подается сигнал, по которому указанные коды с входов 2,18,21 записываются соответственно в регистр 1 аргумента, регистр 17 шага и регистр 20 начального значения, а также производится установка второго триггера 11 в единичное состояние. Сигнал с прямого выхода второго триггера 11 открывает третий элемент И 24 для прохождения синхронизирующих импульсов с тактового входа 25 на регистр 9 последовательных приближений, первый триггер 5, а также на элемент 27 задержки, с выхода которого синхроимпульсы поступают на регистры

верхней 6 и нижней 7 границ. Под действием синхроимпульсов среди кодов, хранящихся та блоке 4 памяти, реализуется поиск ближайшего меньшего к аргументу поиска, зафиксированного

Q Q

5

0

0

5

0

5

5

на регистре 1 аргумента. Указанный поиск осуществляется последовательным выделением интервала, заключающего в себе искомый код, причем на каждом шаге величина упомянутого интервала уменьшается вдвое. Адреса, по которым хранятся в первом блоке 4 памяти верхняя и нижняя границы интервала, фиксируются соответственно на регистрах 6 и 7. В каждом такте адреса с указанных регистров 6 и 7 поступают на входы первого сумматора 8, код с выхода которого со сдвигом на один разряд вправо фиксируется на регистре 9 последовательных приближений. Таким образом, на регистре 9 последовательных приближений оказывается записанным адрес,делящий интервал, заключенный между адресами нижней и верхней границ, пополам. Код аргумента, считанный с блока 4 памяти, поступает на первую схему сравнения, где сравнивается с кодом аргумента, заданного на регистре 1. Если считанный код совпадает с кодом поступившего аргумента, то на выходе признака равенства первой схемы 3 сравнения формируется единичный сигнал, который свидетельствует о том, что искомое ближайшее найдено, а его адрес зафиксирован на регистре 9 последовательных приближений,

Если считанный код меньше кода поступившего аргумента (на выходе признака неравенства схемы 3 сравнения при этом формируется нулевой сигнал), то искомый ближайший меньший к заданному код хранится в интервале адресов на регистрах 6 и 9, в противном случае - на регистрах 9 и 7. Соответственно, в первом случае триггер 5 установится в нуль и производится прием информации из регистра 9 на регистр 7 нижней границы, а во втором триггер 5 устанавливается в единицу и по сигналу с его прямого выхода информация из регистра 9 записывается на регистр 6 верхней границы. Причем переброс триггера 5 осуществляется по заднему фронту синхроимпульса, а запись информации в регистры 6 или 7 осуществляется по заднему фронту сдвинутого синхроимпульса.

Описанная процедура повторяется до тех пор, пока на выходе признака равенства первой схемы 3 сравнения не будет сформирован сигнал единичного уровня, либо содержимое регистра 9

516

последовательных приближений не сравняется с содержимым регистра 7 | нижней границы, т.е. пока на выходе признака равенства первой схемы 3 сравнения либо второй схемы 12 срав- нения не появится единичный сигнал, который через элементы И 15 и 13 соответственно поступает на входы элемента ИЛИ 14, который инициирует начало работы умножителя 10, на выходе которого формируется произведение кода шага квантования функции, хранящегося на регистре 17 шага, на адрес, по которому в блоке 4 памяти хранения ближайшее меньшее к заданному аргументу, зафиксированный на регистре 9 последовательных приближений. Указанное произведение с выхода умножителя 10 поступает на вход второго сумматора 19, где к нему прибавляется код начального значения функции, хранящегося на регистре 20 начального значения. Таким образом на выходе второго сумматора 19 и на выходах 22 результата устройства формируется код значения функции, соответствующий аргументу из блока 4 памяти, т.е. ближайшему меньшему или равному заданному аргументу. Одновременно с этим сигнал с выхода элемента ИЛИ 14 поступает на выход 16 готовности устройства, свидетельствуя о том, что вычисление функции закончено, а также на вход сброса триггера 11, по нулевому сигналу с выхода которого схема приходит в исходное состояние.

Формула изобретения

Функциональный преобразователь, содержавший регистр аргумента, два триггера, три элемента И, элемент ИЛИ, элемент задержки, две схемы сргв нения, регистр нижней границы, регистр верхней границы, первый сумматор, регистр последовательных приближений и блок памяти, причем вход аргумента устройства соединен с информационным входом регистра аргумента, выход которого соединен с первым входом первой схемы сравнения, выход признака неравенства которой соединен с информационным входом первого триг- гера, прямой и инверсный выходы которого соединены с входами разрешения записи соответственно регистра верхней границы и регистра нижней грани

20

25

дд

„

92586

цы, выходы которых соединены с входами соответственно первого и второго операндов первого сумматора, выход которого со сдвигом на один разряд сое- динен с первым входом второй схемы

сравнения и информационным входом регистра последовательных приближений, выход которого соединен с адресным

Ю входом блока памяти и информационными входами регистров верхней границы и нижней границы, выход регистра, нижней границы соединен с вторым входом второй схемы сравнения, выход коt5 торой соединен с первым входом первого элемента И, выход которого подключен к первому входу элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с выходом признака равенства первой схемы сравнения, второй вход которой соединен с выходом блока памяти, выход элемента ИЛИ соединен с входом установки в О второго триггера, вход установки в I которого соединен с входом запуска устройства и входом синхронизации ре- гистрг аргумента, инверсный выход второго триггера соединен с входом установки в О регистра нижней границы и входом установки в 1 регистра верхней границы, прямой выход второго триггера соединен с первым входом третьего элемента И, второй вход которо,с го соединен с тактовым входом преобразователя, выход третьего элемента И соединен с входами синхронизации первого триггера, регистра последовательных приближений, блока памяти, вторым входом первого элемента И и входом элемента задержки, выход которого соединен с входами синхронизации регистра верхней границы, регистра нижней границы и вторым входом второго

45 элемента И, отличающийся тем, что, с целью упрощения, он содержит умножитель, регистр шага, регистр начального значения и второй сумматор, причем выход регистра последо5Q вательных приближений соединен с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходом регистра шага, информационный вход которого соединен с с входом задания шага квантования преобразователя} вход задания начальных условий которого соединен с информационным входом регистра начального значения, вход синхронизации кото30

16

рого соединен с входом запуска преобразователя, и входом синхронизации регистра шага, выход элемента ИЛИ со единен с выходом готовности преобразователя и входом стробирования умно жителя, выход которого соединен с

192588

-входом первого слагаемого второго сумматора,вход второго слагаемого которого

,соединен с выходом регистра начального значения, выход второго сумматора соединен с выходом результата преобразователя.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| Функциональный преобразователь | 1987 |

|

SU1508207A1 |

| Функциональный преобразователь | 1989 |

|

SU1709303A1 |

| Функциональный преобразователь | 1988 |

|

SU1587500A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функций | 1985 |

|

SU1280391A1 |

| Интерполятор функций двух аргументов | 1984 |

|

SU1247893A1 |

| Устройство для воспроизведения функций | 1986 |

|

SU1348828A1 |

| Генератор функций | 1984 |

|

SU1241219A1 |

| Устройство для воспроизведения функций | 1990 |

|

SU1734102A1 |

Изобретение относится к вычислительной технике, в частности к устройствам вычисления функций, и может быть использовано в ЭВМ в качестве сопроцессора для вычисления произвольных функций или как самостоятельное устройство в системах цифрового автоматического управления. Целью изобретения является упрощение преобразователя. Использование предлагаемого функционального преобразователя позволяет сократить аппаратурные затраты путем уменьшения необходимого объема постоянной памяти. Функциональный преобразователь содержит регистр аргумента, входом которого является информационный вход устройства, первую схему сравнения, блок памяти, пер- вый триггер, регистр верхней границы, регистр нижней границы, первый сумматор, регистр последовательных приближений, умножитель, второй триггер, вторую схему сравнения, первый элемент И, элемент ИЛИ, второй элемент И, выход готовности устройства, регистр шага, информационным входом которого является вход задания шага квантования, второй сумматор, регистр начального значения, информационным входом которого является вход задания начального значения, выход результата устройства, вход запуска устройства, третий элемент И, первым входом которого является тактовый вход устройства, элемент задержки. Сущность работы устройства состоит в том, что вычисление функции осуществляется с использованием таблицы аргументов, хранящейся в памяти, причем опорные значения аргументов, содержащиеся в таблице, соответствуют значениям функции, отличающимся на фиксированную константу. Отыскание номера табличного значения аргумента, ближайшего к заданному, осуществляется биларным поиском, а определение значения функцию-умножением найденного номера на константу. 1 ил. .ч. СО ю ел 00

I

22

| Цифровой функциональный преобразователь | 1986 |

|

SU1374218A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Функциональный преобразователь | 1987 |

|

SU1508207A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-01-07—Публикация

1988-10-17—Подача