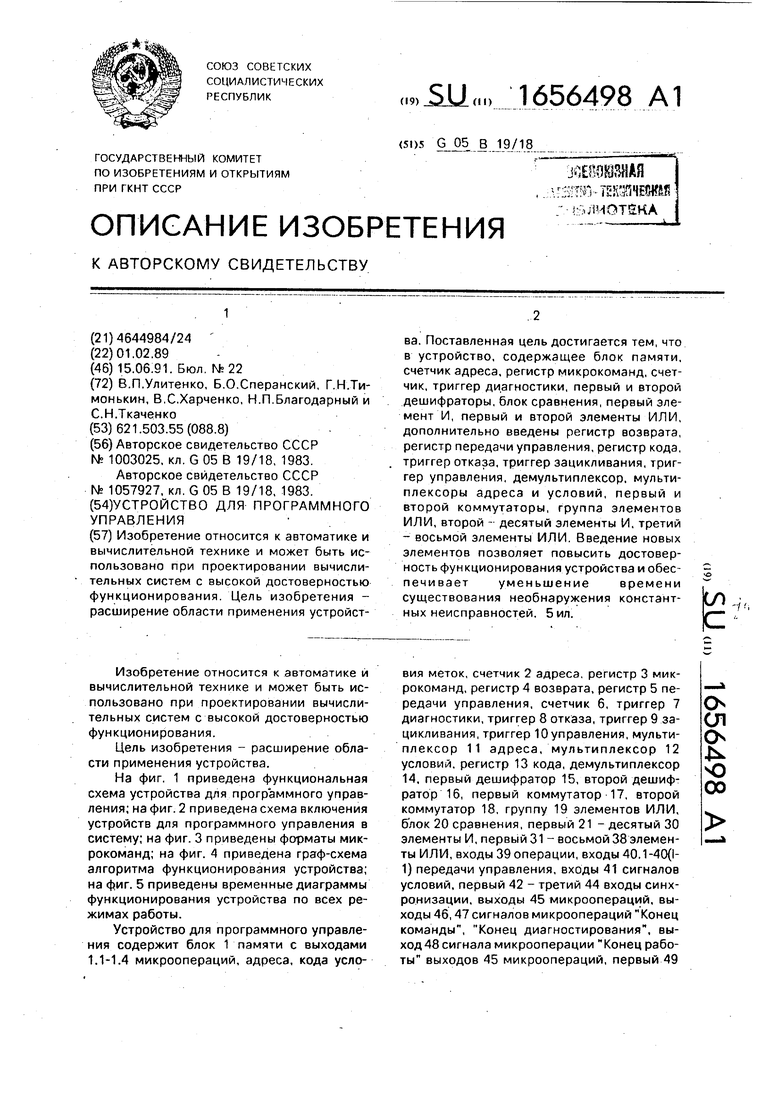

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных систем с высокой достоверностью функционирования.

Цель изобретения - расширение области применения устройства.

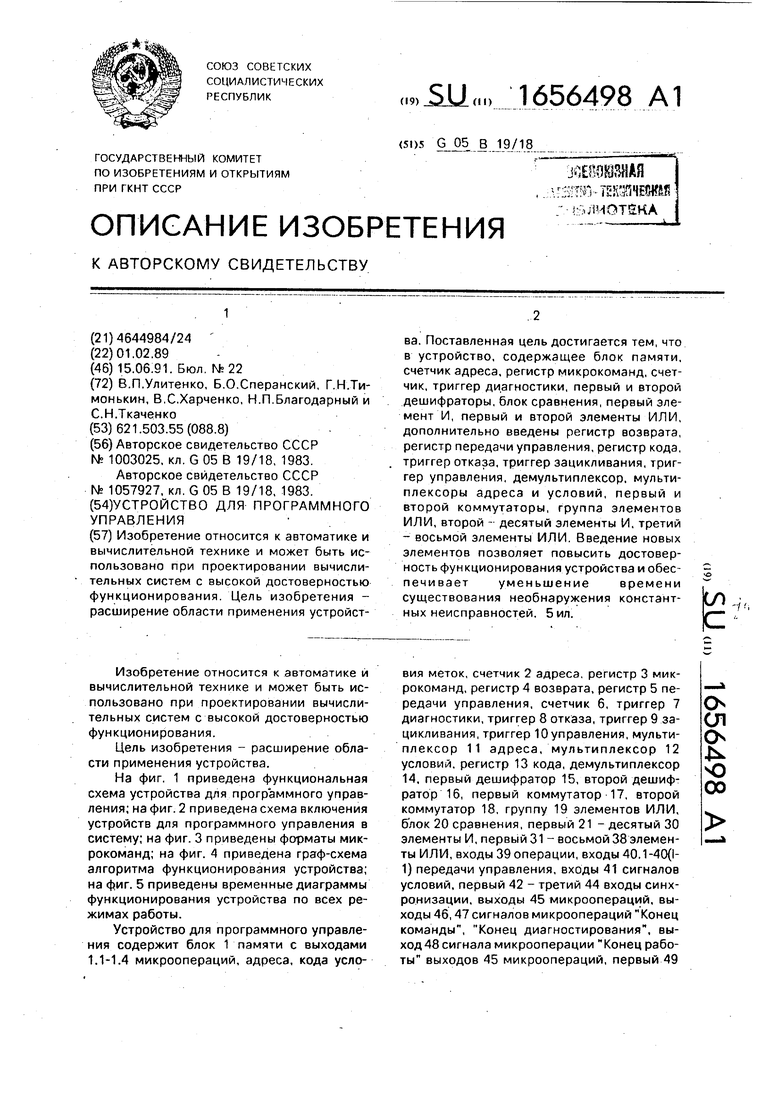

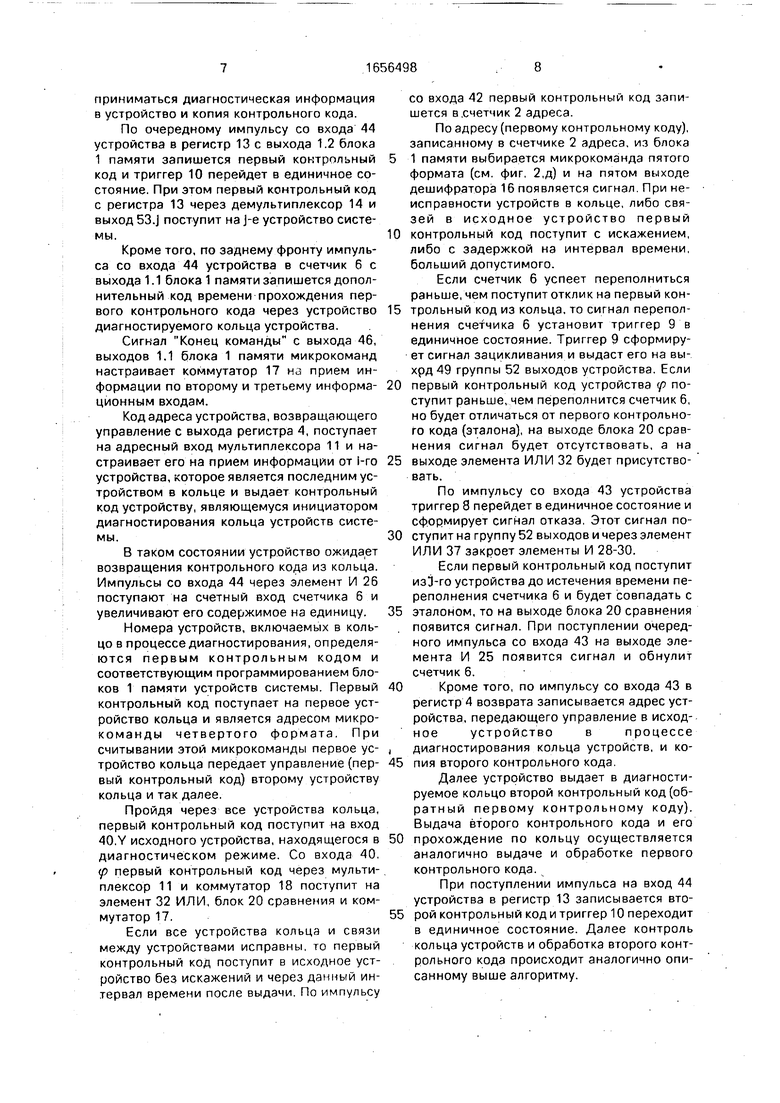

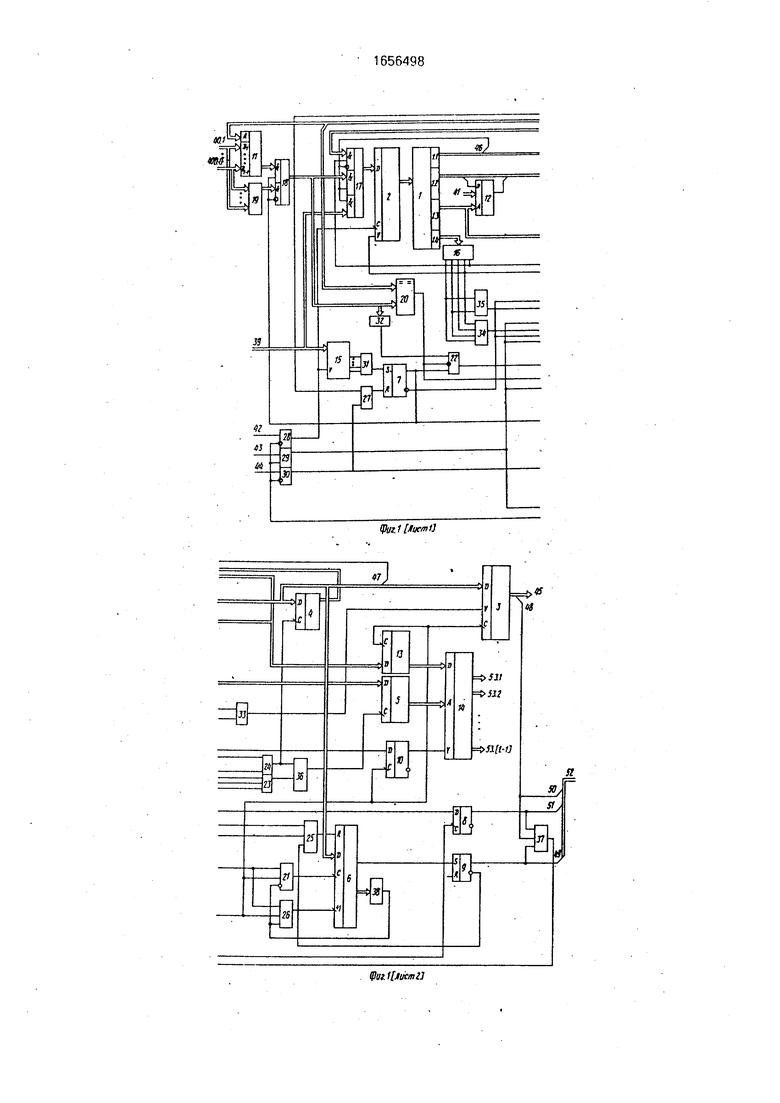

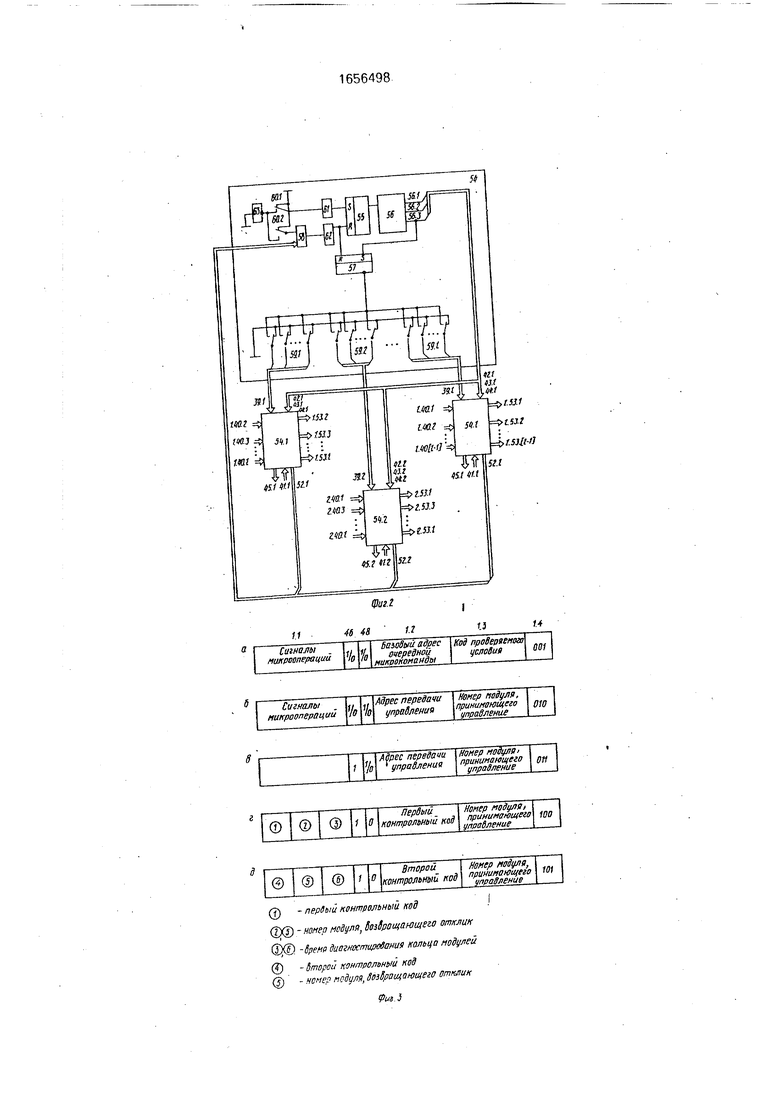

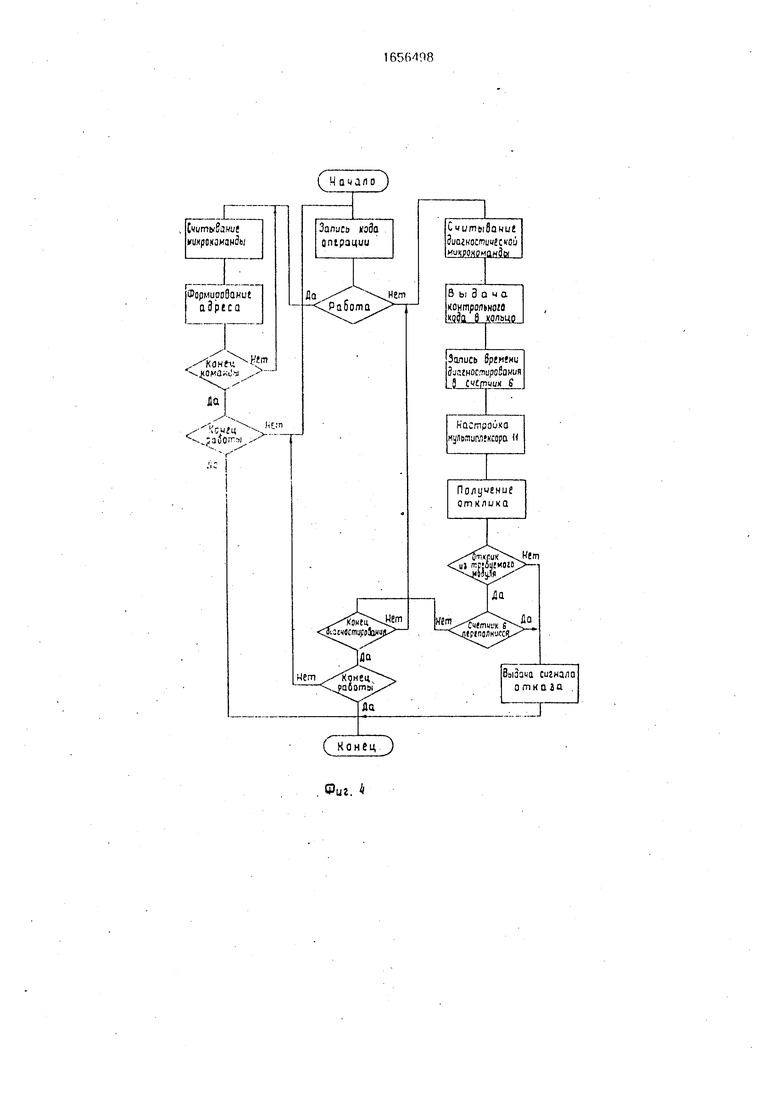

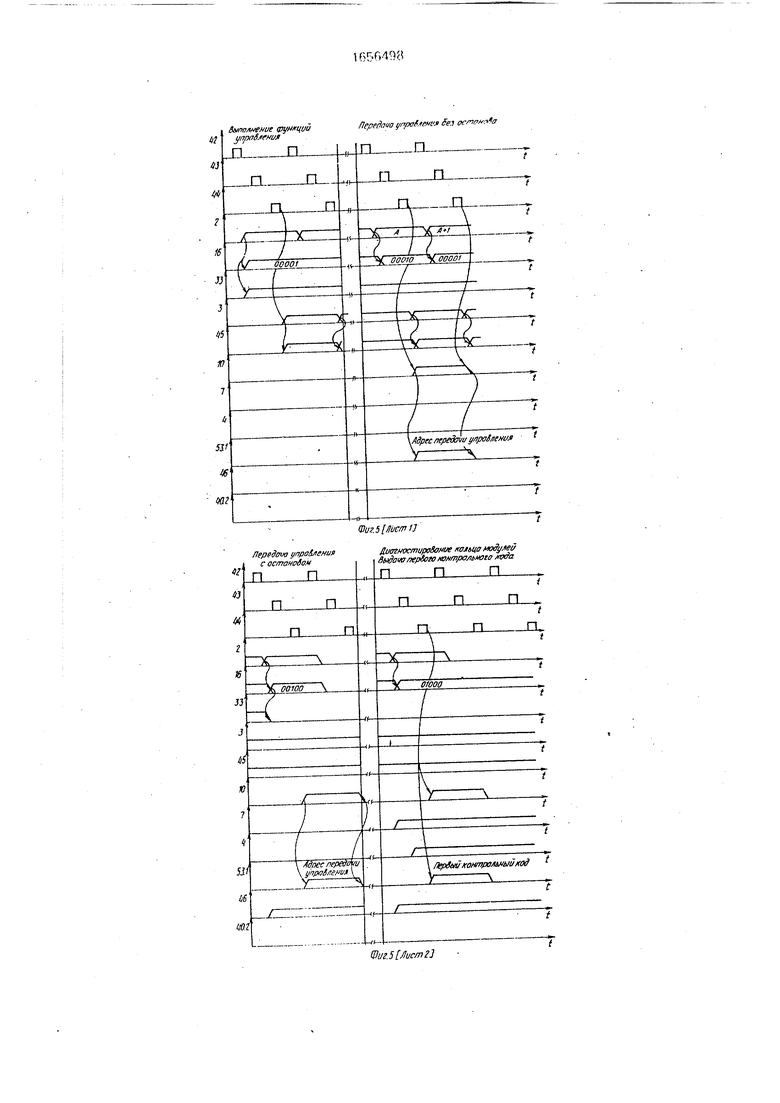

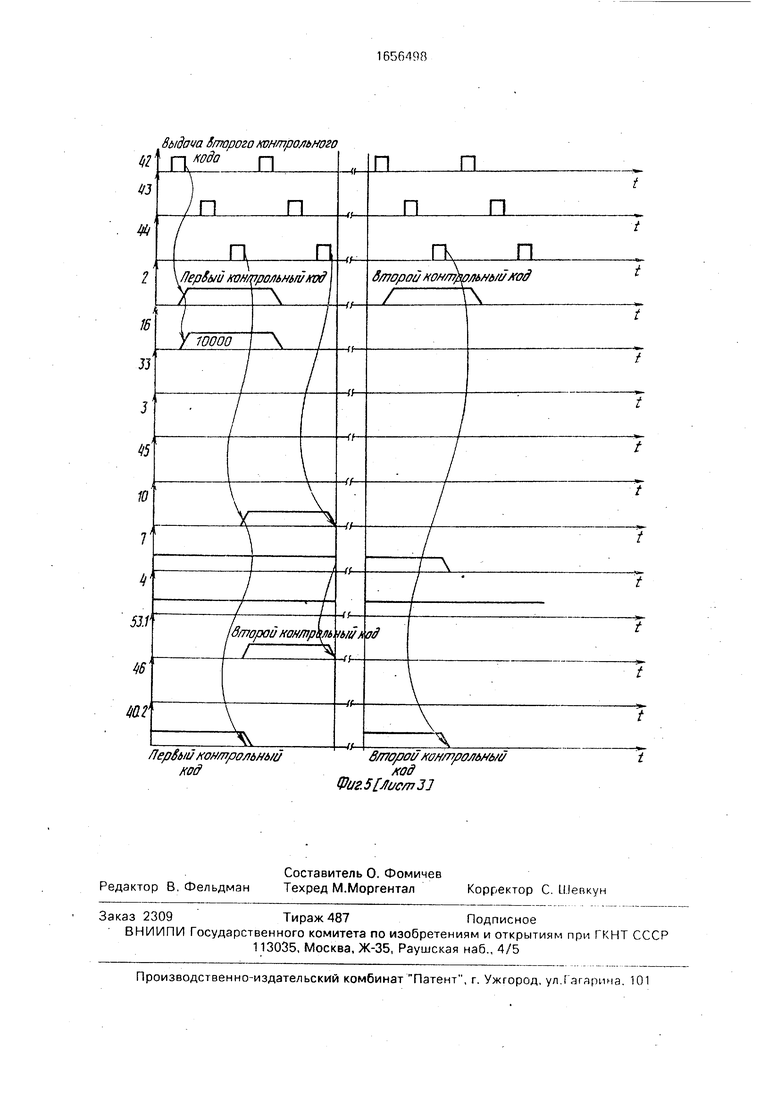

На фиг. 1 приведена функциональная схема устройства для программного управления; на фиг. 2 приведена схема включения устройств для программного управления в систему; на фиг. 3 приведены форматы микрокоманд; на фиг. 4 приведена граф-схема алгоритма функционирования устройства; на фиг. 5 приведены временные диаграммы функционирования устройства по всех режимах работы.

Устройство для программного управления содержит блок 1 памяти с выходами 1.1-1.4 микроопераций, адреса, кода условия меток, счетчик 2 адреса, регистр 3 микрокоманд, регистр 4 возврата, регистр 5 передачи управления, счетчик 6, триггер 7 диагностики, триггер 8 отказа, триггер 9 зацикливания, триггер 10 управления, мультиплексор 11 адреса, мультиплексор 12 условий, регистр 13 кода, демультиплексор 14, первый дешифратор 15, второй дешифратор 16, первый коммутатор 17, второй коммутатор 18, группу 19 элементов ИЛИ, блок 20 сравнения, первый 21 - десятый 30 элементы И, первый 31 - восьмой 38 элементы ИЛИ, входы 39 операции, входы 40.1-40(1- 1) передачи управления, входы 41 сигналов условий, первый 42 - третий 44 входы синхронизации, выходы 45 микроопераций, выходы 46,47 сигналов микроопераций Конец команды, Конец диагностирования, выход 48 сигнала микрооперации Конец работы выходов 45 микроопераций, первый 49

О

ел о

ю оо

- третий 51 выходы, составляющие группу 52 осведомительных выходов, первый (1-1)-й выходы 53.1-53.(1-1) передачи управления

На фиг. 2 приведен пример объединения I устройств для программного управления в систему, где использованы следующие обозначения: 54 - блок верхнего уровня управления, 54.1,54.2,54 I- соответственно первый, второй и 1-й устройства.

Входы и выходы модульного устройства 54.1 - 1.53.2, 1.53.3, 1.53.1- выходы передачи управления соответственно на второй, третий и 1-й модульные устройства, 1.40.2, 1.40.3, 1.40.1 - входы передачи управления со второго, третьего и 1-го модульных устройств, 39.1 - вход кода операции, 41.1 - вход сигналов условий, 45.1 - выход микроопераций, 52.1 - группа осведомительных выходов, 42.1, 43.1, 44.1 - входы первой- третьей последовательности импульсов.

Входы и выходы модульных устройств 54.2, 54.1 имеют аналогичные назначения.

Блок 54 содержит триггер 55 пуска, генератор 56 с выходами 56.1-56.3 первой- третьей последовательностей импульсов, триггер 57 сигнала, элемент ИЛИ 58, группы 59.1-59.1 переключателя кодов операций, переключатель 60.1 запуска системы, переключатель 60.2 останова системы, первый и второй одновибраторы 61, 62, элемент НЕ 63.

Устройство для программного управления функционирует в двух режимах

-рабочий режим,

-режим диагностики.

В исходном состоянии все регистры и триггеры устройства находятся в нулевом состоянии.

Рабочий режим. В этом режиме устройство может работать в одном из подрежимов:

-выполнение функций управления,

-передача управления без останова;

-передача управления с остановом

В исходном состоянии на выходе 46 блока 1 памяти присутствует единичный сигнал Конец команды.

Коммутатор 17 открыт для приема адреса обращения к блоку 1 памяти от соседних устройств или от верхнего уровня управления (со входа 39 операций).

Выполнение функций управления

Адрес первой микрокоманды поступает либо со входа 39 кода операции, либо по одному из входов 40.1-40(1-1) от устройств системы передающих управление данному устройству. Предполагается, что в каждый отдельный момент времени передавать управление может только одно устройство системы Со входа 40 i (i 1 1-1) адрес

передачи управления пройдет через эле менты ИЛИ группы 19 и коммутаторы 18 и 17 на информационный вход счетчика 2 адреса Со входа 39 (при запуске устройства с

верхнего уровня управления) код операции пройдет через коммутатор 17 на информа ционный вход счетчика 2 адреса По заднр му фронту импульса, поступающего на вход 42 устройства, адрес первой микрокоманды

0 микропрограммы запишется в счетчик 2 адреса.

С выхода 1.1 блока 1 памяти коды микроопераций микрокоманды первого формата (см. фиг. 2,а) поступают на

5 информационный вход регистра 3 микроко манд Сигнал на выходе 46 блока 1 памяти исчезает. Базовый адрес очередной микрокоманды с выхода 1.2 блока 1 памяти посту пает на формирователь адреса очередной

0 микрокоманды, состоящей из мультиплексора 12 и коммутатора 17

Младший (модифицируемый) разряд ад реса с выходов 1.2 блока 1 памяти поступает на первый информационный вход мульти5 плексора 12. На другие информационные входы мультиплексора 12 поступают сигналы логических условий от объекта управления чер-ез вход 41 логических условий устройства. Код проверяемого логического

0 условия с выхода 1 3 блока 1 памяти поступает на адресный вход мультиплексора 12 На выход мультиплексора 12 поступает либо значение младшего разряда кода адреса с выходов 1.2 блока 1 памяти, если в процессе

5 выполнения текущей микрокоманды выполнение логических условий не проверяется либо значение проверяемого логического условия.

Код номера формата микрокоманды с

0 выхода 1.4 блока 1 памяти поступает на дешифратор 16 формата микрокоманды При этом на первом выходе дешифратора 16 по является сигнал разрешающий запись сигналов микроопераций (по за днему фронту

5 импульса с входа 44 устройства) в регистр 3 микрокоманд, а также передачу адреса оче редной микрокоманды через коммутатор 17 на счетчик 2 адреса. Сигналы микроопераций с регистра 3 через выходы 45 поступают

0 на объект управления. По заднему фронту очередного импульса со входа 42 устройства в счетчик 2 адреса запишется адрес второй микрокоманды. Далее устройство в этом режиме будет функционировать анало5 гично описанному выше алгоритму При проявлении на выходе 46 блока 1 памяти сигнала микрооперации Конец команды коммутатор 17 закрывается по первому информационному входу и открывается по второму и третьему информационным входам

. tOl (.ИГНЛЛ ГДеПЛСГ ПО М ЧЧ НММ ПОП

учение слрдующего адррга обр inn иич к блоку 1 памяти от соседни устройств (при передаче управления) или от порхнет уров- нч управления.

При появлении (в прочее се фунщиони рованич устройства) на выходе 48 регистра 3 сигнала Конец работы элементы 28-30 И закрываются и импульсы со входов 42-44 на элементы устройства не поступают На вы ходе 50 группы 52 осведомительных выходов появляется единичный сигнал

Передача управления без останова

В этот режим устройство из режима Выполнение функций упрапления при выборке из блока 1 памяти микрокоман ды второго формата (см. фиг 2 б)

Адрес обращения к блоку 1 памяти устройства, которому передается управление с выхода 1 2 блока 1 памяти поступает на информационный вход регистра 13 Номер устройства, которому передастся управление, с выхода 1.3 блока 1 памяти подается на регистр 5

Номер формата микрокоманды с выхода 1.4 блока 1 памяти поступает на дешифратор 16 и возбуждает em в горой выход По заднему фронту очередного импульса с входа 43 в регистр 5 адреса передачи управления записывается адрес устройства. которому передается управление По заднему фронту импульса со входа 44 триггер 10 управления переходит в единичное состояние и открывает по управляющему входу демультиплексор 14, а в регистр 13 записывается адрес передачи управления Адрес передачи управления с выхода рргистра 13 через демультиплексор 14 поступает на выход 53.j устройства (j - номер, устройства которому передается управление (значение j определяется содержимым регистра 5).

Сигналы микроопераций с выхода 1.1 блока 1 памяти записываются о регистр 3 аналогично описанному выше алгоритму.

Адрес обращения к последующей микрокоманде в устройстве формируется следующим образом. Сигнал со второго выхода дешифратора 16 поступает на управляющий вход счетчика 2 адреса. По заднему фронту импульса со входа 42 устройства содержимое счетчика 2 адреса увеличивается на единицу. Далее устройство функционирует аналогично описанному выше алгоритму.

Передача управления с остановом.

В этот режим устройство переходит из описанных выше рабочих режимов функционирования при считывании из блока 1 памяти микрокоманды третьего формата (см. фиг. 2,в). При этом адрес обращения к блоку

1 1ЫМЯТИ VI Ч1 11 I ) vo i|iii, in | I |. ь ч

упртвлрнмр г пы пда 1 } (щпк 1 d-)iui

ПО( ТуМЫРТ Н,1 ИНфпрмЧЦИОННЫС и ДЫ |ЬЧИ

(, 13. г. выхода 1 3 Гътокл 1 п ишти счши вартгя код номера уг троигт п.) которому

НеобхОДИНО HPpPjpTb уНр,1В РНИ И ПО Ту

пает на pet иг тр S Причин 1 рмти мтрс команды тин тупеет на дрмшФр пор 1Ь , третьем пы«г)де дешифратор 1( при этом

пояолчотс0сигнал ичоро 1 ЛРМРНТ И ПИ 31 поступает на племен г И 23 По заднему фронту очередного импулы а го 13 ч регистр 5 с выхода 1 Зблсжч 1 млмчти з,ши ШРТСЯ номрр угтроигт в.з ююрому перед 1

е т с ч управление По з лд и о му Фронту импульса со вход 14 устройства п ргчистп

13чапимкмгд адрес nepon, i и управл ччия триггер 10 перейдет в единичное ГОГТО-ОШР и разрешит выдачу a/ipei з передачи управ

лен и я г per иг л рл 13 414103 дом , пыип IP гор

14ня выход г 3 j О R(5)

При считып нии третьего мата на выхода 46 (пока 1 памяти почпляет Ся сигнал Конец команды, который

разрешает прохождение коммутатор 17 адреса первой мш рокомтнды очередной микропрограммы от других устройств либо от верхнего уровня управления При поступлении адреса на один из входов 40 1 40 (1-1)

либо на 39 устройства функционирует аналогично описанному выше алюритму Режим диагностики

(В ITOM режиме устройство переходит при поступлении кода операции диагноста

ки с верхнего уровни управления на вход 39 операции устроис гва Птоту од поступает на информационный вход дешифратора 15 и через коммутатор 17 на информационный вход счетчика 2 адреса При поступлении

очередного импульса со входа 42 устройства этот код записывается в счетчик 2 адреса и возбуждает соответствующий выход дешифратора 15 Сигнал с выходя дешифратора Г) поступает через элемент ИЛИ 31 на

триггера 7 диагностики и устанавливает его в единичное состояние При этом устройство переходит в диагностический режим функционирования

Из блока 1 памяти выбирается микрокоманда четвертого формата (см фиг 2.г) Сигнал с четвертого выходя дешифратора 16 через элемент 34 и 35 ИЛИ поступает на элементы 23 и 24 И По заднему фронту импульса, поступающему на вход 43 устройства, в регистр 5 с выхода 1 3 блока 1 памяти запишется адрес устройства которому будет передаваться управление в процессе диагностирования кольца устройств, а в регистр 4 адрес устройства, из которого будет

приниматься диагностическая информация в устройство и копия контрольного кода.

По очередному импульсу со входа 44 устройства в регистр 13 с выхода 1.2 блока 1 памяти запишется первый контрольный код и триггер 10 перейдет в единичное состояние. При этом первый контрольный код с регистра 13 через демультиплексор 14 и выход 53.J поступит на j-e устройство системы.

Кроме того, по заднему фронту импульса со входа 44 устройства в счетчик 6 с выхода 1.1 блока 1 памяти запишется дополнительный код времени прохождения первого контрольного кода через устройство диагностируемого кольца устройства.

Сигнал Конец команды с выхода 46. выходов 1.1 блока 1 памяти микрокоманд настраивает коммутатор 17 HJ прием информации по второму и третьему информационным входам.

Код адреса устройства, возвращающего управление с выхода регистра 4, поступает на адресный вход мультиплексора 11 и настраивает его на прием информации от 1-го устройства, которое является последним устройством в кольце и выдает контрольный код устройству, являющемуся инициатором диагностирования кольца устройств системы.

В таком состоянии устройство ожидает возвращения контрольного кода из кольца. Импульсы со входа 44 через элемент И 26 поступают на счетный вход счетчика 6 и увеличивают его содержимое на единицу.

Номера устройств, включаемых в кольцо в процессе диагностирования, определяются первым контрольным кодом и соответствующим программированием блоков 1 памяти устройств системы. Первый контрольный код поступает на первое устройство кольца и является адресом микрокоманды четвертого формата. При считывании этой микрокоманды первое устройство кольца передает управление (первый контрольный код) второму устройству кольца и так далее.

Пройдя через все устройства кольца, первый контрольный код поступит на вход 40.Y исходного устройства, находящегося в диагностическом режиме. Со входа 40. f первый контрольный код через мультиплексор 11 и коммутатор 18 поступит на элемент 32 ИЛИ, блок 20 сравнения и коммутатор 17.

Если все устройства кольца и связи между устройствами исправны, то первый контрольный код поступит в исходное устройство без искажений и через данный интервал времени после выдачи, По импульсу

со входа 42 первый контрольный код запишется в.счетчик 2 адреса.

По адресу (первому контрольному коду), записанному в счетчике 2 адреса, из блока

1 памяти выбирается микрокоманда пятого формата (см. фиг. 2,д) и на пятом выходе дешифратора 16 появляется сигнал. При неисправности устройств в кольце, либо связей в исходное устройство первый

контрольный код поступит с искажением, либо с задержкой на интервал времени, больший допустимого.

Если счетчик 6 успеет переполниться раньше, чем поступит отклик на первый контрольный код из кольца, то сигнал переполнения счетчика 6 установит триггер 9 в единичное состояние. Триггер 9 сформирует сигнал зацикливания и выдаст его на вы- хрд 49 группы 52 выходов устройства, Если

первый контрольный код устройства f поступит раньше, чем переполнится счетчик 6, но будет отличаться от первого контрольного кода (эталона), на выходе блока 20 сравнения сигнал будет отсутствовать, а на

выходе элемента ИЛИ 32 будет присутствовать.

По импульсу со входа 43 устройства триггер 8 перейдет в единичное состояние и сформирует сигнал отказа. Этот сигнал поступит на группу 52 выходов и через элемент ИЛИ 37 закроет элементы И 28-30.

Если первый контрольный код поступит изЗ-го устройства до истечения времени переполнения счетчика 6 и будет совпадать с

эталоном, то на выходе блока 20 сравнения появится сигнал. При поступлении очередного импульса со входа 43 на выходе элемента И 25 появится сигнал и обнулит счетчик 6.

Кроме того, по импульсу со входа 43 в

регистр 4 возврата записывается адрес устройства, передающего управление в исходное устройство в процессе

диагностирования кольца устройств, и копия второго контрольного кода.

Далее устройство выдает в диагностируемое кольцо второй контрольный код (обратный первому контрольному коду). Выдача второго контрольного кода и его

прохождение по кольцу осуществляется аналогично выдаче и обработке первого контрольного кода.

При поступлении импульса на вход 44 устройства в регистр 13 записывается второй контрольный код и триггер 10 переходит в единичное состояние. Далее контроль кольца устройств и обработка второго контрольного кода происходит аналогично описанному выше алгоритму.

После отработки отклика пторого контрольного кода и записи его неискаженного значения в счетчик 2 адреса исходного устройства происходит обращение к блоку 1 памяти. При этом считывается микрокоманда первого формата. Сигнал с выхода 47 Конец диагностирования выхода 1.1 блока 1 памяти поступает на элемент И 27. При поступлении очередного импульса со входя 44 устройства на выходе элемента И 27 появляется сигнал, переводящий триггер 7 диагностики в нулевое состояние. Этим же сигналом очередная микрокоманда первого формата записывается в регистр 3. На выходе 48 Конец работы регистра 3 появляется единичный сигнал. Это сигнал поступает на выход 50 группы 52 выходов и сигнализирует на блок верхнего уровня 54 управления о готовности кольца устройств к работе. Далее устройство для программного управления функционирует аналогично описанному выше алгоритму.

Таким образом, устройство позволяет повысить достоверность функционирования и обеспечивает благодаря этому умень- шение времени существования необнаружения константных неисправностей.

Формула изобретения

Устройство для программного управления, содержащее блок памяти, счетчик адреса, регистр микрокоманд, счетчик, триггер диагностики, первый и второй дешифраторы, блок сравнения, первый элемент И. первый и второй элементы ИЛИ. причем информационные выходы счетчика адреса соединены с адресными входами блока памяти, выходы старших разрядов группы выходов микроопераций которого соединены с информационными входами счетчика и регистра микроопераций, выходы старших разрядов которого являются выходами микроопераций устройства, выходы меток блока памяти соединены с входами второго дешифратора, четвертый выход которого соединен с входом разрешения счетчика адреса, информационные входы первого дешифратора являются входами операций устройства, а выходы соединены с входами первого элемента ИЛИ, выход которого соединен с входом установки триггера диагностики, выход первого элемента И соединен с входом записи счетчика, отличающее- с я тем, что, с целью расширения области применения устройства, в него введены регистры возврата, передачи управления и кода, триггеры отказа, зацикливания и управления, демультиплексор, мультиплексоры адреса и условий, первый и второй коммутаторы, группа элементов ИЛИ, второй-десятый элементы И и третий-впсьмой элементы ИЛИ, причем группы входов передачи управления устройства являются группами информационных входов

мультиплексора адреса и группы элементов ИЛИ. выходы которых соединены соответственно с первой и второй группами входов второго коммутатора, выходы которого соединены с первыми группами информацион0 ных входов первого коммутатора и блока сравнения и входами второго элемента ИЛИ, выход которого соединен с первым входом второго элемента И. выход которого соединен с информационным входом триг5 гера отказа, выход которого является выходом третьего разряда группы осведомительных выходов устройства и соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с инверсны0 ми входами восьмого, девятого и десятого элементов И. выход которого соединен с первыми входами седьмого, шестого и первого элементов И, с входом синхронизации триггера управления и с входами записи

5 регистров кода и микрокоманд, выход Конец работы которого является выходом второго разряда группы осведомительных выходов устройства и соединен со вторым входом седьмого элемента ИЛИ. входы опе0 раций устройства являются второй группой информационных входов первого коммутатора, выходы которого соединены с информационными входами счетчика адреса, первый вход синхронизации устройства яв5 ляется прямым входом восьмого элемента И, выход которого соединен с входом разрешения первого дешифратора и входом счета/записи счетчика адреса, третий и второй входы синхронизации устройства являются

0 соответственно.прямыми входами десятого и девятого элементов И. выход которого соединен с входом синхронизации триггера отказа и с первыми входами третьего, четвертого и пятого элементов И. выход кото5 рого соединен с входом сброса счетчика, выход старшего разряда которого соединен с входом установки триггера зацикливания, прямой выход которого соединен с третьим входом седьмого элемента ИЛИ и является

0 выходом первого разряда группы осведомительных выходов устройства, выходы старших разрядов адреса блока памяти соединены с информационными входами регистра кода и с третьей группой информа5 ционных входов первого коммутатора, выход младшего разряда группы выходов адреса блока памяти соединен с входами младшего разряда группы информационных входов мультиплексора условий, выход которого соединен с входами младшего разряда группы информационных входов регистра кодов и третьей группы информационных входов первого коммутатора, выходы кода условия блока памяти соединены с адресными входами мультиплексора усчовий и информационными входами регистра передачи управления, выходы которого соеди- нены с адресными входами демультиплексора, группы информационных выходов которого являются группами выходов передачи управления устройства, входы сигналов условия устройства являются входами старших разрядов группы информационных входов мультиплексора условий, выходы старших разрядов группы выходов микроопераций соединены с информационными входами регистра возврата, выходы которого соединены с адресными входами мультиплексора адреса и со второй группой информационных входов блока сравнения,выход которого соединен с инверсным входом второго элемента И и со вторым входом пятого элемента И. выход Конец команды выходов микроопераций блока памяти соединен с-первым, вторым и третьим инверсными управляющими входами первого коммутатора, выход Конец диагностики выходов микроопераций блока памяти соединен со вторым входом седьмого элемента И, выход которого соединен с входом сброса триггера диагностики, инверсный выход которого соединен со вторым входом третьего элемента И и с информационным входом триггера управления, выход которого соединен с входом разрешения демультиплексора, прямой выход триггера диагностики соединен с третьим входом второго элемента И, с прямым и

инверсным входами управления второго коммутатора и со вторыми входами первого и шестого элементов И, выход которого соединен с входом прямого счета счетчика,

выходы младших разрядов которого соединены с входами восьмого элемента ИЛИ, выход которого соединен соответственно с третьими прямым и инверсным входами шестого и первого элементов И, инверсный

выход триггера зацикливания соединен с третьим входом пятого элемента И, первый выход второго дешифратора соединен с первым входом пятого элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход которого соединен с третьим входом третьего элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, выход которого соединен с входом записи регистра передачи управления, второй выход второго дешифратора соединен со вторыми входами четвертого и пятого элементов ИЛИ, выход которого соединен со вторым входом четвертого элемента И, выход которого соединен со вторым входом

шестого элемента ИЛИ и с входом записи регистра возврата, третий выход второго дешифратора соединен с третьим входом четвертого элемента ИЛИ, четвертый выход второго дешифратора соединен с четвертым входом четвертого элемента ИЛИ и с первым входом третьего элемента ИЛИ, выход которого соединен с входом разрешения регистра микрокоманд, пятый выход второго дешифратора соединен с четвертым управляющим входом первого коммутатора и со вторым входом третьего элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при проектировании вычислительных систем с высокой достоверностью функционирования. Цель изобретения - расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее блок памяти, счетчик адреса, регистр микрокоманд, счетчик, триггер диагностики, первый и второй дешифраторы, блок сравнения, первый элемент И, первый и второй элементы ИЛИ, дополнительно введены регистр возврата, регистр передачи управления, регистр кода, триггер отказа, триггер зацикливания, триггер управления, демультиплексор, мультиплексоры адреса и условий, первый и второй коммутаторы, группа элементов ИЛИ, второй - десятый элементы И, третий - восьмой элементы ИЛИ. Введение новых элементов позволяет повысить достоверность функционирования устройства и обес- печивает уменьшение времени существования необнаружения константных неисправностей. 5 ил, Ё

JU

- - я a U

Фиг 1 llucml

«I

я

JO; Sty

Гг

к

фиг 1 листг

ii

(Т) - nepftiu центральный ков

@@ - нот педу-пя, (обращающего отклик

®ff) -fyffa диагностирования кольца нодулей

(Т) - Smeacii контослоныи код

(i) - vrw ,Stilpou((iff рпняин

Фы 3

е

с:

ч #

ць 16 JJ J «

7 7 4

5J

«

0

Выттениг функций илраблгни

uTIП

Htpfdma ynpat/ifnus

flpppfauo pfvvf wj cm

лn

1

фпг nrpedwii 1// ро1яени

Vuii /luc/r IJ

Диагностирование кольцо модулей

®иг5 Листг

в/порой яон/г ро/н ь/й

ход Фиг. 5 Лист 3

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-06-15—Публикация

1989-02-01—Подача