ISD

Oi

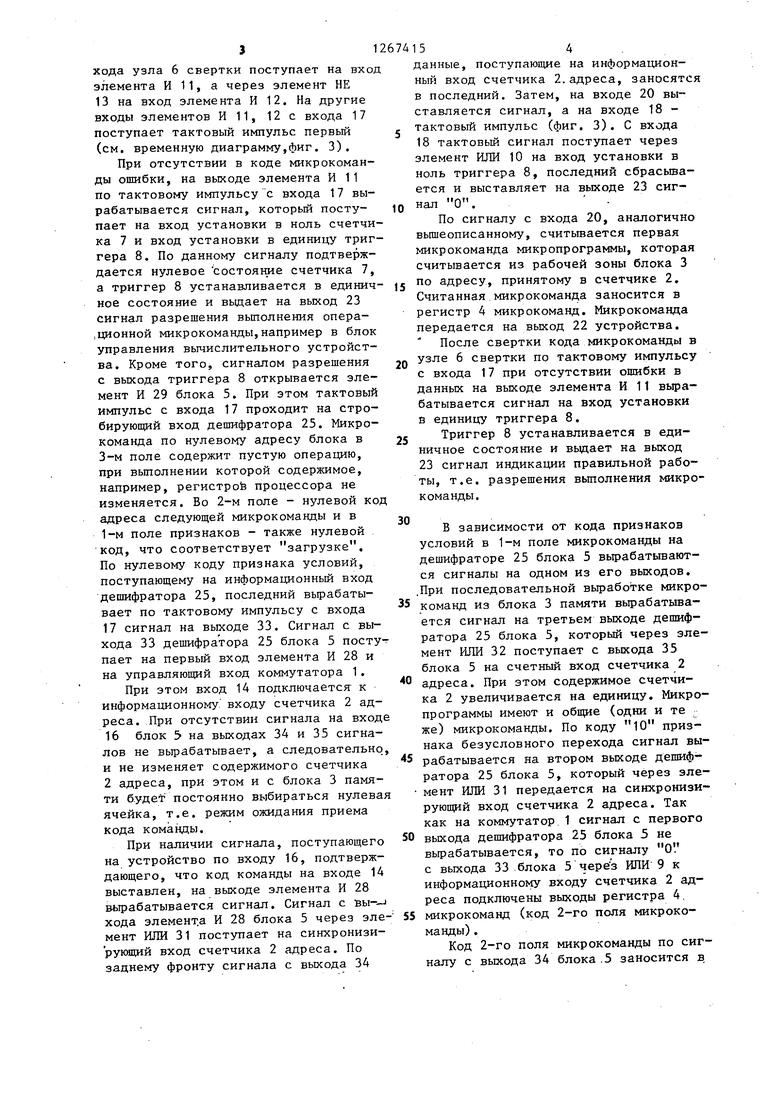

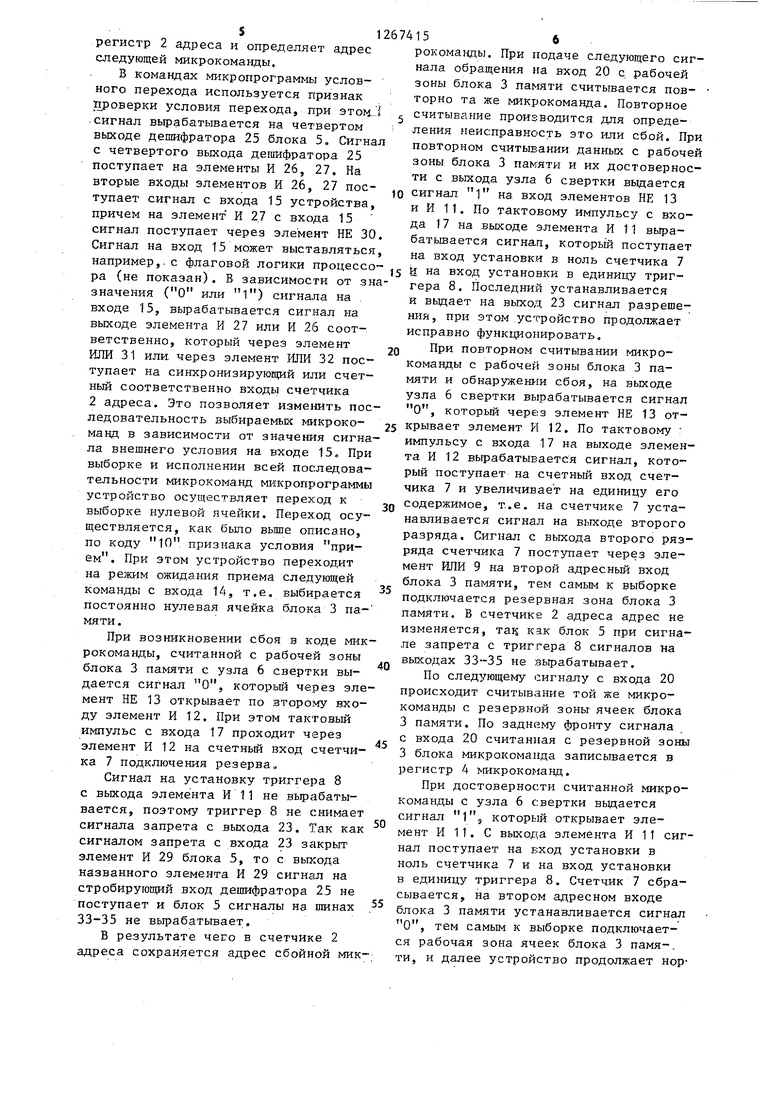

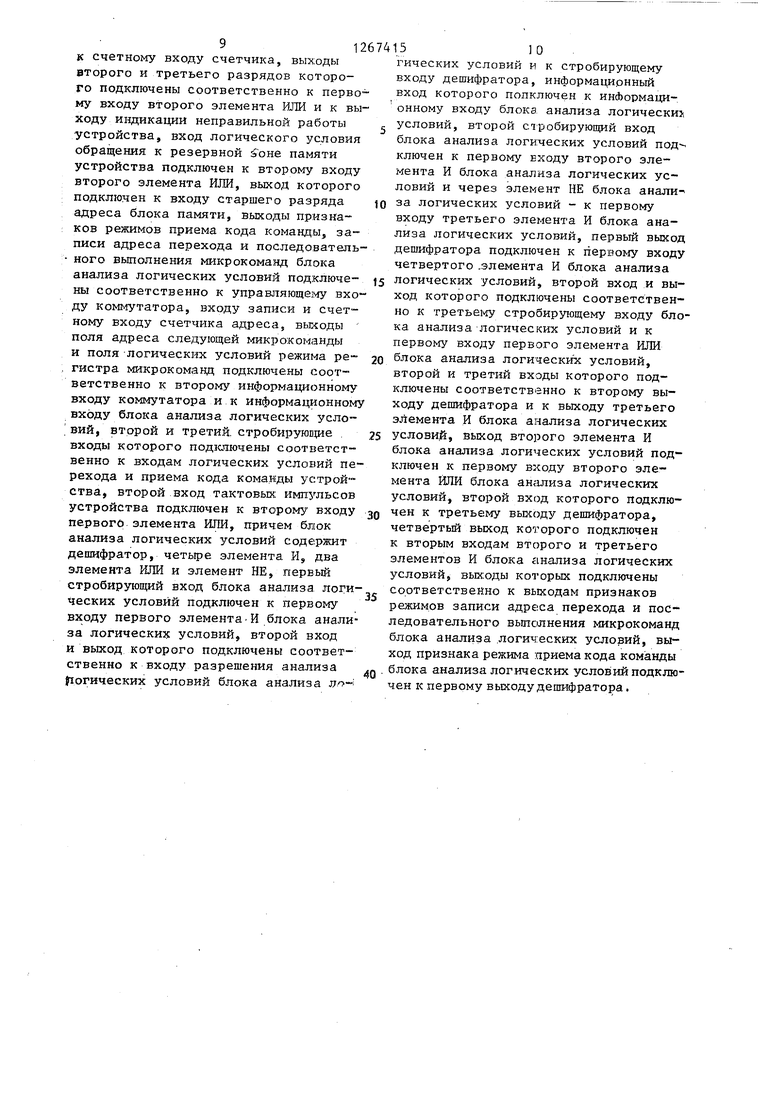

4;: Изобретение относится к вычислительной технике и может быть использовано в устройствах управления цифровых вьгаислительных машин. Целью изобретения является повыше ние достоверности функционирования. На фиг. 1 представлена функционал ная схема устройства, на фиг. 2 функциональная схема блока анализа логических условийj на фиг, 3 - временная диаграмма работы устройства. Устройство содержит коммутатор 1, счетчик 2 адреса, блок 3 памяти, регистр 4 микрокоманд, блок 5 анализа логических условий, узел 6 свертк по модулю, счетчик 7, триггер 8, эле менты ИЛИ 9j 10, элементы И 11, 12, элемент НЕ 13, входы 14 кода .команды 15 логического условия перехода, 16 логического условия приема кода команды устройства, первый 17 и второй 18 входы тактовых импульсов устройст ва, входы 19 начальной установки, 20 выборки микрокоманды, 21 логического условия обращения к резервной зоне памяти устройства, выходы 22 ко да микрооперации, 23 индикации правильной работы, 24 индикации неправильной работы устройства. Блок анализа логическ к условий содержит дешифратор 25, элементы И 26-29, элемент НЕ 30, элементы ШШ 31, 32, выходы 33 признаков режимов приема кода команды, 34 записи адреса перекода, 35 последовательного вы полнения микрокоманд. Устройство работает следуюпр м образом. При включении пита1шй на устройст по входу 19 подается сигнал сброса, например, от блока управления вычислительного устройства (не показано). При этом в счетчике 2 адреса уста навливается нулевой код адреса, в ре гистре 4 микрокоманд устанавливается нулевой код микрокоманды, счетчик 7 устанавливается в О (шина сброса счетчика не показана). Сигналом сброса с входа 19 через элемент ИЛИ 10 сбрасывается триггер 8, который при этом на выход 23 вьздает признак запре та, например, в блок упра)зления вычислительного устройства.(не показан) , Сигнал О с выхода 23 в блоке управления -вычислительного устройства может быть использован, например, для запрещения выполнения данной микрокоманды процессором.. С выхода триггера В сигнал О поступает также на первый вход- элемента И 29 блока 5, закрывая его для прохождения тактового импульса с входа 17. При этом блок 5 сигналы на выходе не вьфабатывает. Работа устройства производится при подаче на входы 17 и 18 тактовых импульсов и на вход 20 сигнала выборки микрокомавды, например, от блока управления вычислительного устройства (непоказан). Названные сигналы подаются в соответствии с временной диаграммой (фиг. 3). Сигнал с входа 20 поступает на управляющий вход блока 3 .памяти и регистр 4 м1-1крокоманд. Так как счетчик обнулен, то с его второго выхода (второй разряд счетчика) через элемент ИЛИ 9 на второй адресный вход блока 3 памяти (например, на вход старшего разряда адреса) поступает сигнал О при этом считывание производится с ячеек рабочей зоны блока 3 памяти. Считанная микрокоманда с блока 3 передается на информационньй вход регистра 4 микрокоманд. По заднему фронту сигнала с входа 20 информация записьшается в регистр 4, Микр.окоманда разделена на три поля: в 1-м поле размеп ены логические усяовия режи;ма работы устройства, во 2-м - адрес следующей микрокоманды, в - код операционной части микрокоманды. Признаки логических условий поступают на информационный вход дешифратора 25 блока 3, адрес следующей микрокоманды - на первый вход коммутатора 1, код операционной микрокоманды - на вксход 22 устройства. В предлагаемом устройстве поле логических условий содержит два разряда, состояние которых определяет вьшолнение следующих операций (режимов): 00 - прием кода команды, 01 последовательное вьшолнение микрокоманд, 10 - безусловный переход,11 условный переход. Б первом поле может быть и другое количество разрядов. Кроме того, с выхода регистра 4 микроманд сигналы со всех разрядов, включая контрольные, поступают на узел 6 свёртки. Последний производит свертку кода г 1икрокоманды, например, по модулю два, причем при достоверности данных на выходе узла 6 свертки устанавливается сигнал V,. Результат с вы3хода узла 6 свертки поступает на вхо элемента И 11, а через элемент НЕ 13 на вход элемента И 12. На другие входы элементов И 11, 12 с входа 17 поступает тактовый импульс первый (см. временную диаграмму,фиг. 3). При отсутствии в коде микрокоманды ошибки, на выходе элемента И 11 по тактовому импульсу с входа 17 вырабатывается сигнал, который поступает на вход установки в ноль счетчи ка 7 и вход установки в единицу триг гера 8. По данному сигналу подтверждается нулевое состояние счетчика 7, а триггер 8 устанавливается в единич ное состояние и выдает на выход 23 сигнал разрешения вьшолнения опера.ционной микрокоманды,например в блок управления вычислительного устройства. Кроме того, сигналом разрешения с выхода триггера 8 открывается элемент И 29 блока 5. При этом тактовый импульс с входа 17 проходит на стробирующий вход дешифратора 25. Микрокоманда по нулевому адресу блока в 3-м поле содержит пустую операцию, при вьшолнении которой содержимое, например, регистров процессора не изменяется. Во 2-м поле - нулевой ко адреса следующей микрокоманды ив 1-м поле признаков - также нулевой код, что соответствует загрузке. По нулевому коду признака условий, поступающему на информационный вход дешифратора 25, последний вьфабатывает по тактовому импульсу с входа 17 сигнал на выходе 33. Сигнал с выхода 33 дешифратора 25 блока 5 посту пает на первый вход элемента И 28 и на управляющий вход коммутатора 1. При этом вход 14 подключается к информационному входу счетчика 2 адреса. При отсутствии сигнала на вход 16 блок 3 на выходах 34 и 35 сигналов не вьфабатывает, а следовательно и не изменяет содержимого счетчика 2 адреса, при этом и с блока 3 памяти будет постоянно выбираться нулева ячейка, т.е. режим ожидания приема кода команды. При наличии сигнала, поступающего на устройство по входу 16, подтверждающего, что код команды на входе 14 выставлен, на выходе элемента И 28 вырабатывается сигнал. Сигнал с вы-- хода элемента И 28 блока 5 через эле мент ИЛИ 31 поступает на синхронизирукиций вход счетчика 2 адреса. По заднему фронту сигнала с выхода 34 154 . данные, поступающие на информационный вход счетчика 2.адреса, заносятся в последний. Затем, на входе 20 выставляется сигнал, а на входе 18 тактовьй импульс (фиг. 3). С входа 18 тактовый сигнал поступает через элемент ИЛИ 10 на вход установки в ноль триггера 8, последний сбрасьша- ется и выставляет на выходе 23 сигнал О. По сигналу с входа 20, аналогично Bbmie описан ному, считьтается первая микрокоманда микропрограммы, которая считывается из рабочей зоны блока 3 по адресу, принятому в счетчике 2, Считанная микрокоманда заносится в регистр 4 микрокоманд. Микрокоманда передается на выход 22 устройства. После свертки кода микрокоманды в узле 6 свертки по тактовому импульсу с входа 17 при отсутствии ошибки в данных на выходе элемента И 11 вырабатывается сигнал на вход установки в единицу триггера 8. Триггер 8 устанавливается в единичное состояние и вьщает на выход 23 сигнал индикации правильной работы, т.е. разрешения вьтолнения микрокоманды. В зависимости от кода признаков условий в 1-м поле микрокоманды на дешифраторе 25 блока 5 вырабатываются сигналы на одном из его выходов, При последовательной выработке микрокоманд из блока 3 памяти вырабатывается сигнал на третьем выходе дешифратора 25 блока 5, который через элемент ИЛИ 32 поступает с выхода 35 блока 5 на счетный вход счетчика 2 адреса. При этом содержимое счетчика 2 увеличивается на единицу. Микропрограммы имеют и общие (одни и те же) микрокоманды. По коду 10 признака безусловного перехода сигнал вырабатывается на втором выходе дешифратора 25 блока 5, который через элемент ИЛИ 31 передается на синхронизируюш;ий вход счетчика 2 адреса. Так как на коммутатор 1 сигнал с первого выхода дешифратора 25 блока 5 не вырабатывается, то по сигналу О. с выхода 33 блока 5 через ИЛИ 9 к информационному входу счетчика 2 адреса подключены выходы регистра 4. микрокоманд (код 2-го поля микрокоманды) . Код 2-го поля микрокоманды по сигналу с выхода 34 блока .5 заносится в регистр 2 адреса и определяет адрес следующей микрокоманды, В командах микропрограммы условного перехода используется признак проверки условия перехода, гфи этомЛ сигнал вьфабатывается на четвертом выходе дешифратора 25 блока 5. Сигна с четвертого выхода де1иифратора 25 поступает на элементы И 26, 27. На вторые входы элементов Е 26, 27 поступает сигнал с входа 15 устройства, причем на элемент И 27 с входа 15 сигнал поступает через элемент НЕ 30 Сигнал на вход 15 может выставляться например,, с флаговой логики продессо ра (не показан). В зависимости от зн (О или 1) значения (О или сигнала на входе 15, вьфабатывается сигнал на выходе элемента И 27 или И 26 соответственно, который череэ элемент ИЛИ 31 или, через элемент .ИЛИ 32 поступает на синхронизирующий или счетный соответственно входы счетчика 2 адреса. Это позволяет изменить пос ледовательность выбираемых микрокоманд в зависимости от значешгя сигна ла внешнего условия на входе 15, При выборке и исполнении всей последовательности микрокоманд микропрограммы устройство осуществляет переход к выборке нулевой ячейки. Переход осуществляется, как было выше описано, по коду 10 признака условия прием. При этом устройство переходит на режим ожидания приема следующей команды с входа 14, т.е. выбирается постоянно нулевая ячейка блока 3 памяти. При возникновении сбоя в коде мик рокоманды, считанной с рабочей зоны блока 3 памяти с узла 6 свертки выдается сигнал О, который через эле мент НЕ 13 открывает по второ;му входу элемент И 12. При этом тактовый импульс с входа 17 проходит через элемент И 12 на счетньм вход счетчика 7 подключения резерва,, Сигнал на установку триггера 8 с выхода элемента И 11 не вырабатывается, поэтому триггер 8 не снимает сигнала запрета с выхода 23. Так как сигналом запрета с входа 23 закрыт элемент И 29 блока 5, то с вьосода названного элемента И 29 сигнгил на стробирующий вход дещифратора 25 не поступает и блок 5 сигналы на шинах 33-35 не вьфабатывает. В результате чего в счетчике 2 адреса сохраняется адрес сбойной мик 1 15 рокомавды. При подаче следующего сигнала обращения на вход 20 с. рабочей зоны блока 3 памяти считывается пов- торно та же микрокоманда. Повторное считывание производится для определения неисправность это или сбой. При повторном считывании данных с рабочей зоны блока 3 пакяти и их достоверности с выхода узла 6 свертки выдается It XII сигнал 1 на вход элементов НЕ 13 и И 11, По тактовому импульсу с входа 17 на выходе элемента И 11 вырабатьшается сигнап, которьй поступает на вход установки в ноль счетчика 7 - „ установки в единицу триггера 8. Последний устанавливается и вьщает на выход 23 сигнал разрешения, при этом .устройство продолжает исправно функционировать, При повторном считывании микрокоманды с рабочей зоны блока 3 памяти и обнаружении сбоя, на выходе узла 6 свертки вырабатывается сигнал О, который через элемент НЕ 13 открывает элемент И 12. По тактовому импульсу с входа 17 на выходе элемента И 12 вырабатывается сигнал, который поступает на счетнью вход счетчика 7 и увеличивает на единицу его содержимое, т.е. на счетчике 7 устанавливается сигнал на выходе второго разряда. Сигнал с выхода второго рязряда счетчика 7 поступает через элемент ИЛИ 9 на второй адресный вход блока 3 памяти, тем самым к выборке подключается резервная зона блока 3 памяти. В счетчике 2 адреса адрес не изменяется, Taij как блок 5 при сигнале запрета с триггера 8 сигналов на выходах 33-35 не вырабатывает. По следующему сигналу с входа 20 происходит считывание той же микрокоманды с резервной зоны ячеек блока 3 памяти. По заднему фронту сигнала с входа 20 считанная с резервной зоны 3 блока микрокоманда записьтается в регистр 4 rикpoкoмaнд. При достоверности считанной микрокоманды с узла 6 свертки выдается сигнал который открывает элемент И 11. С выхода элемента И 11 сигнал поступает на р;ход установки в ноль счетчика 7 и на вход установки в единицу триггера 8. Счетчик 7 сбрасывается, на втором адресном входе блока 3 памяти устанавливается сигнал О, тем самым к выборке подключается рабочая зона ячеек блока 3 памя-. ти, и далее устройство продолжает нор71мально функционировать как это описано выше. При обнаружении ошибки в коде мик рокоманды, считанной с резервной зоны блока 3 памяти, вырабатывается с сигнал на выходе элемента И 12, кото рый увеличивает содержимое счетчика 7 на единицу. При этом в названномсчетчике 7 устанавливается единица в первом и во втором разрядах. Триггер 8 продолжает находиться в сброшенном состоянии, так как на выходе элемента И 11 сигнал не вырабатывается, и с выхода триггера 8 продолжа ется выдача сигнала запрета на выход 23. В результате чего изменения адреса в счетчике 2 адреса не происходит. С второго выхода счетчика 7 выдается сигнал 1, который через элемент ИЛИ 9 поступает на второй адрес ный вход блока 3 памяти, тем самым подключая к выборке резервную зону ячеек блока 3 памяти. По следующему сигналу обращения с шины 20 выбирается повторно та же микрокоманда с резервной зоны блока 3 памяти. Аналогично, при достоверности считанной микрокоманды на выходе элемента И 11 вырабатывается сигнал, который сбрасывает счетчик и устанавливает триггер 8. Последний выставляет сигнал разрешения на выхо де 23, а счетчик 7 подключает к выборке рабочую зону блока 3 и устройство продолжает исправно функционировать. При обнаружении сбоя в коде микро команды, аналогично описанному, на выходе элемента И 12 вырабатывается сигнал, который поступает на счетный вход счетчика 7 и увеличивает его содержимое на единицу. При этом в счетчике 7 устанавливается единица в третьем разряде так как предьщущее значение счетчика 7 равнялось трем. Сигнал с третьего разряда упо мянутого счетчика 7 поступает на вы ход 24 устройства и сигнализирует о его неисправности. Данный сигнал мо жет использоваться, например, для останова устройства-. Дпя проверки и правности ячеек памяти резервной зо ны .блока 3 памяти, например, в диаг ностических тестах, используется вт рой вход элемента ИЛИ 9. По входу 21 на вход элемента ИЛИ 9 подается сигнал, например-, от блока управления вычислительного устройства, (не .158показан).. С выхода элемента ИЛИ 9 сигнал поступает на второй адресньп вход блока 3 памяти, при этом к выборке будет постоянно подключена резервная зона блока 3 памяти. По наличию сигнала на входе 21 судят о неисправности ячеек памяти резервной зоны блока 3. Формула изобретения Микропрограммное устройство управления, содержащее коммутатор, счетчик адреса, блок памяти, регистр микрокоманд, узел свертки по модулю, триггер, два элемента РШИ, два элемента И, причем выход коммутатора подключен к информационному входу счетчика адреса, выход которого подключен к входу младших разрядов адреса блока памяти, вькод которого подключен к информационному входу регистра микрокоманд, выход поля операционной части м1-1крокоманды регистра микрокоманд подключен к выходу кода микрооперации устройства, информационному входу узла свертки по модулю, первый информационный вход коммутатора подключен к входу кода команды устройства, отличающееся тем, что, с целью повышения достоверности функционирования, в него введелы элемент НЕ, счетчики и блок ана-i лиза логических условий, причем вход выборки микрокоманды устройства подключен к входу записи - считывания блока памяти и к синхровходу регистра микрокоманд, вход начальной установки устройства подключен к входам установки в ноль счетчика адреса и регистра микрокоманд и к первому входу первого элемента ИЛИ, выход которого подключен к входу установки в ноль триггера, первый вход тактовых импульсов устройства подключен к первому стробирующему входу блока анализа логических условий и к первым входам первого и второго элементов И, выход первого элемента .И подключен к входу установки в ноль с4етчика и к входу установки в единицу триггера, выход которого подключен к выходу индикации правильной работы устройства и к входу разрешения ана лиза логических условий, выход узла свертки по модулю подключен к второму входу первого элемента И и через элемент НЕ - к второму входу второго элемента И, выход которого подключен к счетному входу счетчика, выходы второго и третьего разрядов которого подключены соответственно к перво му входу второго элемента ИЛИ и к вы ходу индикации неправильной работы устройства, вход логического условия обращения к резервной $оне памяти устройства подключен к второму входу второго элемента ИЛИ, выход которого подключен к входу старшего разряда адреса блока памяти, выходы призна™ ков режимов приема кода команды, записи адреса перехода и последователь ного выполнения микрокоманд блока анализа логических условий подключены соответственно к управляюще угу вхо ду комг-гутатора, входу записи и счетному входу счетчика адреса, выводы поля адреса следующей микрокоманды и поля логических условий режима регистра микрокоманд подключены соответственно к BTopoi v информационному входу коммутатора и к информационном входу блока анализа логических усло ВИЙ, второй и третий, стробируювще входы которого подключены соответственно к входам логических условий пе рехода и приема кода команды устройства, второй вход тактовых имп льсов устройства подключен к второму входу первого элемента ИЛИ, причем блок анализа логических условий содержит дешифратор, четыре элемента И, два элемента ИЛИ и элемент НЕ, первый стробирующий вход блока анализа логи ческих условий подключен к первому входу первого элементаИ блока анали за логических условий, второй вход и выход которого подключены соответственно к входу разрешения анализа Уюгических условий блока анализа л/огических условий и к стробирующему входу дешифратора, информационный вход которого подключен к информационному входу блока, анализа логически, условий, второй С1робирующий вход блока анализа логических условий подключен к первому Еходу второго элемента И блока анализа логических условий и через элемент НЕ блока анали за логических условий - к первому входу третьего элемента И блока анализа логических условий, первый выход дешифратора подключен к первому входу четвертого .элемента И блока анализа логических условий, второй вход и выход которого подключены соответственно к третьеачу стробирующему входу блока анализа-логических условий и к первому входу первого элемента ИЛИ блока анализа логических условий, второй и трет11й входы которого подключены соответственно к второму выходу дешифратора и к вьпсоду третьего элемента И блока анализа логических условий, выход второго элемента И блока анализа логических условий подключен к первому входу второго элемента ИЛИ блока ангзлиза логических условий, второй вход которого подключен к третьему выходу дешифратора, четвертый выход которого подключен к вторым входам второго и третьего элементов И блока анализа логических условий, вькоды которых подключены соответственно к выходам признаков режимов записи адреса перехода и последовательного вьтолнения микрокоманд блока анализа .логических условий, выход признака режима приема кода команды блока анализа логических ус лов ий подключен к первому выходу дешифратора.

2zr

fff

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU898431A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1020826A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Устройство микропрограммного управления | 1989 |

|

SU1786486A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1242946A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

Изобретение относится к области вычислительной техники и может быть |1спользовано в устройствах управления ЭВМ. Целью изобретения является повышение достоверности функциони-« рования. Устройство содержит коммутатор, счетчик адреса, блок памяти, регистр микрокоманд, блок анализа логических условий, элемент свертки по модулю, счетчик, триггер, два элемента И, два элемента ИЛИ, элемент НЕ. Цель достигается за счет введения элемента НЕ, счетчика и блока с $ анализа логических условий. 3 ил.

.2

| Микропрограммное устройство управления | 1981 |

|

SU1003084A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Перестраиваемое микропрограммноеуСТРОйСТВО упРАВлЕНия | 1979 |

|

SU830383A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-30—Публикация

1985-05-15—Подача