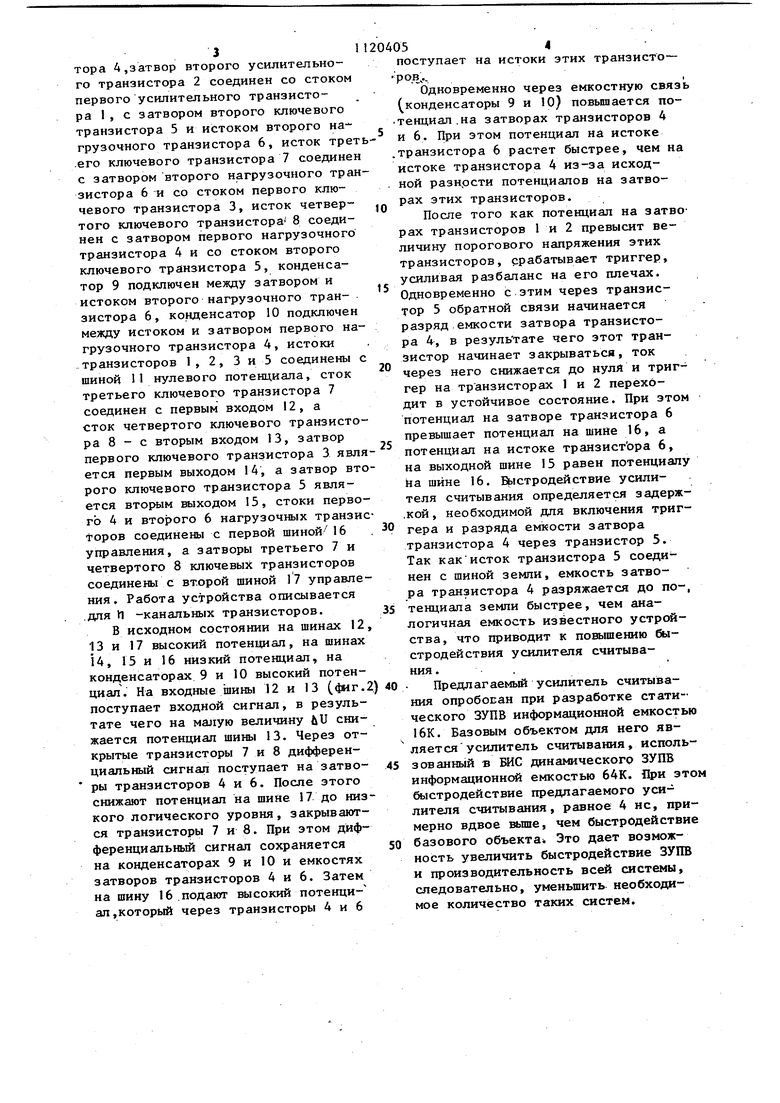

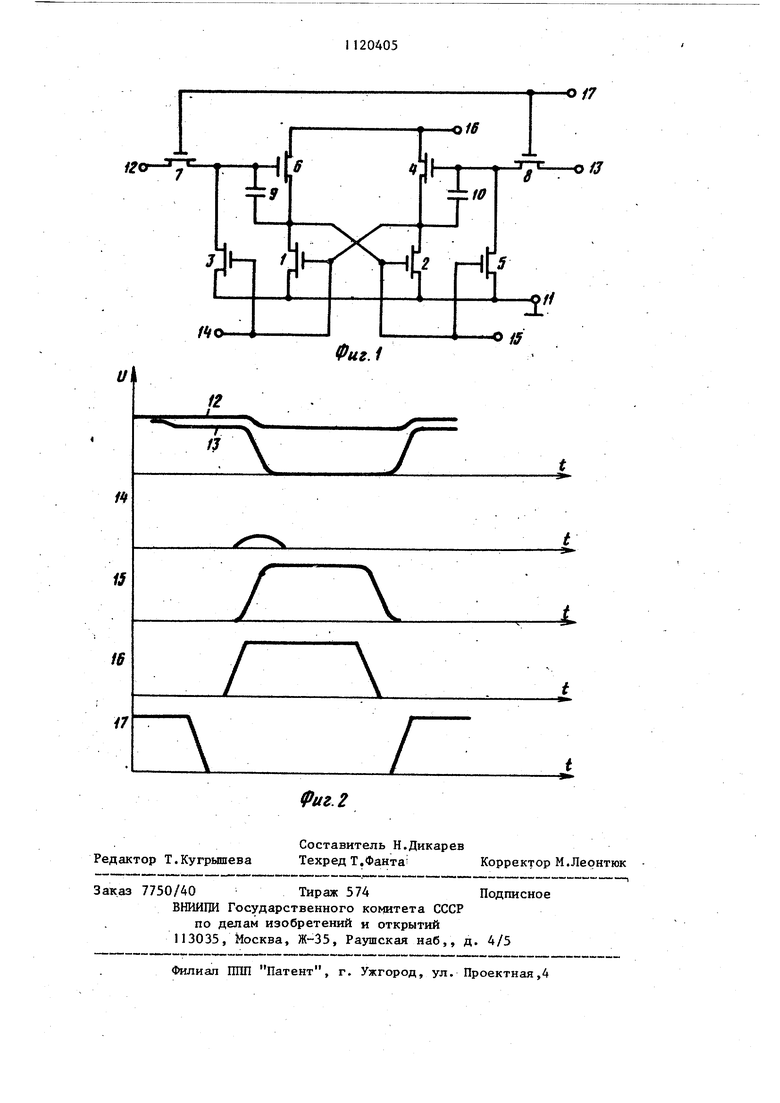

Изобретение относится к области электроники и может быть испапьзовано в ШС ЗУ на МДП-транзисторах. Известен усилитель считывания, содержащий 4 транзистора, 2 сигнал ные шины,2 управляющие шины, в котором первый и второй транзисторы соединены по триггерной схеме, исто ки первого и второго транзисторов соединены с первой управляющей шиной, затвор первого транзистора соединен со стоком второго и истоко третьего транзисторов, затвор второго транзистора соединен со стоком второго и с истоком четвертого тран зисторов, затворы третьего и чётвер того транзисторов соединены с второй управляющей шиной, сток третьего транзистора соединен с первой сигнальной шиной, сток четвертого транзистора соединен с второй сигнальной шиной П . Недостатком данного усилителя сч тывания является низкое быстродейст вие , определяемое временем, необходимым для срабатывания триггера. Наиболее близким по технической сущности к предлагаемому является усилитель считывания , содержащий первый усилительный транзистор, затвор к&торого является первьпу вых дом устройства и соединен со стоком второго усилительного транзистора, затвором первого ключевого транзистора и истоком первого нагрузочного транзистора, затвор второго усилительного транзистора является вторым выходом устройства и соединен с стоком первого усилительного транзистора, затвором второго ключевого транзистора и истоком второго нагру зочного транзистора, сток которого соединен со стоком первого нагрузоч ного транзистора, затвор - со стоко первого ключевого транзистора и пер вой обкладкой первого конденсатора, затвор первого нагрузочного транзистора соединен с первой обкла кой второго конденсатора и стоком второго ключевого транзистора, исто первого усилительного транзистора соединен с истоком второго усилительного транзистора, первую и втор шины управления I2J. Недостатком известного усилителя считывания является низкое быстродействие. Цель изобретения - пошлпение бы родействия усилителя считывания. Поставленная цель достигается тем, что усилитель считывания, содержащий первый усилительный транзистор, затвор которого является первым выходом устройства и соединен со стоком второго усилительного транзистора, затвором первого ключевого транзистора и истоком первого нагрузочного транзистора,затворвторого усилительного транзистора является вторым выходом устройства и соединен со стоком первого усилительного транзистора, затвором второго ключевого транзистора и истоком второго нагрузочного транзистора, сток которого соединен со стоком первого нагрузочного транзистора, затвор со стоком первого ключевого транзистора и первой обкладкой первого конденсатора, затвор первого нагрузочного транзистора соединен с первой обкладкой второго конденсатора и стоком второго ключевого транзистора, исток первого усилительного транзистора соединен с истоком второго усилительного транзистора, пер-, вую и вторую шины управления, содержит третий и четвертый ключевые транзисторы, стоки которых являются соответственно первым и вторым входами устройства, исток третьего ключевого транзистора соединен со стоком первого ключевого транзистора, исток которого соединен с истоками первого усилительного и второго ключевого транзисторов и шиной нулевого потенциала, исток четвертого ключевого транзистора соединен со стоком второго ключевого транзистора, вторая обкладка перво.го конденсатора соединена с истоком второго нагрузочного транзистора, вторая обкладка второго конденсатора соединена с истоком первого нагрузочного транзистора, сток которого подключен к первой шине управления, зат воры третьего и четвертого ключевых транзисторов подключены к второй шине управления. Устройство может быть выполнено как на rt -канальных, так и на р-канальных транзисторах. На фиг1 I представлена принципи1альная схема усилителя считывания; на фкг. 2 - временная диаграмма. Затвор первого усилительного транзистора 1 соединен со стоком второго усилительного транзистора 2, с затвором первого ключевого транзистора 3, с истоком первого нагрузочного транзистора 4,затвор второго усилительного транзистора 2 соединен со стоком первого усилительного транзистора 1 , с затвором второго ключевого транзистора 5 и истоком второго нагрузочного транзистора 6, исток тре .его ключевого транзистора 7 соедине с затвором второго нагрузочного тра зистора 6 и со стоком первого ключевого транзистора 3, исток четвертого ключевого транзистора 8 соединен с затвором первого нагрузочного транзистора 4 и со стоком второго ключевого транзистора 5, конденсатор 9 подключен между затвором и истоком второго нагрузочного транзистора 6, конденсатор 10 подключен между истоком и затвором первого на грузочного транзистора 4, истоки транзисторов 1, 2, 3 и 5 соединены шиной 11 нулевого потенциала, сток третьего ключевого транзистора 7 соединен с первым входом 12, а сток четвертого ключевого транзисто ра 8 - с вторым входом 13, затвор первого ключевого транзистора 3 явл ется первым выходом 14, а затвор вт рого ключевого транзистора 5 является вторым выходом 15, стоки перво го 4 и второго 6 нагрузочных транзи торов соединены с первой шиной/16 управления, а затворы третьего 7 и четвертого 8 ключевых транзисторов соединены с второй шиной 17 управле ния. Работа устройства описывается .для И -канальных транзисторов. В исходном состоянии на шинах 12 13 и 17 высокий потенциал, на шинах 14, 15 и 16 низкий потенциал, на конденсаторах 9 и 10 высокий потенциал. На входные шины 12 и 13 (4иг. поступает входной сигнал, в результате чего на малую величину V снижается потенциал шины 13. Через открытые транзисторы 7 и 8 дифференциальный сигнал поступает на затворы транзисторов 4 и 6. После зтого снижают потенциал на шине 17 до низ кого логического уровня, закрываются транзисторы 7 и 8. При этом дифференциальный сигнал сохраняется на конденсаторах 9 и 10 и емкостях затворов транзисторов 4 и 6. Затем на шину 16 .подают высокий потенциал,который через транзисторы 4 и 6 поступает на истоки этих транзисто- ров.. Одновременно через емкостную связь (конденсаторы 9 и 10) повышается потенциал.на затворах транзисторов 4 и 6. При этом потенциал на истоке транзистора 6 растет быстрее, чем на истоке транзистора 4 из-за исходной разнрсти потенциалов на затворах этих транзисторов. После того как потенциал на затворах транзисторов 1 и 2 превысит величину порогового напряжения этих транзисторов, срабатывает триггер, усиливая разбаланс на его плечах. Одновременно с этим через транзистор 5 обратной связи начинается разряд емкости затвора транзистора 4, в результате чего этот транзистор начинает закрываться, ток через него снижается до нуля и триггер на транзисторах 1 и 2 переходит в устойчивое состояние. При этом потенциал на затворе транзистора 6 превышает потенциал на шийе 16, а потенциал на истоке транзистора 6, на выходной шине 15 равен потенциалу на шине 16. Бь1стродействие усилителя считывания определяется задерж.кой, необходимой для включения триггера и разряда емкости затвора транзистора 4 через транзистор 5. Так какисток транзистора 5 соединен с шиной земли, емкость затвора транзистора 4 разряжается до по-, тенциала земпи быстрее, чем аналогичная емкость известного устройства, что приводит к повышению быстродействия усилителя считывания .. Предлагаемый усилитель считывания опробован при разработке статического ЗУПВ информационной емкостью 16К. Базовым объектом для него является усилитель считывания, использованный в БИС динамического ЗУПВ информационной емкостью 64К. Лрк этом быстродействие предлагаемого усилителя считывания, равное 4 не, примерно вдвое вьш|е, чем быстродействие базового объекта Это дает возможность увеличить быстродействие ЗУПВ и производительность всей системы, следовательно, уменьшить необходимое количество таких систем.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1980 |

|

SU888206A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Усилитель считывания | 1982 |

|

SU1084889A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

| Адресный формирователь | 1981 |

|

SU970460A1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

УСИЛИТЕЛЬ СЧИТЫВАНИЯ, содержащий первый усилительный транзистор, затвор которого является пер- . вым выходом устройства и соединен со стоком второго усилительного транзистора, затвором первого ключевого транзистора и истоком первого нагрузочного транзистора, затвор второго усилительного транзистора является вторым выходом устройства и соединен ср. стоком первого усилительного транзистора, затвором второго ключевого транзистора и истоком второго нагрузочного транзистора, сток которого соединен со стоком первого нагрузочного транзистора, затвор - со стоком первого ключевого транзистора и первой обкладкой первого конденсатора, затвор первого нагрузочного транзистора соединен с пербой обкладкой второго конденсатора и стоком второго клю чевого транзистора, исток первого усилительного транзистора соединен с истоком второго усилительного транзистора, первую и вторую шины управления, отличающийся тем, что, с целью повьшения быстродействия усилителя считывания, в него введены третий и четвертый ключевые транзисторы, стоки которых являются соответственно первым и вторым входами устройства, исток третьего ключевого транзистора соединен со стоком первого ключевого транзистора, исток которого соединен с истоками первого усилитель- ., ного и второго ключевого транзистора и шиной нулевого потенциала, исток четвертого ключевого транзис- . тора соединен со стоком второго ключевого транзистора, вторая обкладка первого конденсатора соединена с истоком второго нагрузочного транзиртора, вторая обкладка второго 1С конденсатора соединена с JHCTOKOM о первого нагрузочного транзистора, 4i .сток которого подключен к первой О управления, затворы третьего с и четвертого ключевых транзисторов подключены к второй шине управления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3953839, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-10-23—Публикация

1982-09-22—Подача