S

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1986 |

|

SU1363480A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2051416C1 |

| Преобразователь кодов | 1986 |

|

SU1363481A1 |

| Аналого-цифровой частотомер | 1988 |

|

SU1712894A1 |

| Устройство для измерения амплитуды синусоидального напряжения | 1985 |

|

SU1272262A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Дельта-модулятор | 1987 |

|

SU1508350A2 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Устройство для автоматизированного контроля параметров | 1988 |

|

SU1647520A1 |

Изобретение относится к импульсной технике и может быть использова- но в устройствах автоматики и вычислительной техники. Цель изобретения - упрощение и повышение надежности преобразователя Преобразователь содержит генератор 1 импульсов, счет чики 2, 5 и 6, регистр 3 сдвига, блок 4 памяти, элементы 7 и 9 задержки, компаратор 8, регистр 10 памяти, инвертор 11, элементы И 12 и 13, шину 15 логической единицы, входы 14, информационные и управляющий выходы 16 и 17. 1 табл.. 2 ил.

О5

со

Јь

Изобретение относится к импульс- ной технике и может быть использова- но в устройствах автоматики и вычис лительной техники.

Цель изобретения - упрощение пре- образователя за счет сокращения ап- паратных затрат и повьппение его надежности.

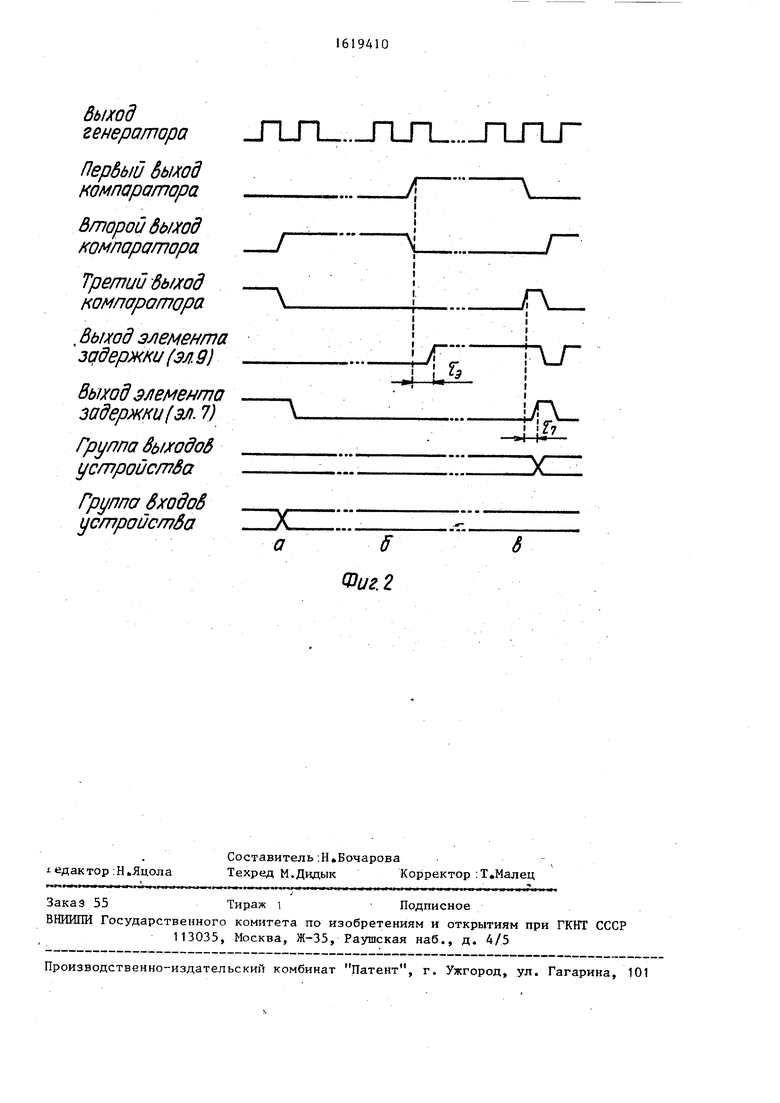

На фиг.1 представлена функциональ- ная схема преобразователя кодов; на фиг.2 - временная диаграмма его работы.

Преобразователь содержит генератор 1 импульсов, первый счетчик 2, регистр 3 сдвига, блок 4 памяти (постоянное запоминающее устройство - ПЗУ), второй и третий счетчик 5 и 6, второй элемент 7 задержки, компаратор 8, первый элемент 9 задержки, регистр 10 памяти, инвертор 11, первый и второй элементы И 12 и 13, входы 14, шину 15 логической единицы информационные и управляющий выходы 16 и 17.

Преобразователь кодов работает следующим образом

Перед началом работы счетчики 2, 5 и 6 и регистр 3 устанавливаются в нулевое состояние (входы установки в нулевое состояние не показаны).При отсутствии на входах 14 преобразуемого кода на первом и втором выходах компаратора 8 устанавливаются сигналы уровня логического нуля, а на третьем выходе - сигнал логической единицы, который через элемент 7 задержки поступает на вход синхронизации регистра 10, при этом в регистр 10 записаны нулевые сигналы с выходов счетчика 5, которые устанавливаются и на выходах 16.

Код, подлежащий преобразованию, поступает с входов 14 на вторые входы компаратора 8 (фиг.2а). При этом, если преобразуемый код не нулевой, на втором выходе компаратора 8 устанавливается сигнал уровня логической единицы (фиг.2а), а на остальных выходах компаратора 8 - сигналы уровня логического нуля. Сигнал уровня логической единицы с второго выхода компаратора 8 открывает элемент И 12, через который импульсы от генератора 1 поступают на входы синхронизации верхнего предела эквивалента преобразуемого кода в новом коде, со держащемся в блоке 4 памяти. Частично содержимое блока 4 памяти приведено в таблице.

Адрес

Содержимое

0 . о

5

0

5

0...0 0 Эквивалент кода Oi..O О 0...0 1 Эквивалент кода:О...О 1 Oi..l 0 Эквивалент кода Oi..l 1

Регистр 3 работает в режиме сдвига, на вход младшего разряда подается постоянный сигнал уровня логической единицы с шины 15. Импульсы наращивания на выходах сигналов уровня логической единицы, начиная с младшего разряда. Таким образом определяется верхний предел значения кода в формате преобразуемого кода, который через счетчик 6 поступает на первые входы компаратора.8. В ответ на втором выходе компаратора 8 устанавливается сигнал уровня логического нуля (фиг.26), который закрывает элемент И 12, а сигнал уровня логической единицы устанавливается или на третьем, или на первом выходе компаратора.8.

Если сигнал уровня логической единицы установился на третьем выходе компаратора 8, значит результат сдвига на выходах регистра 3, который через счетчик 6 поступает на первые входы компаратора 8, совпал со значением преобразуемого кода. По положительному перепаду на третьем выходе компаратора 5, который через элемент 7 задержки поступает на вход синхронизации регистра 10, эквивалент преобразуемого кода в новом коде, который с выходом блока 4 памяти через счетчик 5 поступает на соответствующие входы регистра 10, записывается на выходы регистра 10 и поступает на выходы. Элемент 7 задержки необходим для гарантирования записи в регистр 10 достоверного эквивалента преобразуемого кода в новом коде, так как тракт прохождения наиболее близкого к преобразуемому кода проходит через элементы с различным временем срабатывания.

Сигнал уровня логической единицы с третьего выхода компаратора 8 поступает на вход начальной установки счетчика 2, а через инвертор 11 - на вход начальной установки регистра 3 и устанавливает их в нулевые состояния. Положительный перепад на вы516

ходе 2 устройства свидетельствует о том, что на выходах 16 установлено преобразованное значение преобразуе- мого кода.

Сигнал уровня логической единицы установился на первом выходе компа- ратора 1 и поступает на входы вычи- тания счетчиков 5 и:6 Сигнал уровня логической единицы с первого выхо- да компаратора 8 через элемент 9 за держки поступает также на входы синхронизации счетчиков 5 и 6, переводя их с режима параллельной записи в режим счета Счетчик 5 осуществляет вычитание от значения эквивалента преобразуемого кода в новом коде, соответствующем максимальному значению преобразуемого кода в уста- новленном ферменте Счетчик 6 сравнивается со значением преобразуемого кода на вторых входах компаратора 8, на третьем выходе компаратора 8 () устанавливается сигнал с уровнем логической единицы, по которому регистр 3 и счетчик 2 устанавливаются в нулевое состояние, а на первом, выходе компаратора 8 устанавливается сигнал с уровнем логического нуля (). По положительному перепаду на третьем выходе компаратора 8, который через элемент 7 за-

держки поступает на вход синхронизации регистра 10, результат вычитания с выходов счетчика 5 записывается на выходы регистра 10 и поступает на выходы 16 (). На выходе 17 появляется положительный перепад, свидетельствующий о наличии новой информации на выходах 16 Элемент 9 задержки необходим для того, чтобы счетчик 5 не переводился в режим параллельной записи до записи в регистр 10 преобразованного кода Для этого время задержки элементов 9

задержки равняется Л- о л

ЭЛ.9

2Ј

Ц.7

1U

15

20

25

30

35

40

45

106

Формула изобретения Преобразователь кодов, содержащий генератор импульсов, выход которого соединен с первым входом первого элемента И, выход которого соединен с входами синхронизации регистра сдвига ч первого счетчика, выходы которого соединены с входами блока памяти, выходы блока памяти соединены с соответствующими информационными входами второго счетчика, выходы которого соединены с соответствующими информационными входами регистра памяти, выходы которого являются информационными выходами преобразователя, третий счетчик, выходы которого соединены с первыми входами компаратора, вторые входы которого являются входами преобразователя, первый выход компаратора соединен с первым входом второго элемента И, выход которого соединен с вычитающими входами второго и третьего счетчиков, отличающийся тем, что, с целью упрощения и повышения надежности преобразователя, в него введены инвертор, шина логической единицы и элементы задержки, вход первого элемента задержки подключен к первому выходу компаратора, выход соединен с синхронизирующими входами второго и третьего счетчиков, второй выход компаратора соединен с вторым входом первого элемента И, третий выход компаратора соединен непосредственно с входом начальной установки первого счетчика, через второй элемент задержки - с синхронизирующим входом регистра памяти через инвертор - с входом начальной установки регистра сдвига и является управляющим выходом преобразователя, информационный вход регистра сдвига подключен к шине логической единицы, выходы соединены с информационными входами третьего счетчика, второй вход второго элемента И подключен к выходу генератора импульсов

Выход генератора

Пербый Выход компаратора

Второй Выход компаратора

Третий Выход компаратора

, Выход элемента зддержки (эл9)

Выход элемента задержки Ian. 7)

Группа выходов устройства

Группа Входов устройства

ПЛnjn...

| Преобразователь кодов | 1986 |

|

SU1363480A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-01-07—Публикация

1989-02-13—Подача