Изобретение относится к вычислительной технике и может быть использовано в автоматических устройствах преобразования информации,

Цель изобретения - повьшение быстродействия преобразователя.

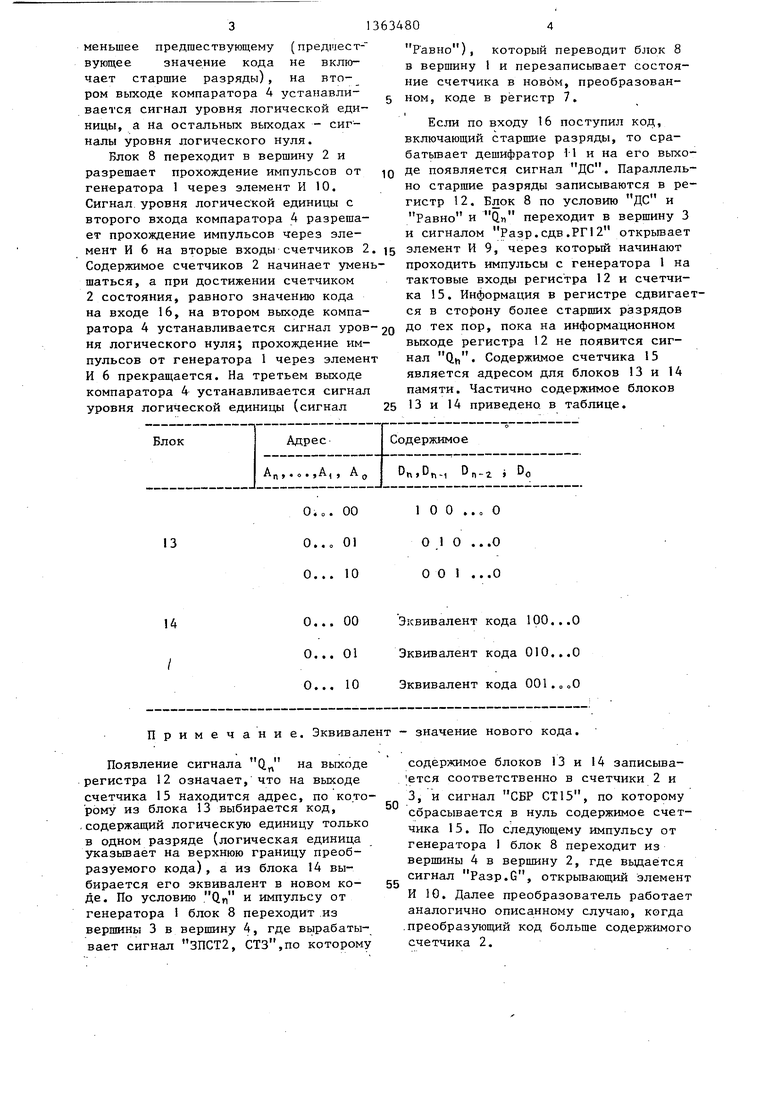

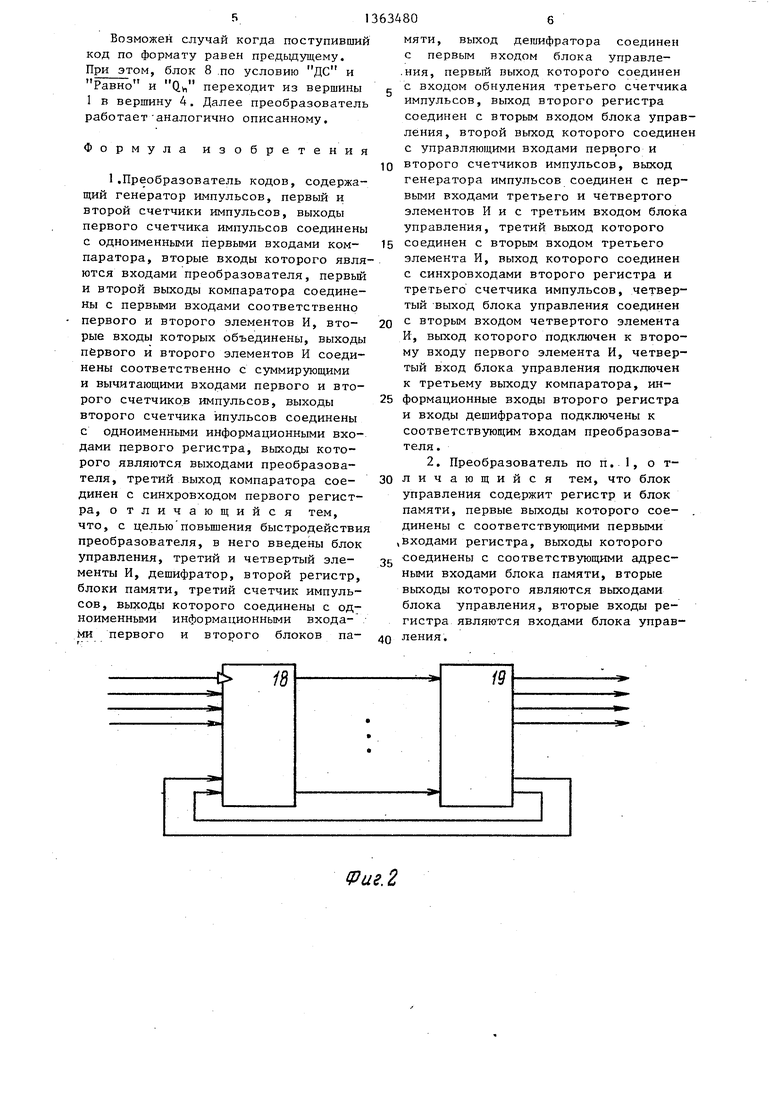

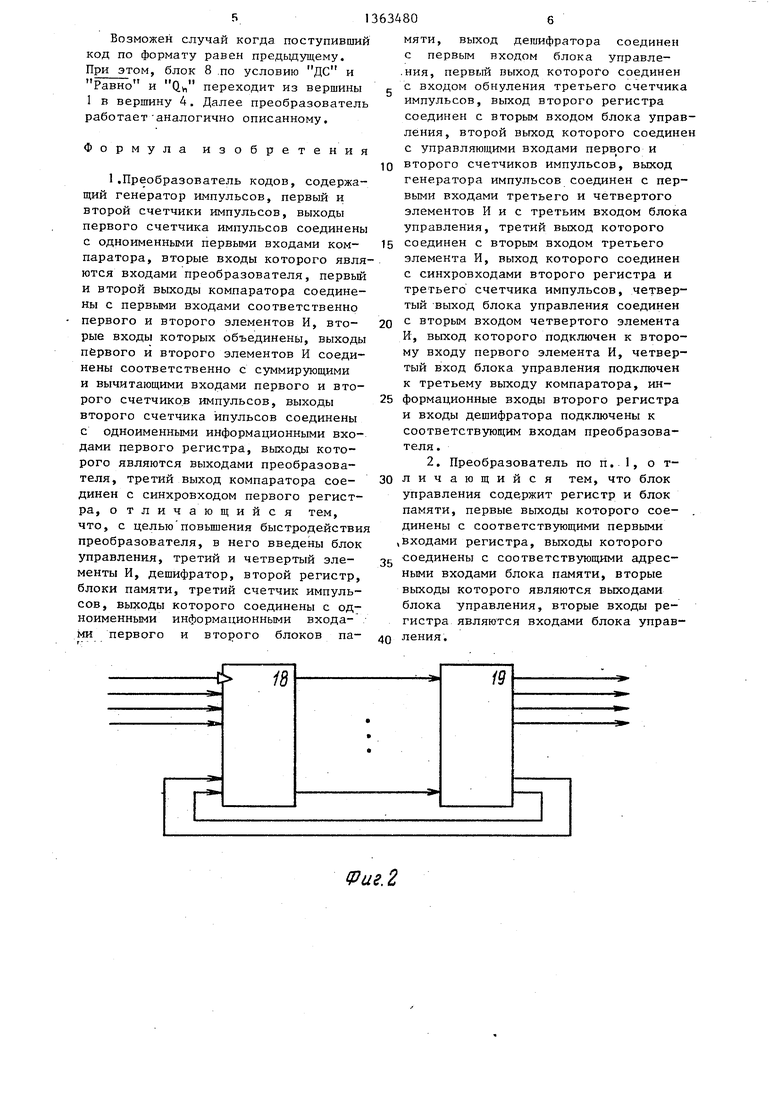

На фиг.1 представлена функциональная блок-схема преобразователя кодов; на фиг.2 - блок-схема блока управления; на фиг.З - граф-алгоритм блока управления.

Преобразователь кодов содержит генератор 1 импульсов, первый 2 и второй 3 счетчики импульсов, компа- ратор 4, первый 5 и второй 6 элементы И, первый регистр 7, блок 8 управления, третий 9 и четвертый 10 элементы И, дешифратор 11, второй регистр 12, первый 13 и второй 14 блоки памяти и третий счетчик 15 импульсов. На фиг.1, обозначены вход 16 и выход 17 преобразователя.

Блок 8 управления содержит регист 18 и блок 19 памяти, выполненный на ПЗУ.

Блок 8 управления работает в синхронном режиме от тактовых импульсов с генератора 1, т.е. переход от вершины к вершине граф-алгоритма проис- ходит при наличии необходимого условия и импульса от генератора 1.

Граф-алгоритм работы блока управления 8 (фиг.2) состоит из четырех вершин. Обозначения сигналов „в граф- алгоритме: Равно - сигнал с третье го выхода компаратора 4; Равно - .отсутствие сигнала на третьем выход компаратора 4; ДС - сигнал на выходе дешифратора 11; ДС - отсут- ствие сигнала на выходе дешифратора 11; Разр.б - сигнал к элементу 10 от блока 8; ЗПСТ2, СТЗ - сигнал к счетчикам 2,3 от блока СТ 15 сигнал к счетчику 15 от блока 8; О.,, - сигнал на информационном выходе регистра 12; Q - отсутствие сигнала на информационном выходе регистра 12; Разр.сдв.РП 2 - сигнал к элементу 9 от блока 8.

Преобразователь кодов работает следующим образом.

До начала работы счетчики 15, 2, 3 и регистр 12 устанавливаются в нуль (входы установки в нуль не по- казаны).

При отсутствии на входе 16 преобразуемого кода на первом и втором выходах компаратора 4 устанавливаются сигналы уровня логического нуля, а на третьем выходе - сигнал логической единицы, который поступит на вход синхронизации регистра 7 памяти, при этом в регистр 7 записываются нулевые сигналы со счетчика 3, которые установятся и на выходе 17.

Код, подлежащий преобразованию, поступает по входу 16 на входы компаратора 4. При этом если преобразуемый код не нулевой, на цервом выходе компаратора 4 устанавливается сигнал уровня логической единицы, а на остальных выходах компаратора 4-сигна- лы уровня логического нуля.

Далее определяется форма кода, поступившего на вход 16. Этот код может быть п-й разрядности. Разряды кода, поступающие по шинам с i-й по п-ю, являются старшими разрядами, остальные разряды - младшими. Старпие разряды определяют основное время, затрачиваемое на преобразование кодов. Итак, если формат поступившего кода не включает старших разрядов, дешифратор 11 выдает в блок 8 сигнал логического нуля. По граф-алгоритму, по условию ДС и Равно блок 8 переходит из вершины 1 в вершину 2, где вырабатывает сигнал Разр.С, который открывает элемент И 10. Так как сигнал логической единицы при- сутствует на первом выходе компаратора 4 , то открывается элемент И 5. Импульсы от генератора 1, через элементы И 10 и 5 поступают на первые входы Счетчиков 2 и 3. При достижении счетчиком 2 числа, равного поступившему преобразуемому коду, на третьем выходе компаратора 4 устанавливается сигнал уровня логической единицы, а на первом выходе - сигнал уровня логического нуля, который запрещает дальнейшее прохождение импульсов через элемент И 5 на счетчики 2 и 3. Блок 8 возвращается в вершину 1, так .как появился сигнал Равно. На выходах счетчика устанавливается поданное по входу 16 число в новом преобразованном коде, которое с выходов счетчика по сигналу уровня логической единицы с третьего выхода компаратора 4 переписьшается в регистр 7, на выходах которого и выходе 17 устанавливается значение преобразованного сигнала в новом коде.

При смене на входе 16 кода, подлежащего преобразованию, на значение.

меньшее предшествующему (предшествующее значение кода не включает старшие разряды), на втором выходе компаратора 4 устанавливается сигнал уровня логической единицы, а На остальных выходах - сигналы уровня логического нуля.

Блок 8 переходит в вершину 2 и разрешает прохождение импульсов от генератора 1 через элемент И 10, Сигнал уровня логической единицы с второго входа компаратора 4 разрешает прохождение импульсов через элемент И 6 на вторые входы счетчиков 2. 15 элемент И 9, через который начинают Содержимое счетчиков 2 начинает умень- проходить импульсы с генератора 1 на

тактовые входы регистра 12 и счетчика 15. Информация в регистре сдвигается в сторону более старших разрядов

шаться, а при достижении счетчиком 2 состояния, равного значению кода на входе 16, на втором выходе компаратора 4 устанавливается сигнал уров-2оД° пор, пока на информационном ня логического нуля; прохождение им-выходе регистра 12 не появится сиг- пульсов от генератора 1 через элементнал Содержимое счетчика 15 И 6 прекращается. На третьем выходеявляется адресом для блоков 13 и 14 компаратора 4 устанавливается сигналпамяти. Частично содержимое блоков уровня логической единицы (сигнал 2513 и 14 приведено в таблице.

13

0.0. 00 0... 01

о... 10

о... 00 Эквивалент кода 100...О О... 01 Эквивалент кода 010...О О... 10 Эквивалент кода 001.„«О

Примечание. Эквивалент - значение нового кода.

Появление сигнала Q на выходе регистра 12 означает, что на выходе

счетчика 15 находится адрес, по которому из блока 13 выбирается код,

,содержащий логическую единицу только в одном разряде (логическая единица указьшает на верхнюю границу преобразуемого кода), а из блока 14 выбирается его эквивалент в новом коде. По условию Qn и импульсу от генератора 1 блок 8 переходит из вершины 3 в вершину 4, где вырабатывает сигнал ЗПСТ2, СТЗ,по которому

Равно), который переводит блок 8 в вершину 1 и перезаписывает состояние счетчика в новом, преобразованном, коде в регистр 7.

Если по входу 16 поступил код, включающий старшие разряды, то сра- батьшает дешифратор М и на его выходе появляется сигнал ДС. Параллельно старшие разряды записываются в регистр 12. Блок 8 по условию ДС и Равно и Qn переходит в вершину 3 и сигналом Разр.сдв. открьгоает

1 о о ..„ о

01 о ...о 00 1 ...о

50

55

содержимое блоков 13 и 14 записыва- ется соответственно в счетчики 2 и 3, и сигнал СВР СТ15, по которому сбрасывается в нуль содержимое счетчика 15. По следующему импульсу от генератора 1 блок 8 переходит из вершины 4 в вершину 2, где выдается сигнал Разр.С, открьгоающий элемент И 10. Далее преобразователь работает аналогично описанному случаю, когда .преобразующий код больше содержимого счетчика 2.

Возможен случай когда поступивший код по формату равен предьщущему. При этом, блок 8 .по условию ДС и Равно и QV, переходит из вершины 1 в вершину 4. Далее преобразователь работает аналогично описанному.

Формула изобретения

1.Преобразователь кодов, содержащий генератор импульсов, первый и второй счетчики импульсов, выходы первого счетчика импульсов соединены с одноименными первыми входами компаратора, вторые входы которого являются входами преобразователя, первый и второй выходы компаратора соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых объединены, выходы первого и второго элементов И соединены соответственно с суммирующими и вычитающими входами первого и второго счетчиков импульсов, выходы второго счетчика ипульсов соединены с одноименными информационными входами первого регистра, выходы которого являются выходами преобразователя, третий выход компаратора соединен с синхровходом первого регистра, о тличающийся тем, что, с целью повышения быстродействия преобразователя, в него введены блок управления, третий и четвертый элементы И, дешифратор, второй регистр, блоки памяти, третий счетчик импульсов, вькоды которого соединены с одноименными информационными входа- ми первого и второго блоков .2

мяти, выход дешифратора соединен с первым входом блока управле- .ния, первый выход которого соединен с входом обнуления третьего счетчика импульсов, выход второго регистра соединен с вторым входом блока управления, второй выход которого соединен с управляющими входами и

второго счетчиков импульсов, выход генератора импульсов соединен с первыми входами третьего и четвертого элементов И и с третьим входом блока управления, третий выход которого

соединен с вторым входом третьего элемента И, выход которого соединен с синхровходами второго регистра и третьего счетчика импульсов, четвертый выход блока управления соединен

с вторым входом четвертого элемента И, выход которого подключен к второму входу первого элемента И, четвертый вход блока управления подключен к третьему выходу компаратора, информационные входы второго регистра и входы дешифратора подключены к соответствующим входам преобразователя .

2. Преобразователь по п. 1, о тличающийся тем, что блок управления содержит регистр и блок памяти, первые выходы которого сое- . динены с соответствующими первыми Входами регистра, выходы которого

соединены с соответствующими адресными входами блока памяти, вторые выходы которого являются выходами блока управления, вторые входы регистра являются входами блока управления.

)СлРаёно/(и

Равно

Раёнс

.9

Ра8но

ЗПСТ2, СТЗ СВР CTI5

Риг.д

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кодов | 1989 |

|

SU1619410A1 |

| Преобразователь двоичного кода в код с произвольным весом младшего разряда | 1985 |

|

SU1325708A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Программно-управляемый генератор синусоидальных колебаний | 1985 |

|

SU1451830A1 |

| Преобразователь кода во временной интервал | 1980 |

|

SU928635A1 |

| Быстродействующий аналого-цифровой преобразователь | 1985 |

|

SU1254584A1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2205500C1 |

| Аналого-цифровой преобразователь | 1983 |

|

SU1156258A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

Изобретение относится к вычислительной технике и может быть использовано в автоматических устройст. вах преобразования информации. Изоб- ретение обеспечивает предварительное определение формата преобразуемого кода, за счет чего повышается быстродействие преобразователя. Преобразователь кодов содержит генератор 1 импульсов, три счетчика 2,3 и 15 импульсов, компаратор 4, четыре элемента И 5,6,9 и 10, два регистра 7 и 12, блок 8 управления, дешифратор 11 и два блока 13 и 14 памяти. Блок 8 управления содержит регистр и блок . памяти. 1 з.п. ф-лы, 3 ил., 1 табл. (Л САЭ 05 СО 4 00 о Фиг. Г

| Устройство для отбора проб | 1986 |

|

SU1372217A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ПРИБОР ДЛЯ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ ЗВУКОВ | 1923 |

|

SU1974A1 |

| Устройство для преобразования кодов | 1982 |

|

SU1078613A1 |

Авторы

Даты

1987-12-30—Публикация

1986-04-29—Подача