I

(21)4436660/24

(22)06.06.88

(46) 15.0U91. БюЛо № 2

(71)Харьковский политехнический институт им. В.И. Ленина

(72)В.Ф. Бохан, ИоГ. Либерг, ИоЕ„ Фролова и ЕсАс Бохан

(53)681.327„66(08808)

(56) Авторское свидетельство СССР № 1300456, кл„ G 06 F 7/00, 1986.

IEEE Trans с Comput., 1983, С-32, № 11, .ро 1038-1046, фиг, 9С

(54)ПРОГРАММИРУЕМАЯ ЛОГИЧЕСКАЯ МАТРИЦА

(57) Изобретение относится к вычислительной технике и может быть использовано при построении дискретных устройств с встроенными средствами тестирования ь Пелыо изобретения является сокращение времени и повышение достоверности тестирования. Для достижения поставленной цели в программируемую логическую матрицу (ПЛМ) введен сигнатурный анализатор, информационные входы которого соединены с выходами группы элементов II ПЛМ проверяется тестовой последовательностью постоянной длины, не зависящей от реализуемых в ней функцийс 2 ил„, 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство анализа результатов тестирования для локализации двукратных неисправностей | 2016 |

|

RU2633908C1 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| УСТРОЙСТВО АНАЛИЗА РЕЗУЛЬТАТОВ ТЕСТИРОВАНИЯ ДЛЯ ПОИСКА НЕИСПРАВНЫХ БЛОКОВ | 2013 |

|

RU2540805C2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство для умножения | 1987 |

|

SU1501043A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1980 |

|

SU907556A1 |

| АВТОМАТИЗИРОВАННЫЙ КОМПЛЕКС КОНТРОЛЯ И ДИАГНОСТИКИ (ВАРИАНТЫ) | 2003 |

|

RU2257604C2 |

| МОДУЛЬ ВВОДА-ВЫВОДА СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1991 |

|

RU2032201C1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА ДИАГНОСТИРОВАНИЯ | 2007 |

|

RU2365966C2 |

| Программируемая логическая матрица | 1986 |

|

SU1381481A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств с встроенными средствами тестирования.

Целью изобретения является сокращение времени и повышение достоверности тестирования

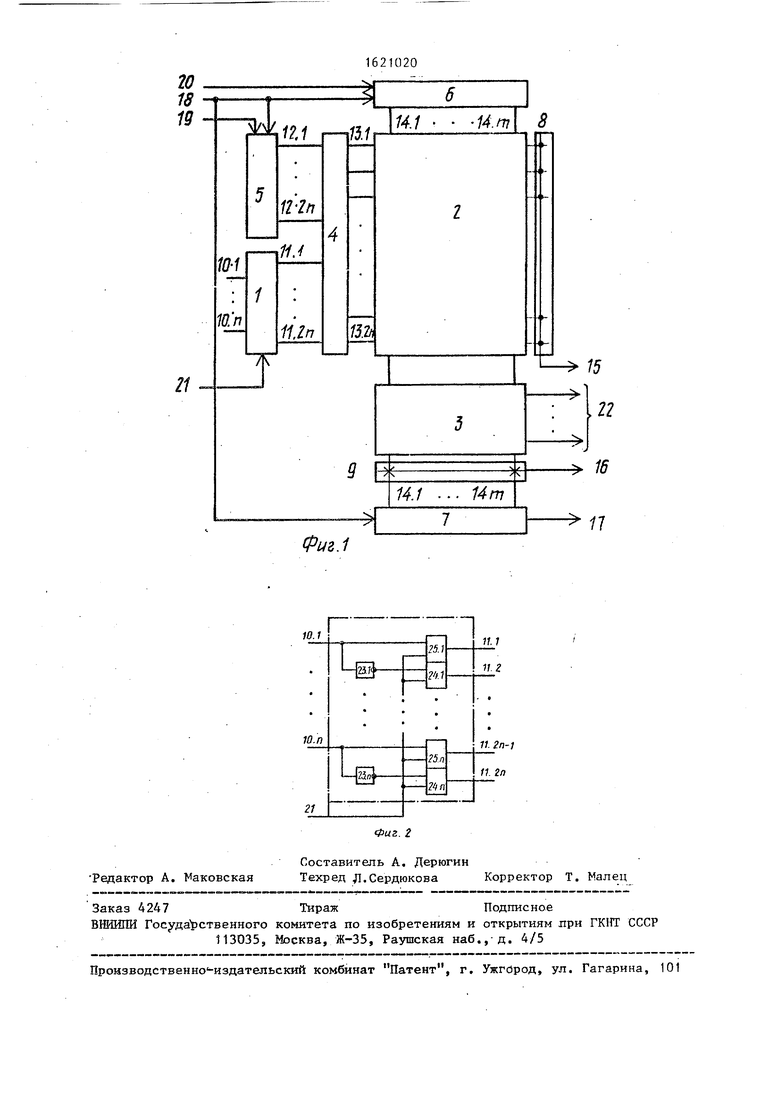

На фиг. 1 приведена структурная схема программируемой логической матрицы; на фиг. 2 - схема одноразрядных дешифраторов.

Программируемая логическая матрица (ПЛМ) содержит группу одноразрядных дешифраторов 1, группу элементов И 2, первую 3 и вторую 4 группы элементов ИЛИ, первый 5 и второй 6 регистры сдвига, сигнатурный анализатор 7, элементы И 8, ИЛИ 9С На фиг. 1 показаны также информационные входы-ПЛМ 10, первые 11 и вторые 12 входы -т U1- ментов ИЛИ второй группы 4, входы 13

и выходы 14 элементов II группы 23 первый 15, второй 1 и третий 17 конт- рольные выходы ПЛМ, тактовый 18, первый 19 и второй 20 тестовые входы и вход 21 режима работы ПЛМ, а также информационные выходы 22 ПЛМ„ Группа одноразрядных дешифраторов 1 (фиг.2) состоит из инверторов 23 и элементов И 24 и 25. Группа элементов И 2 и первая группа элементов ИЛИ 3 образуют матрицы И и ИЛИ ПЛМ соответст- веннОс

ПЛМ может находиться в рабочем режиме и в режиме тестирования.

В рабочем режиме на входе 21 устанавливается значение логической 1 для обеспечения передачи сигналов с входов 10.1-Ю.п через группу 1 одноразрядных дршифраторов. Первый регистр 5 сдвига устанавливается в нулевое состояние тля обеспечения передаю

чи сигналов с выходов группы одноразрядных дешифраторов через элементы ИЛИ вто- рой группы 4 на входы матрицы И 2.

Второй регистр 6 сдвига устанавливается в единичное состояние для установления на входах 12.1-12„п единичных значений. В рабочем режиме тактовые импульсы на вход 18 не подаются и состояние регистров 5 и 6 не меня- J ется. Значения функций, реализуемых ПЛМ, получаются на выходах 2.2.1 и

Тестирование ТШМ осуществляется следующим образом.

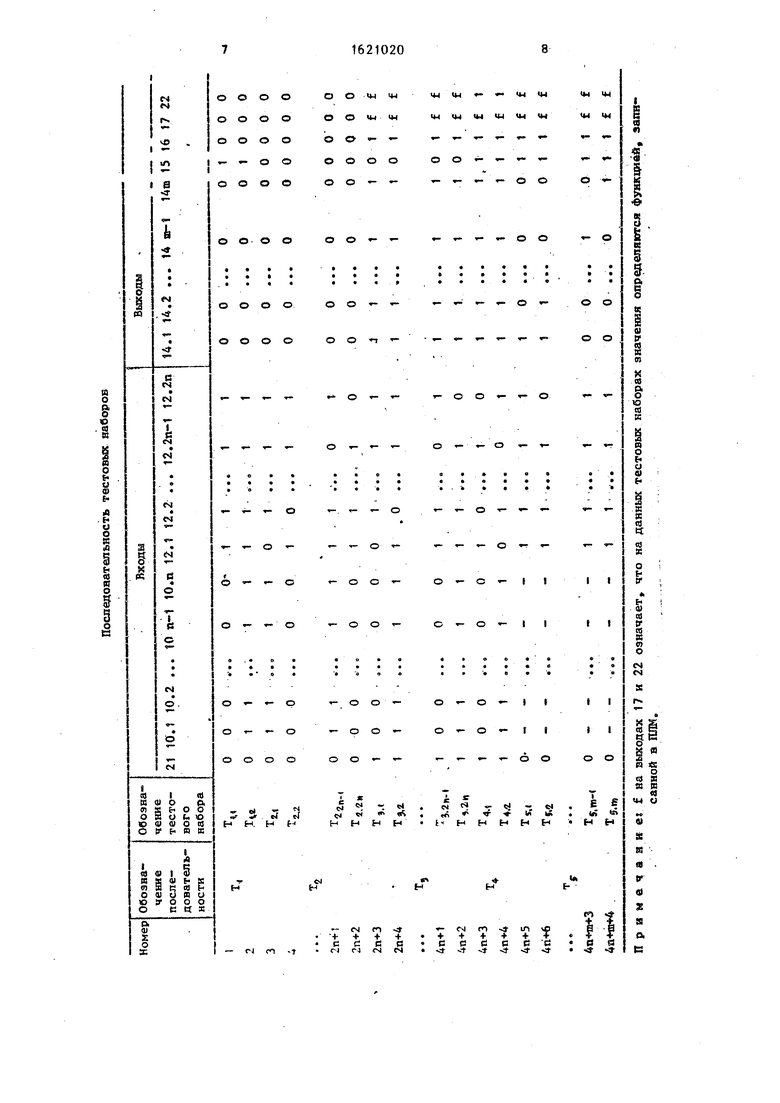

Для подачи последовательности тес- товых наборов, приведенных в таблице, используются информационные входы устройства 10.1-Ю.п и управляющие входы 19-21, Через управляющие входы 19-21 в регистры 5 и 6 заносятся со- 2 ответствующие части тестового набора и осуществляется тестирование, результаты которого наблюдаются на информационных выходах 22.1-22.1 и контрольных выходах 15-17.

Последовательность тестовых наборов состоит из пяти подпоследовательностей Тестовые наборы, относящиеся к одной подпоследовательности, имеют соответствующее обозначение, состоя- щее из двух индексов, каждый из которых указывает на номер подпоследовательности, а второй - на номер .тестового набора в данной подпоследовательности . Например, обозначение Т 4,г означает,что данный тестовый набор принадлежи четвертой подпоследовательности.

В ПЛМ возможны следующие виды не-1 исправностей: контактные неисправности на входах-выходах элементов и на горизонтальных и вертикальных линиях матриц И и ИЛИ; неисправности точек пересечения, под которыми понимаются дефекты коммутации в местах пересечения ортогональных проводников в матрицах И и ИЛИ, т. е. исчезновение полупроводникового элемента там, где он должен быть, или появление полупроводникового элемента там, где его не должно быть. Неисправности точек пересечения в ТШМ называют контактными неисправностями

В зависимости от того, в каких элементах устройства появляются описанные неисправности, все множество неисправностей можно разбить на четыре подмножества.

В первое подмножество входят все константные неисправности, которые

могут появиться в одноразрядных дешифраторах 1, в элементах ИЛИ второй группы 4, в первом регистре 5 сдвига, на входах 13, в элементе ИЛИ 8„ Для обнаружения всех неисправностей в . перечисленных элементах используются тестовые наборы , причем неисправности типа константного О на выходах первого регистра 5 сдвига обнаруживаются на тестовом наборе Т , неисправности типа константного О на входах 10 - на тестовом наборе TH|i,, на тестовых наборах Тг обнаруживаются константные 1 на первых входах элементов 25 и 24, неисправности типа константного О на входах-выходах элементов 24 - на тестовом наборе Т4 ( , неисправности типа константного О на входах-выходах элементов 25 - на тестовом наборе Т 4,2. Остальные неисправности данного подмножества обнаруживаются двумя и более тестовыми наборами из ,, Наличие неисправностей наблюдается на выходе 15,

Во второе подмножество входят все константные неисправности, которые могут появиться на вертикальных линиях 14, на выходах второго регистра 6 сдвига и элемента ИЛИ 9. Для обнаружения указанных неисправностей ис-1- пользуют тестовые наборы Т и 1$, причем на тестовом наборе Т ц обнаруживаются любые неисправности тип константной 1, а на тестовых набо- pax T - все неисправности типа константного О 0 .Наличие неисправносте наблюдается на выходе 16.

В третье подмножество входят все неисправности точек пересечения в матрице И. Для обнаружения неисправности данного типа используются тестовые наборы Tj, причем на каждом тестовом наборе из Т3 активизируется только одна горизонтальная линия в матрице И„ При подаче тактового импульса информация о наличии и отсутствии « вязей в точках пересечения в матрице И заносится в сигнатурный анализатор 7. После подачи всех наборов из в сигнатурном анализаторе получаем сигнатуру, которую затем (на тестовых наборах 14 и Т) последовательно выводим через выход 17, где осуществляется контроль неисправностей точек пересечения матрицы И. В четвертое подмножество входят все неисправности точек пересечения

рицы ИЛИ. Для обнаружения этих Ф справностей используются тестовые оры Tf, причем на каждом тестонаборе активизируется только одвертикальная линия в матрице ИЛИ. ичие и отсутствие связей в точках есечения матрицы ИЛИ контролируетна выходах 22 устройства.

п э р р и с д с э в с с в с г г т н и г л л д ми в м с И вх вы -с вы ма

Так как условия активизации неисправностей разных подмножеств в некоторых случаях совпадают, то стало возможным объединение тестовых наборов для различных подмножеств в общие группы. Это позволяет одновременно обнаруживать неисправности разных подмножеств на одних и тех же тестовых наборах по разным выходам, что ведет к сокращению числа тестовых наборов и, следовательно, к сокращению времени тестирования

г

I

В ПЛМ сигнатурный анализатор 7 позволяет обнаружить любые неисправности точек пересечения в матрице И„ Так как на тестовых наборах из Т3 на каждом также активизируется только одна строка матрицы И, то на входах сигнатурного анализатора 7 каждый раз устанавливается двоичное слово, соответствующее расположению связей в точках пересечения выбранной строки. Это слово на каждом такт записывается в сигнатурный анализатор 7. Любая неисправность приводит к изменению значения на входах сигнатурного анализатора 7S что в конечном итоге отразится на выходной сигнатуре.

Таким образом, любые неисправности точек пересечения в матрице И предлагаемого устройства в отличие от прототипа могут быть обнаружены.

020

Ф

0

5

0

6

ормула изобретения Программируемая логическая матрица, содержатая группу элементов К, первую и вторую группы элементов ИЛИ, элемент И, элемент ИЛИ, первый и второй регистры сдвига и группу однорач- рядных дешифраторов, информационные и управляющие входы которых являются соответствующими информационными входами и входом режима работы программируемой матрицы, а выходы соединены с первыми входами соответствующих элементов ИЛИ второй группы, вторые входы которых соединены с соответствующими выходами первого регистра сдвига, информационные и тактовые входы первого и второго регистров сдвига являются соответственно первым и вторым тестовыми входами и тактовым входом программируемой логической матрицы, выходы элементов ИЛИ второй группы соединены с соответствующими входами элементов II группы и элемента И, выходы элементов И группы соединены с соответствующим выходами второго регистра сдвига и с входами элементов ИЛИ первой группы и элемента ПЛИ, выходы элементов ИЛИ первой группы и выходы элементов И и ИЛИ являются соответственно информационными выходами и первым и вторым контрольными выходами программируемой логической матрицы, о т л и ч а ю щ а я с я тем, что, с целью сокращения времени и повышения достоверности тестирования программируемой логической матрицы, в нее введен сигнатурный анализатор, информационные входы которого соединены с выходами соответствующих элементов И группы, тактовый вход - с тактовым входом первого регистра сдвига, а выход является третьим контрольным с выходом программируемой логической матрицы

5

0

5

0

П р и м е ч а

я и е Ј на выходах 17 и 22 означает что на данных тестовых наборах значения определяются функцией, записанной в ПЛМ.

3d

1

{ЪЛ г-i/З./

И.1

7ч

21

Фиг.1

Г

1621020 ±I

П

251

П

п г

11 2п-1

25 п

11 2л

и я

Авторы

Даты

1991-01-15—Публикация

1988-06-06—Подача