Изобретение относится к области тестирования дискретных объектов большой размерности.

При тестировании принято на входы объекта или на входы его частей (блоков) подавать тестовые воздействия (тесты), а с выходов объекта или его блоков (контрольных точек) снимать тестовую реакцию, которая анализируется (сопоставляется с эталонной реакцией исправного объекта) для решения одной или двух задач: 1) проверка исправности объекта, 2) локализация (или поиск) неисправностей (отказавших выходов или блоков), если проверяемый объект оказался неисправным. Решение второй задачи особенно актуально, если подразумевается восстановление неисправного объекта путем, например, ручной замены отказавшего блока или автоматической реконфигурации объекта, при которой неисправные блоки отключаются от объекта, а вместо них подключаются соответствующие резервные блоки.

В технической диагностике в качестве устройства анализа результатов тестирования чаще всего применяют так называемые сигнатурные анализаторы (СА). СА представляет (заменяет) длинную выходную последовательность на выходе (контрольной точке) объекта в виде короткого слова (сигнатуры). На основании сопоставления сигнатуры, полученной в результате тестирования, с ее эталонным значением, полученным заранее на заведомо исправном объекте или его модели, делается вывод о техническом состоянии тестируемого объекта. СА реализуется в виде регистра сдвига с обратными связями. Различают СА одновходовые (одноканальные), которые «сжимают» одну выходную тестовую последовательность во времени, и многовходовые (многоканальные), «сжимающие» несколько последовательностей с разных выходов объекта, подающихся на входы СА, и во времени, и в пространстве. Эффективность обнаружения ошибки в последовательности сжимаемых данных называется достоверностью СА (Ярмолик В.Н., Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 145-146). Достоверность оценивается как вероятность необнаружения ошибок в анализируемой последовательности:  , где

, где  - число разрядов (или длина) СА. Причем эта вероятность инвариантна относительно сжимаемой последовательности и конструкции СА (числа и вида его обратных связей) и уже при

- число разрядов (или длина) СА. Причем эта вероятность инвариантна относительно сжимаемой последовательности и конструкции СА (числа и вида его обратных связей) и уже при  значение р=1/216=0,0000152 достаточно близко к нулю.

значение р=1/216=0,0000152 достаточно близко к нулю.

Задача сжатия выходной тестовой реакции может решаться двояко. В первом варианте к каждому из N выходов объекта присоединяется одновходовой сигнатурный анализатор длины  . В этом варианте тестирования решается как задача проверки исправности объекта, так и задача локализации неисправностей, в данном случае - это поиск выходов объекта, на которых выдаются неправильные тестовые реакции (будем называть их неисправными выходами). Сигнатуру будем называть неисправной, если она отлична от эталонной. Если при тестировании k из N сигнатур оказались неисправными, то неисправны те выходы объекта, которые подключены ко входам СА, зафиксировавших неисправные сигнатуры. Таким образом, и в классе одиночных неисправностей (когда в объекте неисправен один выход), и в классе кратных неисправностей (когда в объекте одновременно неисправны несколько выходов) рассматриваемый вариант организации проверки объекта обеспечивает решение как задачи проверки его исправности, так и задачи локализации в нем неисправностей произвольной кратности. При этом затраты, исчисленные в количестве разрядов всех анализаторов (без учета затрат на хранение N эталонных сигнатур и их сопоставление с результирующими сигнатурами), составляют

. В этом варианте тестирования решается как задача проверки исправности объекта, так и задача локализации неисправностей, в данном случае - это поиск выходов объекта, на которых выдаются неправильные тестовые реакции (будем называть их неисправными выходами). Сигнатуру будем называть неисправной, если она отлична от эталонной. Если при тестировании k из N сигнатур оказались неисправными, то неисправны те выходы объекта, которые подключены ко входам СА, зафиксировавших неисправные сигнатуры. Таким образом, и в классе одиночных неисправностей (когда в объекте неисправен один выход), и в классе кратных неисправностей (когда в объекте одновременно неисправны несколько выходов) рассматриваемый вариант организации проверки объекта обеспечивает решение как задачи проверки его исправности, так и задачи локализации в нем неисправностей произвольной кратности. При этом затраты, исчисленные в количестве разрядов всех анализаторов (без учета затрат на хранение N эталонных сигнатур и их сопоставление с результирующими сигнатурами), составляют  . Такое устройство реализации тестирования описано в (Ярмолик В.Н., Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 208).

. Такое устройство реализации тестирования описано в (Ярмолик В.Н., Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 208).

Так как в проверяемом дискретном устройстве, как правило, выходов (контрольных точек) оказывается достаточно много, то аппаратурно выгоднее применять второй вариант сжатия тестовой реакции, т.е. многовходовой СА, который, имея такой же объем аппаратуры, что и одновходовой СА, может анализировать реакцию сразу  контрольных точек, где

контрольных точек, где  - число разрядов (триггеров) в СА,

- число разрядов (триггеров) в СА,  . Как показано в литературе, многовходовой СА практически не снижает достоверность контроля по сравнению с одновходовым.

. Как показано в литературе, многовходовой СА практически не снижает достоверность контроля по сравнению с одновходовым.

Устройством-аналогом, реализующим второй вариант сжатия тестовой реакции, является устройство, описанное в работе (Аксенова Г.П., Контролепригодная архитектура для самотестирования в программируемых логических матричных структурах, «Автоматика и телемеханика», 2010, №12, стр. 154-165).

В этой работе проверяемым объектом является контролепригодная программируемая логическая матрица (ПЛМ), выходы ее конфигурируемых логических блоков (КЛБ) наблюдаемы, т.е. являются выходами ПЛМ, а в качестве анализатора тестовой реакции выступает совокупность  -разрядных многовходовых СА, множество входов которых без пересечений охватывает все N выходов ПЛМ (т.е. каждый вход СА соединен с одним выходом ПЛМ). Затраты З2 на реализацию такого устройства минимальны, когда суммарное число разрядов всех СА равно N, а N кратно

-разрядных многовходовых СА, множество входов которых без пересечений охватывает все N выходов ПЛМ (т.е. каждый вход СА соединен с одним выходом ПЛМ). Затраты З2 на реализацию такого устройства минимальны, когда суммарное число разрядов всех СА равно N, а N кратно  . Итак, З2мин=N. И если задача проверки исправности (с достоверностью многовходового СА) решается полностью, то задача локализации неисправностей не решается даже для класса одиночных неисправностей. Действительно, при неисправности только одного выхода ПЛМ единственная неисправная сигнатура свидетельствует лишь о том, что неисправности находятся среди группы выходов ПЛМ, которые соединены со входами СА, выдавшего эту неисправную сигнатуру. Т.е. экономный в реализации многовходовой СА, сжимая тестовую реакцию и во времени, и в пространстве, « замазывает» след от неисправного элемента.

. Итак, З2мин=N. И если задача проверки исправности (с достоверностью многовходового СА) решается полностью, то задача локализации неисправностей не решается даже для класса одиночных неисправностей. Действительно, при неисправности только одного выхода ПЛМ единственная неисправная сигнатура свидетельствует лишь о том, что неисправности находятся среди группы выходов ПЛМ, которые соединены со входами СА, выдавшего эту неисправную сигнатуру. Т.е. экономный в реализации многовходовой СА, сжимая тестовую реакцию и во времени, и в пространстве, « замазывает» след от неисправного элемента.

Наиболее близким к заявляемому устройству является устройство, описанное в работе (Аксенова Г.П. «Матричный способ локализации неисправностей в ПЛИС», «Автоматика и телемеханика», 2013, №9, стр. 119-124), в котором используются многовходовые СА и решена задача поиска одиночных неисправностей (локализация неисправных выходов объекта).

Будем считать, что проверяемый объект для устройства-прототипа и заявляемого устройства один и тот же, т.е. это - контролепригодная ПЛМ. Для пояснения возможности локализации неисправностей условно расположим в пространстве все N наблюдаемых выходов проверяемого объекта в виде некоторой матрицы выходов (не путать условную матрицу выходов с реальным конструктивным размещением КЛБ и их выходов в кристалле). Присвоив выходам объекта порядковые номера, заменим условную матрицу выходов (m×n)-матрицей их номеров, где m - число ее строк, a n - число столбцов. Если N<mn, то последняя строка будет не полностью заполнена. Не умаляя общности, будем считать, что N=mn.

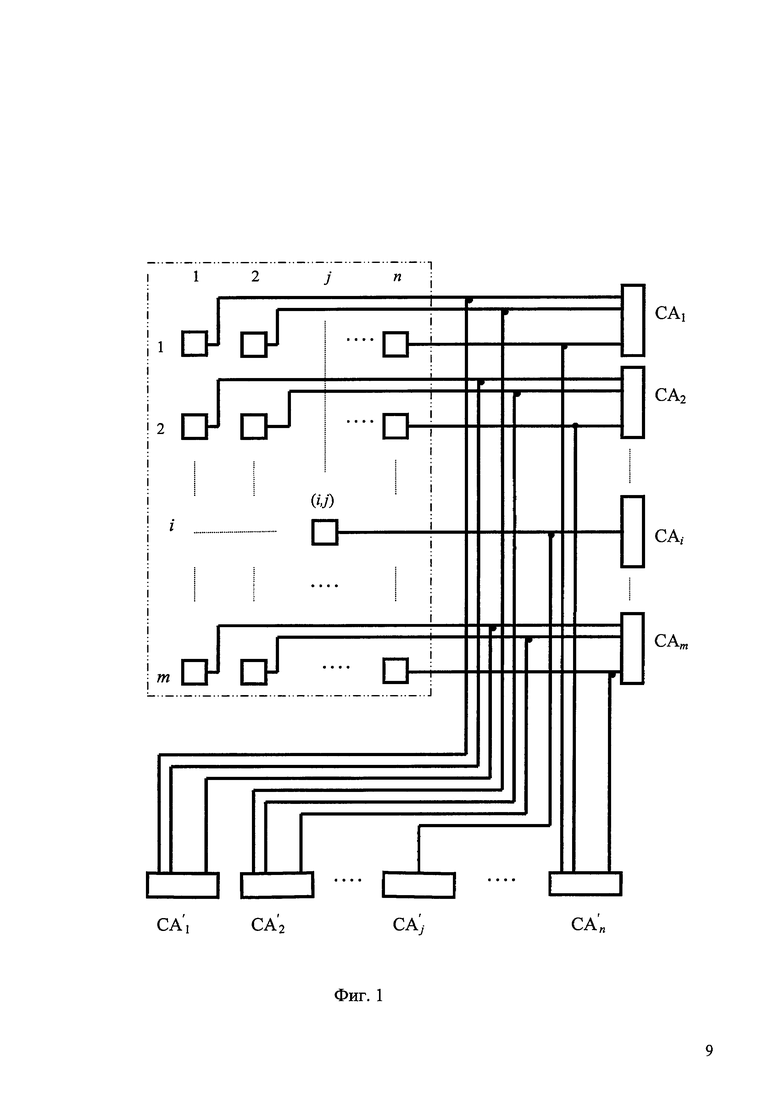

Технический результат в устройстве-прототипе (а именно - возможность локализации одиночных неисправностей) достигается тем, что оно содержит m n-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены построчно со всеми mn выходами проверяемого объекта, и n m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены по столбцам со всеми nm выходами проверяемого объекта.

На фиг. 1 представлена схема устройства-прототипа вместе с выходной частью проверяемой ПЛМ, очерченной штрих-пунктирной линией; наблюдаемые КЛБ ПЛМ изображены квадратами и расположены в форме условной матрицы по строкам и столбцам.

Устройство-прототип содержит m n-разрядных многовходовых СА строк (CA1, СА2, …, CAm) и n m-разрядных многовходовых СА столбцов  , которые соединены с выходами ПЛМ, расположенными соответственно в строках и столбцах матрицы выходов. Каждый выход ПЛМ (выход каждого КЛБ ПЛМ) принадлежит одновременно некоторой строке i (i=1, …, m) и некоторому столбцу j (j=1, …, n) матрицы выходов и, следовательно, соединен с одним из входов (произвольным) CAi, соответствующего строке, и одновременно с одним из входов (произвольным)

, которые соединены с выходами ПЛМ, расположенными соответственно в строках и столбцах матрицы выходов. Каждый выход ПЛМ (выход каждого КЛБ ПЛМ) принадлежит одновременно некоторой строке i (i=1, …, m) и некоторому столбцу j (j=1, …, n) матрицы выходов и, следовательно, соединен с одним из входов (произвольным) CAi, соответствующего строке, и одновременно с одним из входов (произвольным)  , соответствующего столбцу j. Число разрядов всех СА, составляющих устройство-прототип, равно З3=2nm=2N, т.е. в два раза превышает затраты устройства-аналога, использующего многовходовые СА, но в

, соответствующего столбцу j. Число разрядов всех СА, составляющих устройство-прототип, равно З3=2nm=2N, т.е. в два раза превышает затраты устройства-аналога, использующего многовходовые СА, но в  меньше затрат устройства-аналога, использующего одновходовые СА. По существу, в устройстве-прототипе каждый выход ПЛМ при его тестировании подает свою реакцию одновременно на два СА (СА строки и СА столбца), в которых она и анализируется. Каждый СА однозначно задает подмножество выходов объекта (номеров выходов ПЛМ) по строкам или по столбцам, к которым соединены его входы.

меньше затрат устройства-аналога, использующего одновходовые СА. По существу, в устройстве-прототипе каждый выход ПЛМ при его тестировании подает свою реакцию одновременно на два СА (СА строки и СА столбца), в которых она и анализируется. Каждый СА однозначно задает подмножество выходов объекта (номеров выходов ПЛМ) по строкам или по столбцам, к которым соединены его входы.

Все дальнейшие рассуждения будем проводить для условной матрицы номеров выходов объекта диагностирования, например, ПЛМ. Выходы ПЛМ, точнее - их номера будем называть элементами матрицы; элемент матрицы, соответствующий неисправному выходу ПЛМ, - неисправным элементом; строку (столбец) матрицы, в которой находится неисправный элемент, - неисправной строкой (столбцом). А поскольку строкам и столбцам матрицы сопоставлены результирующие сигнатуры соответствующих СА устройства, то неисправная (исправная) строка или столбец - это неисправная (исправная) сигнатура соответствующего СА.

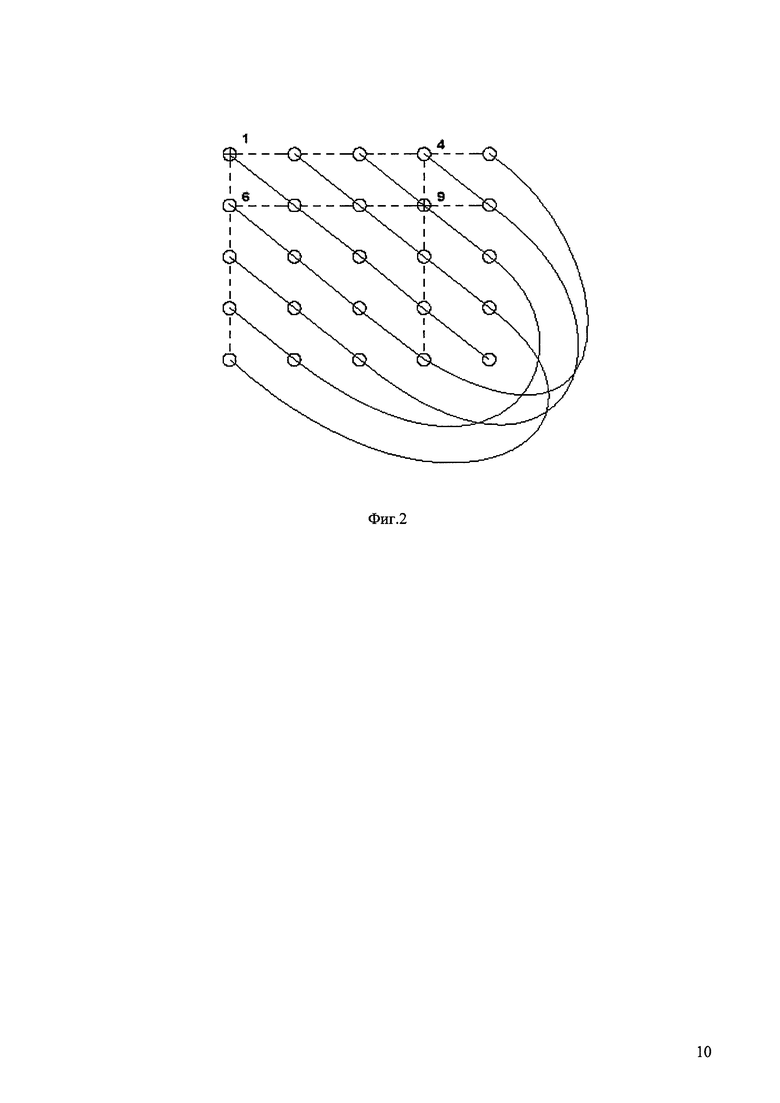

Неисправный элемент (его порядковый номер) определяется (локализуется) пересечением номеров элементов строки и столбца, зафиксированных своими СА как неисправные. Таким образом доказано, что метод локализации, реализованный в устройстве-прототипе, обеспечивает локализацию любой одиночной неисправности в матрице. Однако это не так даже для общего случая двукратных неисправностей. Так, если два неисправных элемента находятся в разных строках и в разных столбцах, например, элементы 1 и 9 в матрице на фиг. 2, то неисправными будут сигнатуры двух строк (1 и 2) и двух столбцов (1 и 4), и неисправными будут признаны уже не два, а четыре элемента их пересечения. Значит, в неисправные будут ошибочно зачислены еще два элемента 4 и 6, которые будем называть подозреваемыми. Только для некоторых кратных неисправностей, а именно таких, что неисправные элементы находятся все в одной строке или все в одном столбце, устройство-прототип будет давать правильные результаты локализации неисправностей.

Задачей настоящего изобретения является поиск неисправностей. Техническим результатом - повышение кратности неисправностей при их локализации по сравнению с уровнем, достигаемым в устройстве-прототипе.

Технический результат в предлагаемом устройстве достигается тем, что устройство анализа результатов тестирования для локализации двукратных неисправностей содержит m m-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены построчно со всеми mm выходами проверяемого объекта, и m m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены по столбцам со всеми mm выходами проверяемого объекта. Устройство дополнительно содержит m m-разрядных сигнатурных анализаторов (СА диагоналей), входы которых соединены подиагонально со всеми mm выходами проверяемого объекта.

На фиг. 1 представлена схема устройства-прототипа.

На фиг. 2 иллюстрируется невозможность локализовать двукратные неисправности устройством-прототипом и возможность их локализации предлагаемым устройством с использованием показанных диагоналей.

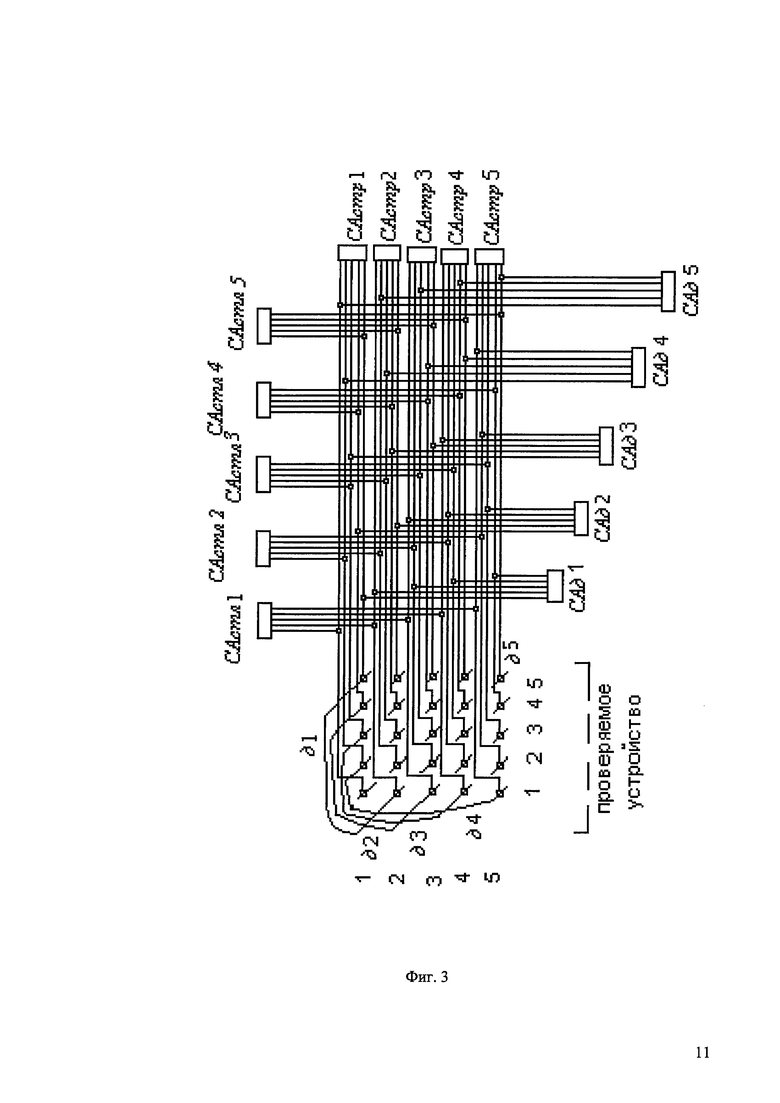

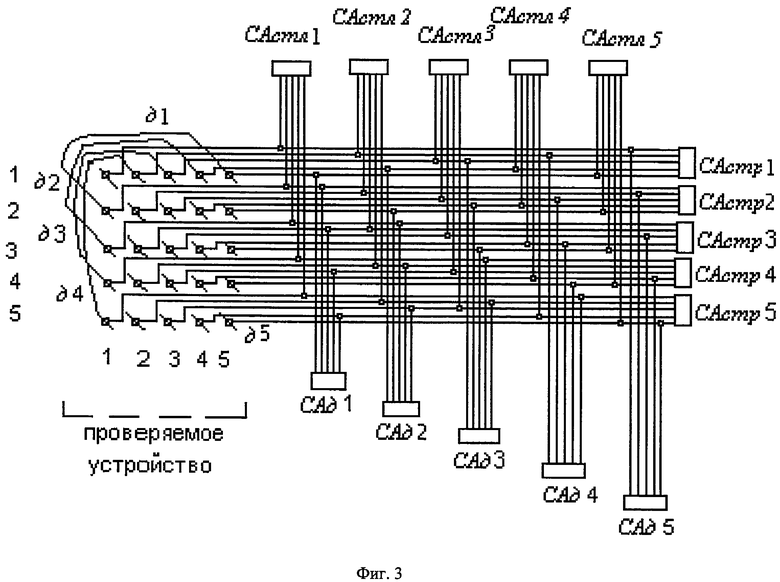

На фиг. 3 представлена схема предложенного устройства для случая объекта диагностирования с 25 (5×5) выходами (контрольными точками).

Далее будут рассматриваться объекты диагностирования, матрица выходов которых квадратная, т.е. m=n, a m - нечетное число. Через каждый элемент матрицы можно провести диагонали. Диагональ, соединяющая первый элемент матрицы с последним, называется главной. Ее и диагонали, ей параллельные, назовем прямыми диагоналями или, покороче, диагоналями. В квадратной матрице главная диагональ содержит m элементов, также как строки и столбцы. Все остальные диагонали, параллельные главной, имеют число элементов, меньшее m, вплоть до одного элемента. Проведем объединение диагоналей так, чтобы каждое объединение содержало m элементов. Так, соседнюю сверху от главной диагональ, имеющую m-1 элементов, объединим с последней в нижней половине матрицы диагональю, содержащей один элемент (см. фиг. 2). Вторую сверху от главной диагональ объединим с предпоследней внизу и т.д. В результате получим m объединенных прямых диагоналей. На фиг. 2 объединенные диагонали изображены кривыми или прямой линиями. В дальнейшем будем рассматривать объединенные диагонали, при этом опуская слово «объединенная».

Рассмотрим произвольную матрицу, у которой m - нечетное число. Подробный анализ выявляет следующие свойства такой матрицы.

1. Через любой элемент может проходить только одна строка, один столбец и одна диагональ, которые условно назовем параметрами элемента.

2. Два различных элемента могут иметь только один общий параметр или не иметь ни одного. Например, если два элемента находятся в одной строке (т.е. имеют уже общий параметр), то из просмотра матрицы видно, что столбцы и диагонали у них будут различаться. То же самое наблюдаем, когда два элемента находятся в одной диагонали. Тогда столбцы и строки у них будут разные. Заметим, что свойством 2 не обладают матрицы с четным m.

На фиг. 3 все выходы проверяемого устройства расположены в виде пространственной матрицы квадратиков с 5-ю строками и 5-ю столбцами. Выходы построчно соединены со входами 5-ти сигнатурных анализаторов строк САстр1, …, САстр5, по столбцам - со входами 5-ти сигнатурных анализаторов столбцов САстл1, …, CAстл5 и по диагонально - со входами 5-ти сигнатурных анализаторов диагоналей САд1, …, САд5 (все 5 диагоналей д1, …, д5 показаны на фиг. 3 кривыми и прямой линиями). При тестировании проверяемого устройства тестовая реакция со всех его выходов одновременно поступает на три вида сигнатурных анализаторов, на которых в общем случае фиксируются исправные и неисправные сигнатуры.

Назовем такой способ контроля матрицы, реализуемый в предлагаемом устройстве, матрично-диагональным. Можно утверждать, что матрично-диагональный способ контроля по трем параметрам локализует любую двукратную неисправность (два одновременно отказавших выхода). При тестировании неисправные выходы имеют все три своих параметра (строку, столбец и диагональ) неисправными, а у исправных выходов хотя бы один параметр будет исправен.

Действительно, при тестировании у неисправного выхода будут зафиксированы как неисправные все три его параметра (строка, столбец и диагональ). Покажем, что у всех остальных (т.е. исправных) выходов хотя бы один параметр будет исправен. Исправный выход может иметь с неисправным только один общий параметр по свойству 2. Так как неисправность двукратная, то общих параметров с неисправными выходами будет максимум два. Эти параметры будут зафиксированы при тестировании как неисправные. Поскольку в предлагаемом устройстве контроль ведется по трем параметрам, то третий параметр наверняка будет исправным. Утверждение доказано. Так, в рассмотренном выше примере двукратной неисправности при контроле по трем параметрам диагонали, проходящие через неисправные элементы, будут, естественно, зафиксированы как неисправные, а диагонали через подозреваемые элементы - как исправные. Тем самым подозрение с элементов 4 и 6 (см. фиг. 2) будет снято.

Очевидно, что предлагаемое устройство осуществляет локализацию и одиночных неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО АНАЛИЗА РЕЗУЛЬТАТОВ ТЕСТИРОВАНИЯ ДЛЯ ПОИСКА НЕИСПРАВНЫХ БЛОКОВ | 2013 |

|

RU2540805C2 |

| Программируемая логическая матрица | 1988 |

|

SU1621020A1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Сигнатурный анализатор | 1987 |

|

SU1524054A1 |

| СПОСОБ ТЕСТОПРИГОДНОСТИ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2011 |

|

RU2497182C2 |

| Микропрограммное устройство управления | 1989 |

|

SU1667069A1 |

| Многовходовой сигнатурный анализатор | 1986 |

|

SU1363213A1 |

| Микропрограммное устройство управления с контролем переходов | 1987 |

|

SU1411743A1 |

Изобретение относится к области тестирования дискретных объектов большой размерности. Технический результат заключается в повышении кратности неисправностей при их локализации. Устройство анализа результатов тестирования для локализации двукратных неисправностей содержит m m-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены построчно со всеми mm выходами проверяемого объекта, и m m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены по столбцам со всеми mm выходами проверяемого объекта. При этом устройство дополнительно содержит m m-разрядных сигнатурных анализаторов (СА диагоналей), входы которых соединены подиагонально со всеми mm выходами проверяемого объекта. 3 ил.

Устройство анализа результатов тестирования для локализации двукратных неисправностей, содержащее m m-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены построчно со всеми mm выходами проверяемого объекта, и m m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены по столбцам со всеми mm выходами проверяемого объекта, отличающееся тем, что дополнительно содержит m m-разрядных сигнатурных анализаторов (СА диагоналей), входы которых соединены подиагонально со всеми mm выходами проверяемого объекта.

| УСТРОЙСТВО АНАЛИЗА РЕЗУЛЬТАТОВ ТЕСТИРОВАНИЯ ДЛЯ ПОИСКА НЕИСПРАВНЫХ БЛОКОВ | 2013 |

|

RU2540805C2 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Способ получения камфоры | 1921 |

|

SU119A1 |

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| ИНТЕГРАЛЬНАЯ СХЕМА С ПРОГРАММИРУЕМЫМ ЛОГИЧЕСКИМ АНАЛИЗАТОРОМ С РАСШИРЕННЫМИ ВОЗМОЖНОСТЯМИ АНАЛИЗА И ОТЛАДКИ И СПОСОБ | 2011 |

|

RU2579814C2 |

| US 6574761 B1 03.06.2003 | |||

| US 20130173632 A1 04.07.2013 | |||

| US 7437271 B2 14.10.2008. | |||

Авторы

Даты

2017-10-19—Публикация

2016-06-21—Подача