При тестировании принято на входы объекта или на входы его частей (блоков) подавать тестовые воздействия (тесты), а с выходов объекта или его блоков снимать тестовую реакцию, которая анализируется (сопоставляется с эталонной реакцией исправного объекта) для решения одной или двух задач: 1) проверка исправности объекта; 2) поиск (или локализация) неисправностей (отказавших блоков), если проверяемый объект оказался неисправным. Решение второй задачи особенно актуально, если подразумевается восстановление неисправного объекта путем, например, ручной замены отказавшего блока или автоматической реконфигурации объекта, при которой неисправные блоки отключаются от объекта, а вместо них подключаются соответствующие резервные блоки. Такая возможность принципиально имеется, если объект реализован на программируемой логической матрице.

В технической диагностике в качестве устройства анализа результатов тестирования чаще всего применяют так называемые сигнатурные анализаторы (СА) (Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 137-142). Сущность СА состоит в представлении длинной выходной последовательности на выходе объекта в виде короткого ключевого слова (сигнатуры). На основании сопоставления сигнатуры, полученной в результате тестирования, с ее эталонным значением, полученным заранее на заведомо исправном объекте или его модели, делается вывод о техническом состоянии тестируемого объекта. СА реализуется в виде регистра сдвига с обратными связями. Различают СА одноканальные (одновходовые), которые «сжимают» одну выходную тестовую последовательность во времени, и многоканальные (многовходовые), «сжимающие» несколько последовательностей с разных выходов объекта и во времени, и в пространстве.

Эффективность обнаружения ошибки в последовательности сжимаемых данных называется достоверностью СА (Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 145-146). Достоверность оценивается как вероятность необнаружения ошибок в анализируемой последовательности: р≈1/2l, где l - число разрядов (или длина) СА. Причем эта вероятность инвариантна относительно сжимаемой последовательности и конструкции СА (числа и вида его обратных связей) и уже при l=16 значение р=1/216=0,0000152 достаточно близко к нулю.

Как правило, проверяемый объект многовыходной, и при условии, что его проверяющий тест построен или сгенерирован и может подаваться на входы объекта, задача сжатия выходной тестовой реакции может решаться двояко. В первом варианте (а это будет аналог заявляемого устройства) к каждому из N выходов объекта присоединяется одновходовой сигнатурный анализатор длины l. При этом затраты, исчисленные в количестве разрядов всех анализаторов (без учета затрат на хранение N эталонных сигнатур и их сопоставление с результирующими сигнатурами), составляют З1=lN. В этом варианте компактного тестирования решается как задача проверки исправности объекта, так и задача локализации неисправностей. Сигнатуру будем называть неисправной, если она отлична от эталонной. Если при тестировании k из N сигнатур оказались неисправными, то неисправности в объекте находятся в аппаратуре, работающей на эти k выходов, причем в общем случае эта аппаратура может пересекаться. В частном случае, если весь объект представляет собой N аппаратурно не пересекающихся частей (возможно, имеющих общие входы объекта), то k неисправных сигнатур свидетельствуют о неисправности соответствующих k частей. При этом для класса одиночных неисправностей в проверяемом объекте строго одна неисправная сигнатура в САi свидетельствует о неисправности строго одной части объекта с выходом i. Рассмотренное устройство реализации компактного тестирования и описанное в работе (Ярмолик В.Н. Контроль и диагностика цифровых узлов ЭВМ, Минск, «Наука и техника», 1988, стр. 208), является аналогом заявляемого устройства и характеризуется, как описано выше, определенным, зависящим от структуры проверяемого объекта, достигаемым уровнем (глубиной) локализации неисправностей и фиксированным уровнем затрат З1 на реализацию устройства анализа результатов тестирования.

Наиболее близким к заявляемому устройству, реализующим второй вариант сжатия тестовой реакции, является устройство, Описанное в работе (Аксенова Г.П. Контролепригодная архитектура для самотестирования в программируемых логических матричных структурах, «Автоматика и телемеханика», 2010, №12, стр. 154-165).

В этой работе в качестве анализатора тестовой реакции выступает совокупность многовходовых сигнатурных анализаторов, множество входов которых без пересечений охватывает все N выходов проверяемого объекта (т.е. каждый вход СА соединен с одним выходом объекта). А проверяемым объектом является контролепригодная программируемая логическая матрица (ПЛМ), аппаратурно не пересекающиеся части - это одновыходные элементы ПЛМ (ее конфигурируемые логические блоки), выходы которых соединены со входами l-разрядных многовходовых СА. Затраты З2 на реализацию устройства-прототипа минимальны, когда суммарное число разрядов всех СА равно N, а N кратно l. Итак, З2мин=N. И если задача проверки исправности (с достоверностью многовходового СА) в прототипе решается полностью, то задача локализации неисправностей не решается даже для класса одиночных неисправностей. Действительно, при неисправности строго одного элемента ПЛМ единственная неисправная сигнатура свидетельствует только о том, что неисправности находятся в части объекта, а точнее, среди группы элементов ПЛМ, выходы которых соединены со входами СА, выдавшего эту неисправную сигнатуру. Т.е. экономный в реализации многовходовой СА, сжимая тестовую реакцию и во времени, и в пространстве, «замазывает» след от неисправного элемента.

Задачей настоящего изобретения является поиск неисправностей.

Техническим результатом изобретения является повышение глубины локализации неисправностей.

Будем считать, что проверяемый объект для устройства-прототипа и заявляемого устройства один и тот же, т.е. это - контролепригодная ПЛМ. Для пояснения принципа достижения заявленного технического результата условно расположим все N одновыходных блоков проверяемого объекта (т.е. элементы ПЛМ) в виде (m х n)-матрицы, где m - число ее строк, a n - число столбцов. (Не путать условную матрицу с реальным конструктивным размещением элементов в кристалле). Если N<mn, то последняя строка будет не полностью заполнена. Не умаляя общности, будем считать, что N=mn.

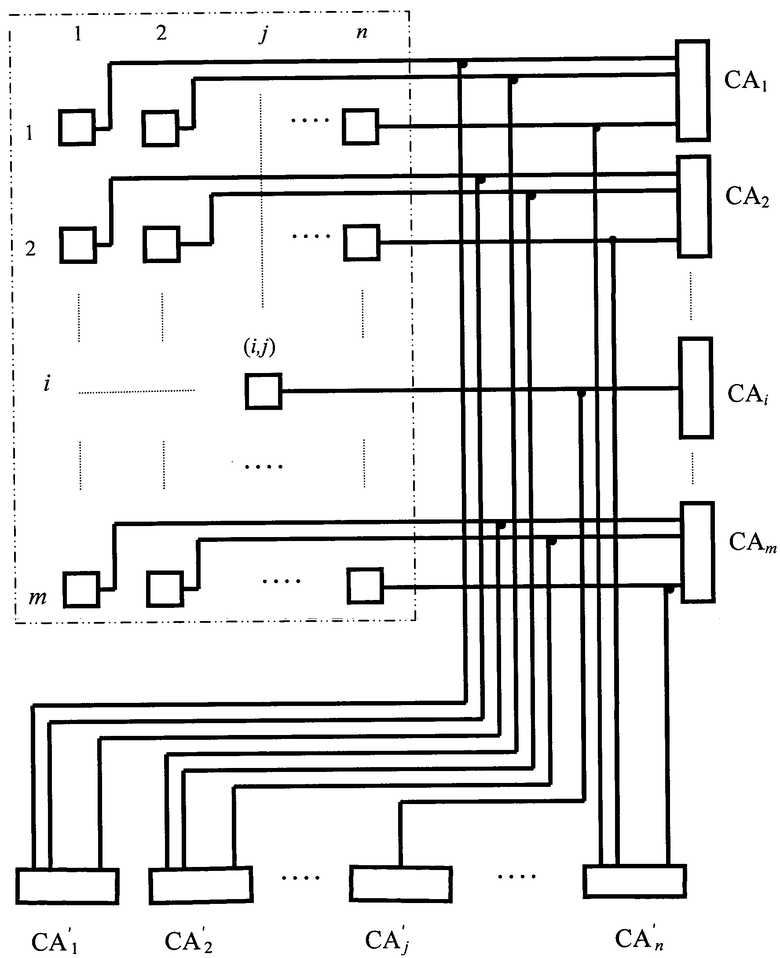

Технический результат достигается тем, что устройство анализа результатов тестирования для поиска неисправных блоков содержит m n-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены со всеми mn выходами одновыходных блоков проверяемого объекта, и дополнительно содержит n m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены со входами СА строк так, что j-е входы (j=1,…, n) всех m СА строк соединены со всеми m входами j-го СА столбцов.

На чертеже представлена схема предложенного устройства вместе с выходной частью проверяемой ПЛМ, очерченной штрихпунктирной линией; одновыходные элементы ПЛМ изображены квадратами и расположены в форме условной матрицы по строкам и столбцам.

Заявляемое устройство содержит m n-разрядных многовходовых СА строк (CA1, СА2,…, САm) и n m-разрядных многовходовых СА столбцов

Теперь оценим достигаемую в заявляемом устройстве глубину локализации неисправностей (неисправных элементов ПЛМ) по результатам тестирования объекта, зафиксированным в виде исправных и неисправных сигнатур во всех m+n СА (строк и столбцов). Все дальнейшие рассуждения будем проводить для условной матрицы. Элементы ПЛМ будем называть элементами матрицы; элемент матрицы, соответствующий неисправному элементу ПЛМ, - неисправным элементом; строку (столбец) матрицы, в которой находится неисправный элемент, - неисправной строкой (столбцом). А поскольку строкам и столбцам матрицы сопоставлены результирующие сигнатуры соответствующих СА устройства, то неисправная строка (столбец) - это неисправная сигнатура соответствующего СА.

Рассмотрим класс одиночных неисправностей матрицы, где неисправным может быть только один ее элемент, хотя в самом элементе допускается кратная неисправность. Покажем, что заявляемое устройство обеспечивает локализацию любого неисправного элемента матрицы в классе одиночных неисправностей в отличие от устройства-прототипа. Пусть в матрице неисправен один элемент (if), принадлежащий одновременно некоторой строке i и некоторому столбцу j матрицы, см. чертеж. В этом случае после проведения тестирования неисправность зафиксируется в виде неисправной сигнатуры в САi и в

Теперь рассмотрим кратные неисправности в матрице. Пусть, например, матрица, состоящая из порядковых номеров своих элементов

содержит три неисправных элемента с номерами 3, 6, 11 (они выделены жирным шрифтом). При проведении тестирования неисправность зафиксируют СА строк 1, 2, 3 и столбцов 2, 3. Следовательно, под подозрение попадают элементы, стоящие на пересечении этих неисправных строк и столбцов, а именно 2, 3, 6, 7, 10, 11. Неисправные элементы все попали в подозреваемое множество, однако туда попали и исправные элементы 2, 7 и 10.

Покажем, что заявляемое устройство в отличие от устройства-прототипа обеспечивает точную локализацию неисправных элементов матрицы при кратной неисправности следующего вида: неисправные элементы находятся все в одной строке или все в одном столбце. Пусть в матрице в i-й строке находятся k неисправных элементов. В этом случае после проведения тестирования будут зафиксированы, как неисправные, i-я строка и k столбцов. Так как неисправная строка одна, то неисправные элементы однозначно будут находиться на пересечениях этой строки и неисправных столбцов. Таким образом, будут указаны как неисправные все k элементов i-й строки и только они. Аналогичные рассуждения можно провести, если неисправные элементы находятся все в j-м столбце.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство анализа результатов тестирования для локализации двукратных неисправностей | 2016 |

|

RU2633908C1 |

| СПОСОБ ТЕСТОПРИГОДНОЙ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2008 |

|

RU2413282C2 |

| СПОСОБ ТЕСТОПРИГОДНОСТИ РЕАЛИЗАЦИИ ЛОГИЧЕСКИХ ПРЕОБРАЗОВАТЕЛЕЙ | 2011 |

|

RU2497182C2 |

| Программируемая логическая матрица | 1988 |

|

SU1621020A1 |

| Многовходовый сигнатурный анализатор | 1986 |

|

SU1383362A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1718220A1 |

| Сигнатурный анализатор | 1987 |

|

SU1524054A1 |

| Микропрограммное устройство управления с контролем переходов | 1987 |

|

SU1411743A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Сигнатурный анализатор (его варианты) | 1984 |

|

SU1252784A1 |

Изобретение относится к области тестирования дискретных объектов большой размерности. Техническим результатом является повышение глубины локализации неисправностей. Устройство содержит m n-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены со всеми mn выходами одновыходных блоков проверяемого объекта, n m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены со входами СА строк так, что j-e входы (j=1,…, n) всех m СА строк соединены со всеми m входами j-го СА столбцов. 1 ил.

Устройство анализа результатов тестирования для поиска неисправных блоков, содержащее m n-разрядных многовходовых сигнатурных анализаторов (СА строк), входы которых соединены со всеми mn выходами одновыходных блоков проверяемого объекта, отличающееся тем, что дополнительно содержит n m-разрядных многовходовых сигнатурных анализаторов (СА столбцов), входы которых соединены со входами СА строк так, что j-е входы (j=1,…,n) всех m СА строк соединены со всеми m входами j-го СА столбцов.

| АКСЕНОВА Г.П | |||

| "КОНТРОЛЕПРИГОДНАЯ АРХИТЕКТУРА ДЛЯ САМОТЕСТИРОВАНИЯ В ПРОГРАММИРУЕМЫХ ЛОГИЧЕСКИХ МАТРИЧНЫХ СТРУКТУРАХ" | |||

| В: "АВТОМАТИКА И ТЕЛЕМЕХАНИКА", 2010, N12, с.154-165 | |||

| Устройство для диагностирования цифровых объектов | 1989 |

|

SU1705829A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1603386A1 |

| Устройство для контроля программируемых логических матриц | 1983 |

|

SU1236486A1 |

| US 6574761 B1, 03.06.2003 | |||

| US 6202182 B1, 13.03.2001 | |||

Авторы

Даты

2015-02-10—Публикация

2013-06-04—Подача