Изобретение относится к вычислительной технике и электронике и можег быть использовано при создании больших интегральных схем (БИС) в качестве выходного усилителя на внешнюю емкостную нагрузку.

Целью изобретения является повышение быстродействия и надежности элемента.

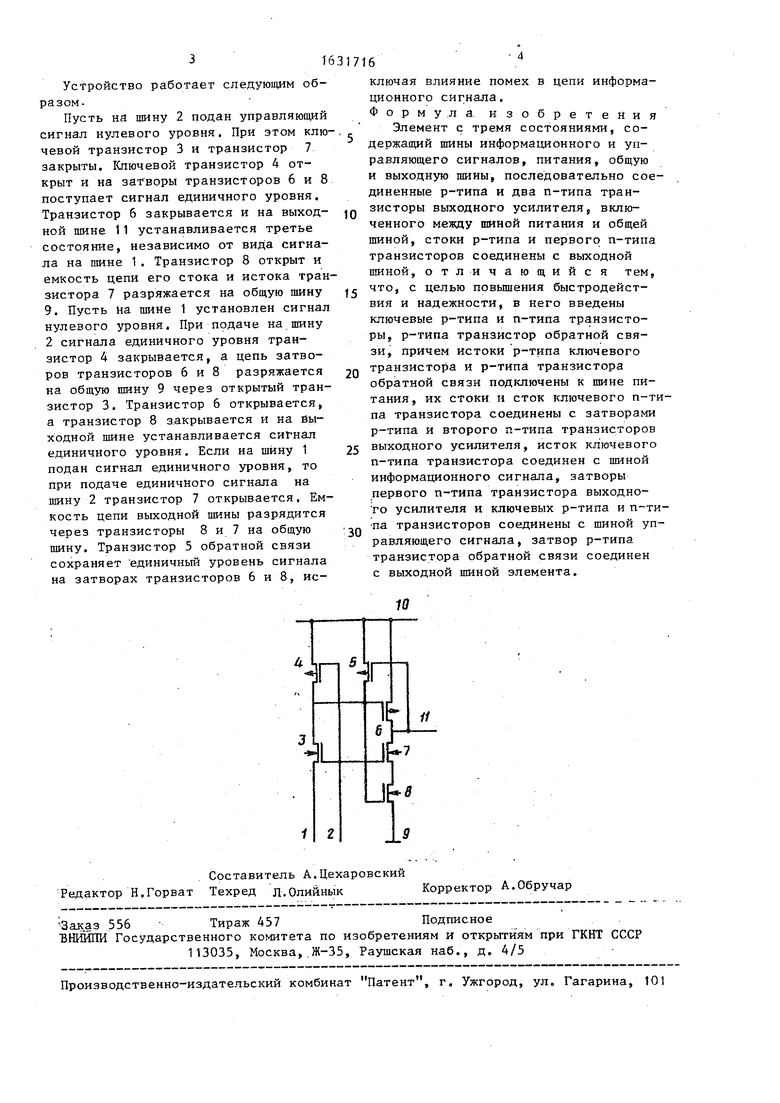

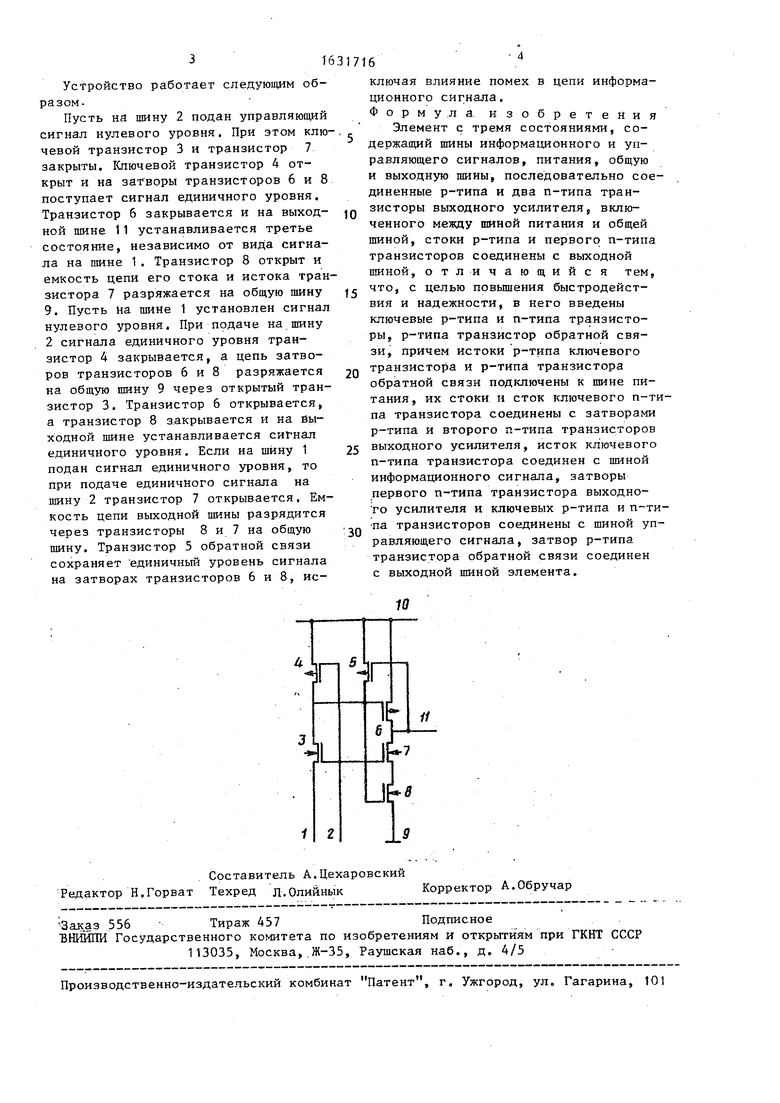

На чертеже показан элемент с тремя состояниями.

На чертеже изображены шина 1 информационного сигнала, шина 2 управляющего сигнала, n-гипа ключевой транзистор 3, р-типа ключевой транзистор 4, р-гипа транзистор 5 обратной связи, р-типа транзистор 6 выходного усилителя, первый п-типа транзистор 7 выходного усилителя,второй n-типа транзистор 8 выходного усилителя, общая 9 шина, шина 10 питания, выходная шина 11 элемента. Информационная шина 1 соединена с истоком ключевого n-типа транзистора 3, стоки ключевых n-типа и р-типа транзисторов 3 и 4 и р-типа транзистора 5 соединены с затворами р-типа и n-типа транзисторов 6 и 8 выходного усилителя, истоки р-типа транзисторов 4, 5 и 6 соединены с шиной питания, затворы ключевых n-типа и р-типа транзисторов 3 и 4 и п-типа транзистора 7 выходного усилителя соединены с шиной 2 управляющего сигнала, затвор р-типа транзистора 5 и стоки р-типа и первого п-типа транзисторов 6 и 7 выходного усилителя соединены с выходной шиной 11 элемента, сток второго n-типа транзистора 8 соединен с истоком первого n-типа транзистора 7, а его исток соединен с общей шиной 9.

О5

м-

05

Устройство работает следующим образомПусть на шину 2 подан управляющий сигнал нулевого уровня. При этом ключевой транзистор 3 и транзистор 7 закрыты. Ключевой транзистор 4 открыт и на затворы транзисторов 6 и 8 поступает сигнал единичного уровня. Транзистор б закрывается и на выходной шине 11 устанавливается третье состояние, независимо от вида сигнала на шине 1. Транзистор 8 открыт и емкость цепи его стока и истока транзистора 7 разряжается на общую шину 9. Пусть ha шине 1 установлен сигнал нулевого уровня. При подаче на шину 2 сигнала единичного уровня транзистор 4 закрывается, а цепь затворов транзисторов 6 и 8 разряжается на общую шину 9 через открытый транзистор 3. Транзистор 6 открывается, а транзистор 8 закрывается и на выходной шине устанавливается сигнал единичного уровня. Если на шину 1 подан сигнал единичного уровня, то при подаче единичного сигнала на шину 2 транзистор 7 открывается. Емкость цепи выходной шины разрядится через транзисторы 8 и 7 на общую шину. Транзистор 5 обратной связи сохраняет единичный уровень сигнала на затворах транзисторов 6 и 8, ис

0

5

0

ключая влияние помех в цепи информационного сигнала.

Формула изобретения

Элемент с тремя состояниями, содержащий шины информационного и управляющего сигналов, питания, общую и выходную шины, последовательно соединенные р-типа и два n-типа транзисторы выходного усилителя, включенного между шиной питания и общей шиной, стоки р-типа и первого п-тииа транзисторов соединены с выходной шиной, отличающийся тем, что, с целью повышения быстродействия и надежности, в него введены ключевые р-типа и n-типа транзисторы, р-типа транзистор обратной связи, причем истоки р-типа ключевого транзистора и р-типа транзистора обратной связи подключены к шине питания, их стоки и сток ключевого п-ти- па транзистора соединены с затворами р-типа и второго n-типа транзисторов выходного усилителя, исток ключевого n-типа транзистора соединен с шиной информационного сигнала, затворы первого n-типа транзистора выходного усилителя и ключевых р-типа и п-ти- па транзисторов соединены с шиной управляющего сигнала, затвор р-типа транзистора обратной связи соединен с выходной шиной элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер со счетным входом на взаимодополняющих МДП-транзисторах | 1989 |

|

SU1622925A1 |

| Элемент с тремя состояниями | 1988 |

|

SU1599985A1 |

| Коммутатор напряжений | 1988 |

|

SU1524168A1 |

| Логический элемент с тремя состояниями на комплементарных МДП-транзисторах | 1988 |

|

SU1562967A1 |

| Ключевой элемент | 1986 |

|

SU1406768A1 |

| Усилитель считывания для запоминающего устройства на МДП-транзисторах | 1981 |

|

SU989583A1 |

| Компаратор напряжения | 1985 |

|

SU1246049A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Изобретение относится к вычислительной технике и электронике и можег быть использовано при создании больших интегральных схем (БИС) в качестве выходного усилителя на внешнюю емкостную нагрузку. Целью изобретения является повышение быстродействия и надежности элемента. Устройство содержит шину 1 информационного сигнала, шину 2 управляющего сигнала, общую шину 9,шину 1 0 питания, выходную шину 11 . Введение МДП-транзисторов 3-5,а также новых связей приводит к тому, что открывание МДП-транзистора 7 обусловлено максимальной разностью между напряжением единичного уровня на его затворе и напряжением на его истоке за счет ранее открытого МДП-транзистора 8. В результате разряд выходной шины 11 произойдет быстрее. 1 ил.

| Элемент с тремя состояниями | 1987 |

|

SU1413721A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-28—Публикация

1989-04-14—Подача