Изобретение относится к электронике, автоматике и вычислительной технике и может найти применение в цифровых интегральных схемах на МДП транзисторах.

Цель изобретения - повьшение быстродействия устройства.

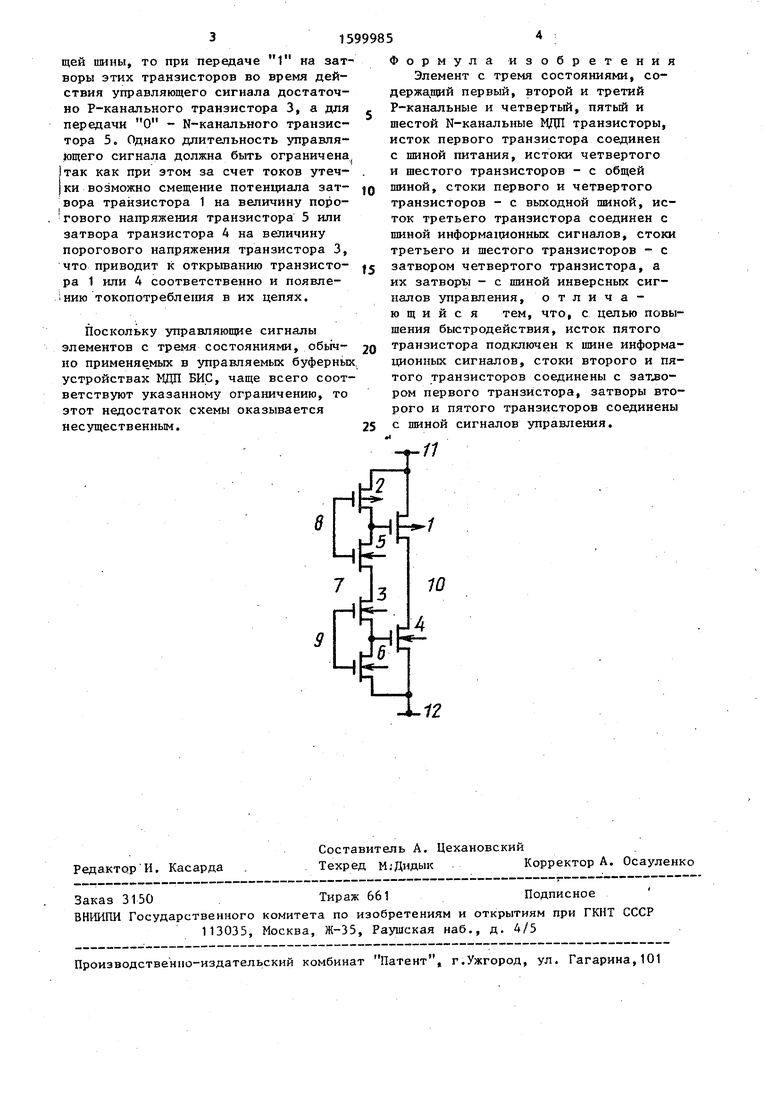

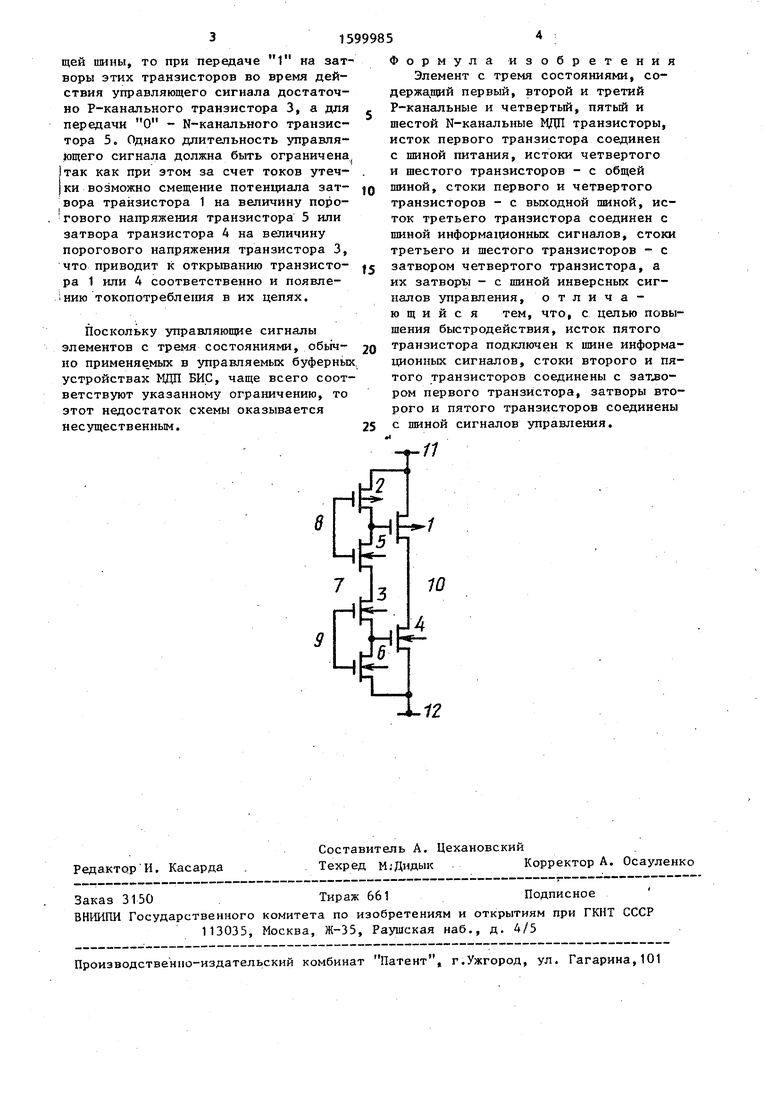

На чертеже представлена электрическая принципиальная схема элемента с тремя состояниями на МДП транзисторах.

Элемент содержит Р-канальные МДП транзисторы 1-3, N-канальные МДП транзисторы 4-6, шину 7 информационных сигналов, шины 8 и 9 сигналов управления и инверсных сигналов управления соответственно, выходную шину 10, шину 11 питания и общую шину 12.

Истоки транзисторов 1 и 2 подключены к шине 11 питания, истоки транзисторов 4 и 6 - к общей шине 12. Стоки транзисторов 1 и 4 соединены с выходной 1яиной 10, стоки транзисторов 2 и 5 - с затвором транзистора 1, а их затворы - с шиной 8 сигналов управления, стоки транзисторов 3 и 6 - с затвором транзистора 4, а их затворы - с шиной 9 инверсных сигналов управления. Истоки транзисторов 3 и 5 соединены с шиной 7 информационных сигналов.

Элемент работает следующим об- разомо

В исходном положении на шине 8 i

(Л

О, на шине 9

Ч. При этом открыты транзисторы 2 и 6, что обеспечивает на затворе транзистора 4 - О, а на затворе транзистора 1 - 1. Транзисторы 1, 3, 4 и 5 закрыты, в результате чего элемент находится в третьем состоянии, независимо от уровня напряжения на шине 7.

При поступлении 1 на шину 8 и О на шину 9 транзисторы 2 и 6 закрываются, а транзисторы 3 и 5 открываются, что обеспечивает передачу информахц онного сигнала с шины 7 на затворы транзисторов 1 и 4 и, соответственно, инверсное значение этого сигнала на выходной шине 10.

Так как в исходном положении на затворе транзистора 1 установлен уровень напряжения питания, а на затворе транзистора 4 - уровень обсд

со со со

00

ел

щей шины, то при передаче 1 на зат воры этих транзисторов во время действия управляющего сигнала достаточно Р-канального транзистора 3, а для передачи О - N-канапьного транзистора 5. Однако длительность управляющего сигнала должна быть ограничена так как при этом за счет токов утечки возможно смещение потенциала затвора транзистора 1 на величину поро- гового напряжения транзистора 5 или затвора транзистора 4 на величину порогового напряжения транзистора 3, что приводит к открьгоанию транзистора 1 или 4 соответственно и появле- нию токопотребле1шя в их цепях.

Поскольку управляющие сигналы элементов с тремя состояниями, обьгч- 20 но применяемых в управляемых буферных, устройствах МДП БИС, чаще всего соответствуют указанному ограничению, то этот недостаток схемы оказывается несущественным.25

Формула изобретения

Элемент с тремя состояниями, со- держа щий первый, второй и третий Р-канальные и четвертый, пятый и шестой N-канальные МДП транзисторы, исток первого транзистора соединен с шиной питания, истоки четвертого и шестого транзисторов - с общей шиной, стоки первого и четвертого транзисторов - с выходной шиной, исток третьего транзистора соединен с шиной информах ионньпс сигналов, стоки третьего и шестого транзисторов - с затвором четвертого транзистора, а их затворЪ - с шиной инверсньк сигналов управления, отличающийся тем, что, с целью повышения быстродействия, исток пятого транзистора подключен к шине информационных сигналов, стоки второго и пятого транзисторов соединены с 3aTjBO- ром первого транзистора, затворы второго и пятого транзисторов соединены с шиной сигналов управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый махоритарный элемент на комплементарных МДП-транзисторах | 1982 |

|

SU1034191A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

| Формирователь импульсов | 1982 |

|

SU1238230A1 |

| Элемент с тремя состояниями | 1978 |

|

SU743200A1 |

| Аналоговый переключатель | 1986 |

|

SU1385288A1 |

| Элемент с тремя состояниями | 1989 |

|

SU1631716A1 |

| Запоминающее устройство | 1986 |

|

SU1372357A1 |

| Динамический Д-триггер с третьим состоянием по выходу | 1990 |

|

SU1774472A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Управляемый мажоритарный элемент | 1981 |

|

SU993479A1 |

Изобретение относится к электронике, автоматике и вычислительной технике и может найти применение в цифровых интегральных схемах на МДП-транзисторах. Цель изобретения - повышение быстродействия. Элемент содержит P-канальные МДП-транзисторы 1,2,3 и N-канальные МДП-транзисторы 4,5,6. Поставленная цель достигаеся за счет введения новых электрических связей между функциональными элементами. 1 ил.

O-tf

| Способ сужения чугунных изделий | 1922 |

|

SU38A1 |

| Бкхл | |||

| Г.И | |||

| ПОРТСИГАР С ПРИСПОСОБЛЕНИЕМ ДЛЯ СКРУЧИВАНИЯ ПАПИРОС | 1922 |

|

SU621A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-10-15—Публикация

1988-09-15—Подача