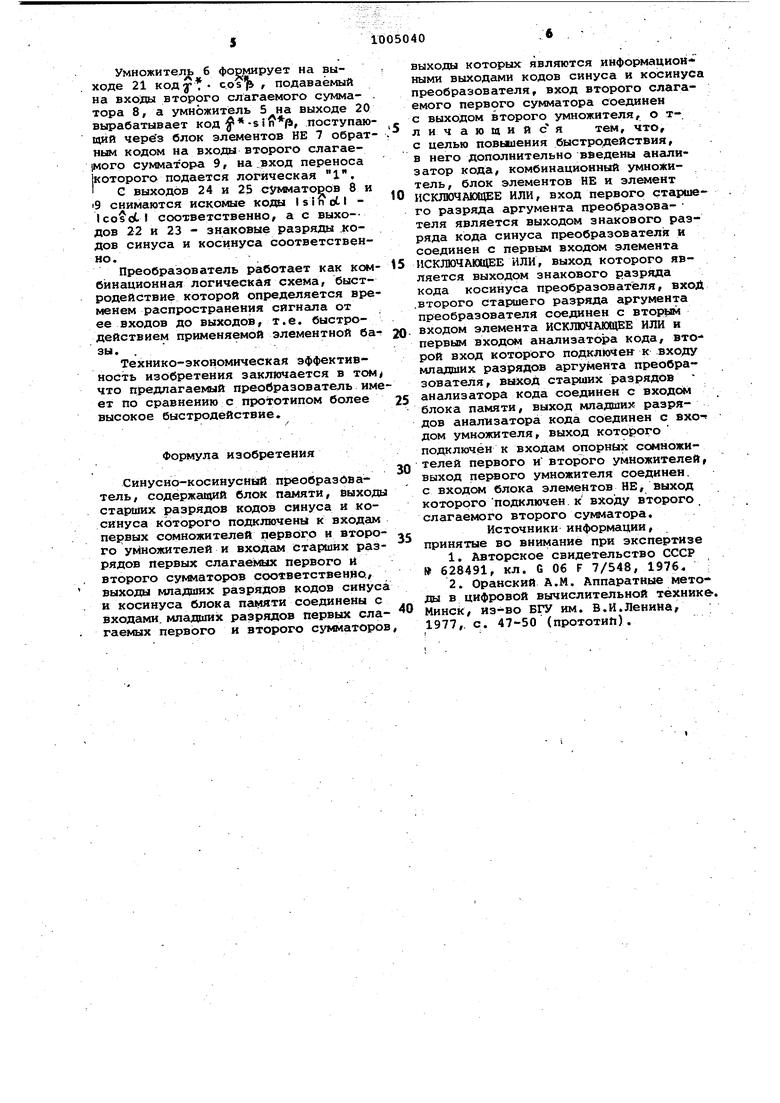

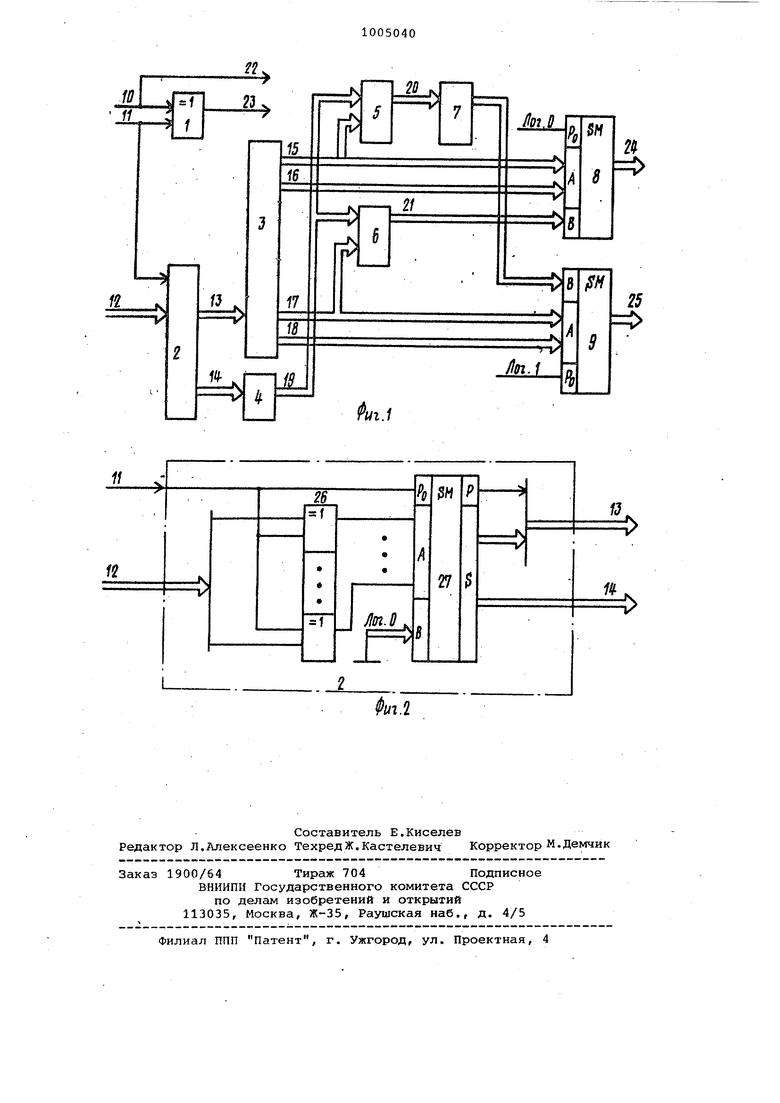

гаемых первого и второго сумматоро выходы которых являются инфррмацио ны:ми выходами кодов Синуса и косин преобразователя, вход второго слаг мого первого сумматора соединен с в ходом второгЬ умножителя, дополнительно введены анализатор кода, ком би г ационный умножитель, блок элемен тов НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого старшего разряда аргумента преобразователя является выхо дом знакового разряда кода синуса преобразователя и соединен с первы входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вы ход которого является выходом знако вого разряда кода косинуса преобраз вателя, вход второго старшего разряда аргумента преобразователя соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и первым входам аналиштора кода, второй вход которого подключен к входу младших разрядов аргумента преобразователя, выход старших разрядов анализатора кода соединен с входом блока памяти, выход младших разрядов анализатора кода соединен с входом умножителя, выход которого подключен к входам опорных сомножителей первого и второго умножителей, выход первого yм oжитeля соединен-с входом блока эле;ментов НЕ, -выход которого подклю jei- к входу второго слагаемого второгО сумматора. На фиг. 1 приведена структурная схема синусно-косинусного преобразоЕ ателя; на фиг. 2 - функциональная схема анализатора кода. Устройство содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 1, анализатор 2 код блок 3 памяти, комбинационный умножитель 4, умножители 5 и б, блок элементов НЕ 7, сумматоры 8 и 9, входы 10 и 11 старших и кодовый вхо 12 младших разрядов кода аргумента, выходы 13 и 14 старших и младших ра рядов кода анализатора 2 соответственно, кодовые выходы 15 - 18 блока 3 памяти, кодовый выход 19 комбинационного умножителя 4, кодовые выходы 20 и 21 умножителей 5 и 6 соогветствённо, выходы 22 и 23 знаKOBidx разрядов кодов синуса и косинуса соответственно, и выходы 24 к 25 кодов синуса и косинуса преобразователя соответственно. Анализатор 2 кода содержит группу 26 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и сумматор 27. Предлагаемый преобразователь выраб.зтьгоает по ( h + 2)-разрядному коду с а)гумента oi (h+ 1)-разрядные коды синуса и косинуса sinoi и Код оС и аргумент oL связаны соотношением . ot 2J/rioC. , где oi- - разрядная цифра i-го разряда кода оС . Два старших разряда кода ot определяют знаковые разряды кодов . л А , S in с, и cos оС .в соответствии с выражениями : Ф22 ot.i, Ф23 оС1 ©об2, где Ф22, Ф23 - знаковые разряды ко-дов . соответственно. Анализатор 2 кода выдает при 0 прямой код (при - дополнительный код ) по коду, образованному п младшими разрядами входного кода аргумента. Блок 3 памяти комбинационно вырабатывает п -разрядные коды slnfb и cos fb по коду р, , образованному старшими разрядами выходного кода анализатора 2.. Младшие (.т-1) разрядов выходного кода анализатора 2 образуют код у , соответствующий аргументу y J//22- J. 2 .Для представления ар1 п.-тт1+2 гумента f кодом радианах с весом младшего разряда л 2 служит комбинационный умножитель 4, реализующий операцию Умножители 5 и 6 формируют п-разрядные -коды произведений т-разряднсго кода на коды и cos ft, образованные старшими m разрядами кодов si и соответственно. Усечение кодов si при cos|b при умножении применяется для упрощения реализации умножителей 5 и б. При 2 m п погрешность умножения не превышает величины д,(щц 2. Преобразование кода и в коды I S i not I и осуществляется на основе соотношений Ilsino6bsinfb+f , .| CO§p-J 5iftV С подачей двух старших разрядов кода oL по входам 10 и 11 и остальных его разрядов по входу 12 преобразователя блок 3 памяти на выходах 15 и 16 вырабатывает код s i п fj , поступающий на входы первого слагаемого сумматора 8, а на выходах 17 и 18 - код cos fb , поступающий на входы первого слагаемого сумматора 9. Умножитель б формирует на вы, ходе 21 коду, cos , подаваемый на входы второго слагаемого сумматора 8, а умножитель 5 на выходе 20 вырабатывает код , поступающий через блок элементов НЕ 7 обратным кодом на входы второго слагае1МОГО сумматора 9, на вход переноса которого подается логическая 1. G выходов 24 и 25 сукиаторов 8 и i9 снимаются искомые коды I s i п о(. I IcosctI соответственно, а с выхо-дов 22 и 23 - знаковые разряды .кодов синуса и косинуса соответственно. Преобразователь работает как комбйнационная логическая схема, быстродействие которой определяется временем распространения сигнала от ее входов до выходов, т.е. быстродействием применяемой элементной ба эы. . , Технико-экономическая эффективность изобретения заключается в том что предлагаемый преобразователь име ет по сравнению с прототипом более высокое быстродействие. Формула изобретения Синусно-косинусный преобразователь, содержащий блок памяти, выходы старших разрядов кодов синуса и косинуса которого подключены к входам первых сомножителей первого и второ го умножителей и входам старших раз рядов первых слагаемых первого и второго суланаторов соответственно., выходы младагах разрядов кодов синус и косинуса блока памяти соединены с входами, младших раэр5шов первых ела гаемых первого и второго сумматоро выхода которых являются информацион ными выходами кодов синуса и косинуса преобразователя, вход второго слагаемого первого сумматора соединен с выходом второго умножителя, о т-. личаюадийс я тем, что, с целью повышения быстродействия, в него дополнительно введены анализатор кода, комбинационный умножитель, блок элементов НЕ и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, вход первого старшего разряда аргумента преобразова- теля является выходом знакового разряда кода синуса преобразователя к соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом знакового разряда кода косинуса преобразователя, вхоА .второго старшего разряда аргумента преобразователя соединен с вторьлм входом элемента ИСКЛЮЧАОДЕЕ ИЛИ и первым входом анализатора кода, втО рой вход которого подклк«е к входу младших разрядов аргумента преобразователя , выход старших разрядов анализатора кода соединен с входом блока памяти, выход младших разрядов анализатора кода соединен с входом умножителя, выход которого подключен к входам опорных сомножителей первого и второго умножителей, выход первого умножителя соединен, с входом блока элементов НЕ, выход которогоподключен, к входу второго, слагаемого второго сумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 628491, кл. G Об F 7/548, 1976 2.Оранский A.M. Аппаратные методы в цифровой вычислительной технике. Минск, из-во БГУ им. В.И.Ленина, 1977,. с. 47-50 (прототий) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Синусно-косинусный преобразователь | 1986 |

|

SU1327095A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1302273A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

Авторы

Даты

1983-03-15—Публикация

1981-08-21—Подача