увеличения емкости его блока памяти. Генератор содержит вход выбора режима преобразования, входы параллельного п-разрядного двоичного кода угла с весом младшего разряда 2 рад, три сумматора,.-два умножителя, блок памяти параллельного п -разрядного двоичного кода синуса угла от О до

() и/2 рад (где m - число адресных входов блока памяти, причем п т

7 т } т) , первый блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. Новым в генераторе является то, что он содержит два комму1

Изобретение относится к вычисли- тельной технике и предназначено для вычисления по двоичному п-разрядному коду угла, изменяющемуся от О до (l-Z ) -IT/Z рад, двоичного п-раз- рядного кода синуса или косинуса с высокой точностью и быстродействием.

Цель изобретения - повышение точности синусно-косинусного преобразователя.

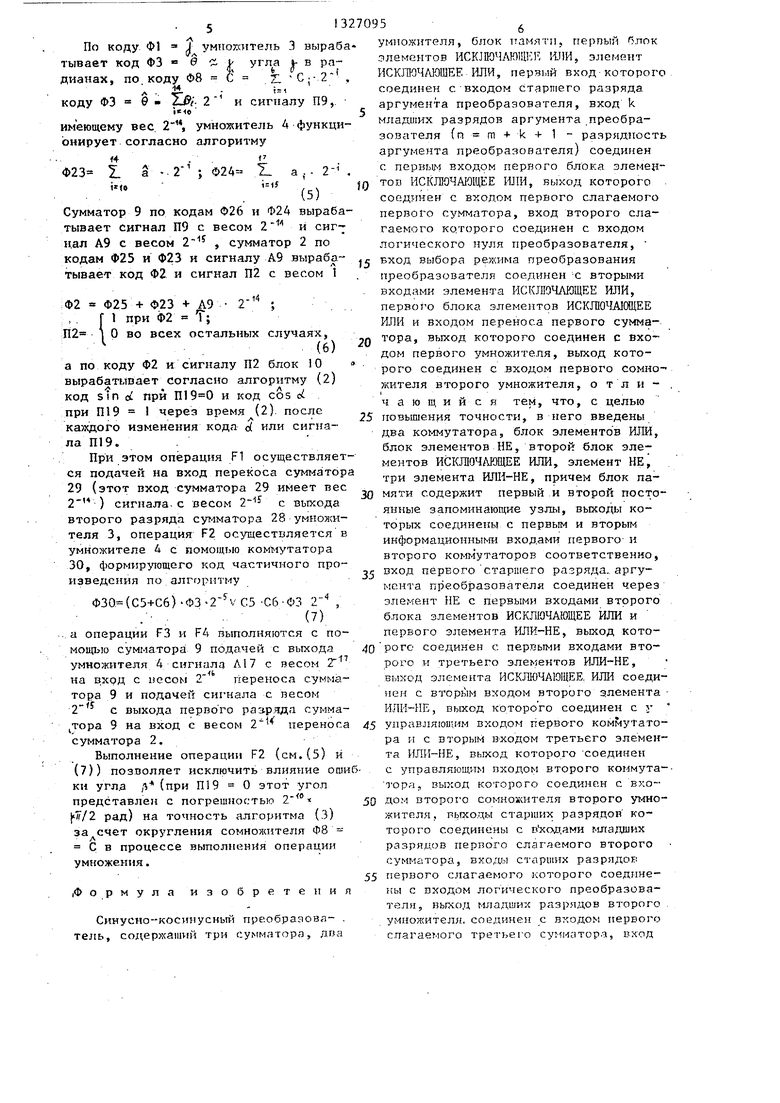

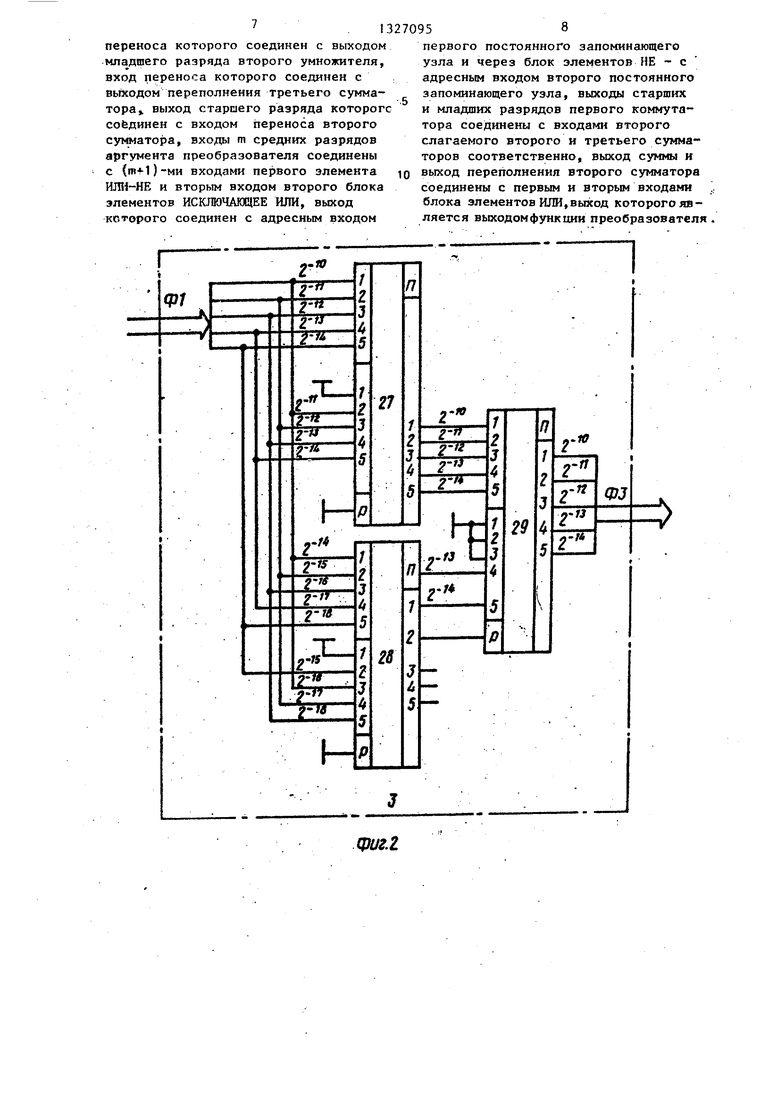

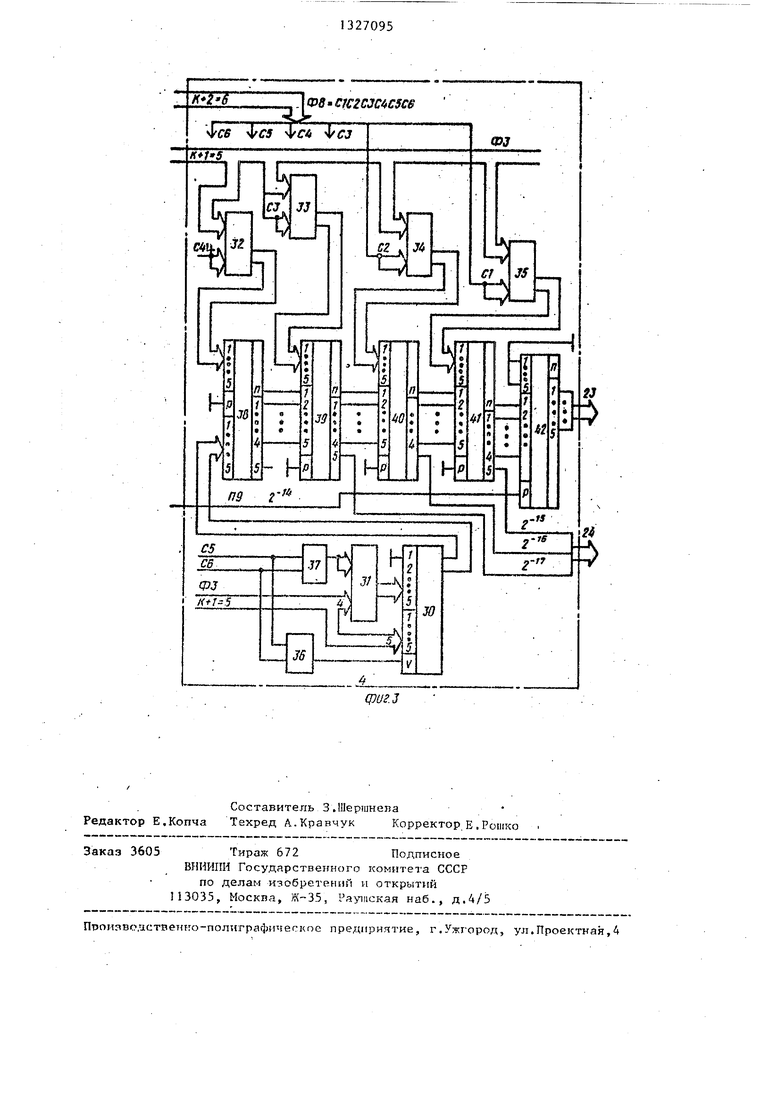

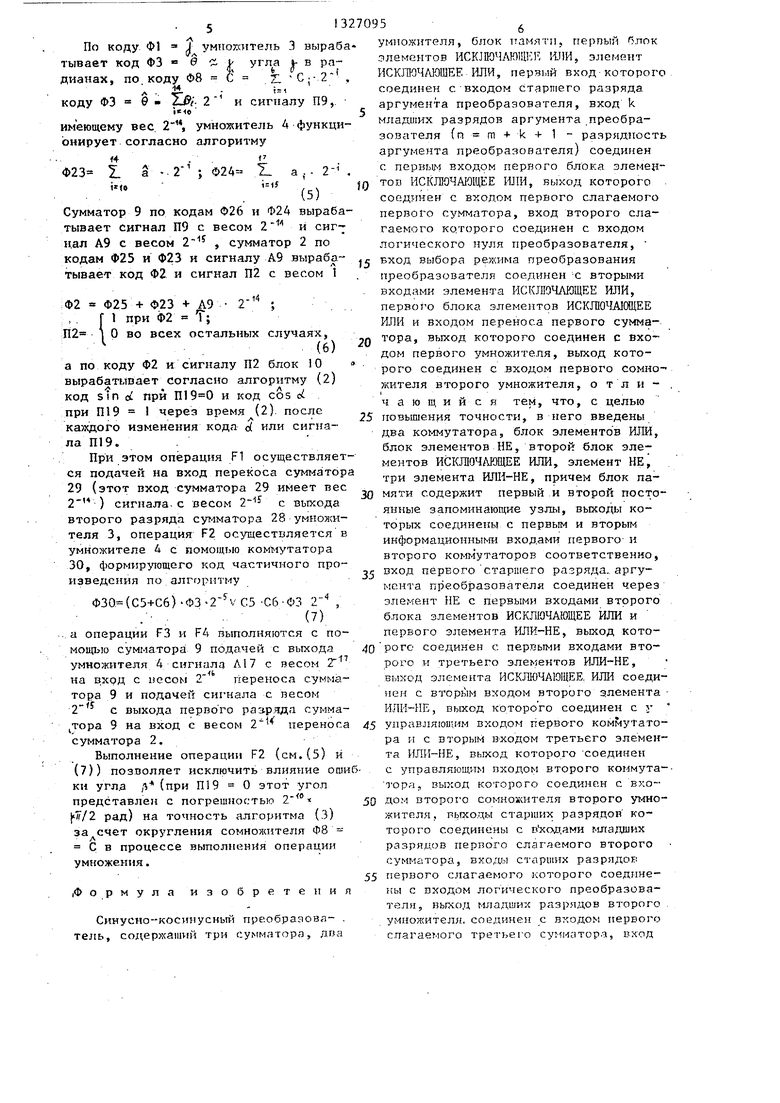

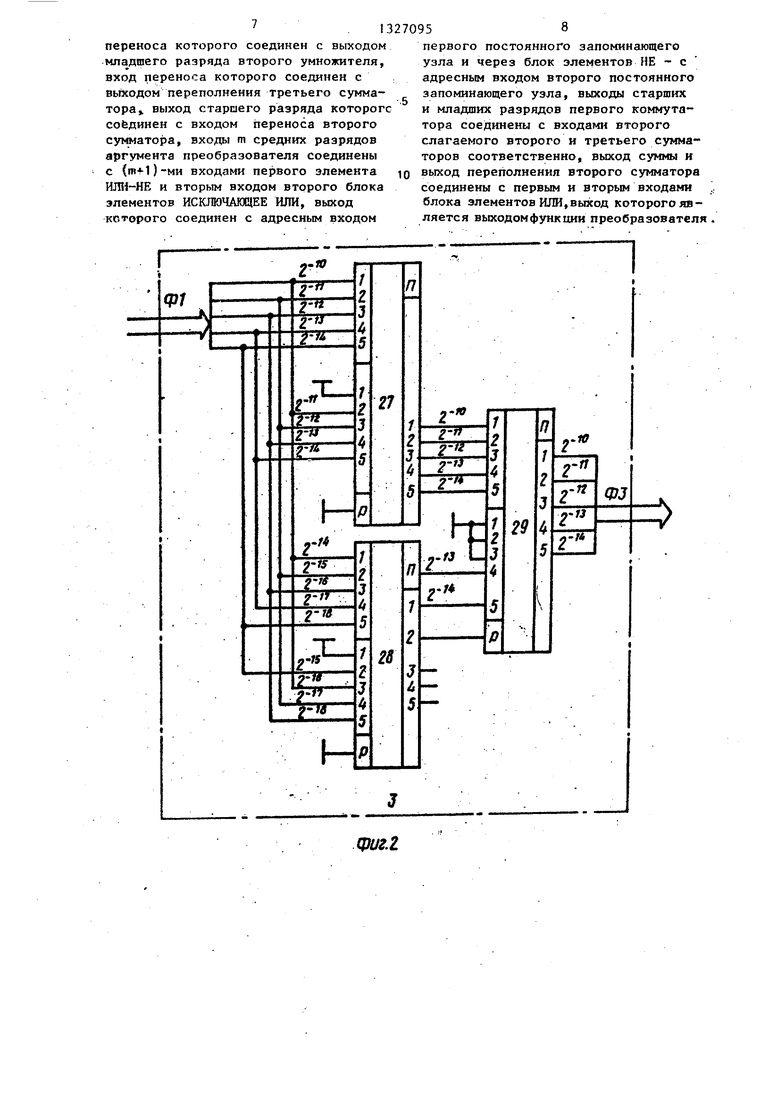

На фиг,1 Изображена функциональ- ная схема синусно-косинусного преобразователя; на фиг.2 - функциональная схема первого умножителя; на фиг.З - функциональная схема второго умножителя.

Преобразователь (фиг. 1) содержит первый 1 и второй 2 сумматоры, первый 3 и второй 4 умножители, блок памяти, образованный первым 5 и вторым 6 постоянным запоминающим узлом (ПЗУ), первый 7 И второй 8 коммутаторы, третий 9 сумматор, блок 10 элементов ИЛИ, первый 11 и второй 12 блоки .элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, блок 13 элементов НЕ, элемент 14 НЕ,.элемент 15 ИСКЛЮЧАКНЦЕЕ ИЛИ, первый 16, второй 17 и третий 18 элементы ЛЛИ-НЕ, управляющий вход 19, вход 20 первого старшего разряда, входы 21 m п - - k .- 1 старших разрядов и входы 22k младших разрядов (п -- 1 + m + k)- разрядного кода угла, выходы 23 старших и выходы 24 младших разрядов кода умножителя 4 и выходы 25п стартатора 7,8-, блок 10 элементов ИЛИ, выходы которого являются выходами преобразователя, блок 12 элементов ИСКЛЮЧАЮС1ЕЕ ИЛИ, блок 13 элементов ИЕр Элемент НЕ 14, и три элемента Ш1И-НЕ 16,17,18. Данный генератор может быть использован в специалнзи- рованньгх вычислителях с высоким быстродействием и точностью (с числом значап1их разрядов п 10), например, для цостроения цифрового преобразователя координат устройства отображения информации метеораднолокатора, 3 ил.

ших и выходы 26 остальных младших разрядов коммутатора 7.

Умножитель 3 содержит три (k+1)- разрядных сумматора 27 - 29.

Умножитель 4 содержит коммутатор 30, пять блоков элементов И (с первого 31 по 35), элемент 36 И, элемент 37 ИЛИ и пять сумматоров

(с первого 38 по пятьй 42), вход переноса пятого из которых является суммирующим входом умножителя 4, у которого выходы 23 образованы разряд- нь1ми выходами разрядов сумматора -42,

а разрядные выходы младших разрядов cyi fMaTopoB 41, 40 и. 39 образуют выходы 24.

Предлагаемый преобразователь (фиг.1 - 3) реализован для п 14 и k 4 на ИС серий 505 и 533 так, что ПЗУ- 5 содержит две ИС 505РЕЗ памяти 16-разрядного кода синуса в угле от ff/4 до (1-2 ) /2 рад (прошивки

007 и 0070), ПЗУ 6 - две ИС 505РЕЗ памяти 16-разрядного кода синуса в угле от О до (0, ) fi/2 рад (прошивки 0069 и 0068), сумматор 1 - одну ИС 533liM6, сумматор 2 - одну ИС 533ИМ5 и три ИС 533ИМ6, сумматор 9 - одну ИС 533ИМ5 коммутатор 7 - четыре ИС 533КП11, каждый из коммутаторов. 8 и 30 - две ИС 533КП11, умножитель 3 - две ИС 533ИМ5 и три ИС 533ИМ6, сумматоры 38-42 умножителя

4 выполнены на трех ИС 533ИМ5н пятиИС

533ИМ6, а остальные узлы выполнены на лргических элементах серии 533.

Сигнал на выходе переполнения и сигнал на разрядном выходе старшего разряда сумматора 9 обозначим через П9 и А9 соответственно. В предлагаемом ,генераторе операндами являются

{7Г/2). , (ТГ/2) I о,. 2- ;

(О

21 d-- 2 ; Ф22 . i-Z

Ф21

Aon

(1 - 7 ) - rf +

где - разрядная цифра -го { д .1,2,...,п) разряда кода; У - код, обратный коду о ; rf.,д- код, определяющий дополни- тельньп до я/2 угол-с(ед (;р/2) , т.е. oL +of л - «/2; 1 - код положительной единицы, определяемой в модифицированном дополнительном коде выражением t ,01,0..0. С учетом принятых обозначений и связей {1} работу генератора йожно описать следующим образом.

П19 sin (rfvni9 cos of stn у « s1n {/i+); -v« . .

/T/2{ni9 - Z: ci.-2- vni9 Z o(- 2 )v bt

i«

/} П19 (/i- r/2)vni9-/s ;

. ir/2 пТ9 Ф22УП19 (Ф22 .+ 2 ) ; .

4 Л 1119 0 vПi9fl(40(

В процессе вычисления блоки 11 - в угле от tf/A до ( ) 7Г/2 рад,, 13 и сумматор 1 вьфабатывают коды ФП второе ПЗУ 6 запрограммировано на

воспроизведение (п+2)- разрядного кода синуса в угле от О до (0,5 - - ) J/2 рад, ПЗУ 5, ПЗУ 6 и коммутаторы 7 и 8 вырабатывают коды 50

Ф12, Ф13, Ф1, элементы 15 - 18 - сигналы П15, , П17, . Первое ПЗУ 5 .запрограммировано на воспроизведение (п+2)-разрядного коДа синусу

Ф5 stn(0,5 + Ф12)- S /Zj

Ф6 stn фТ2 71/2;

Ф7 пТТ . Ф5УШ7-Ф6 - sfn /S « Ф25 + Ф26;

Ф8 (iiTs Ф5 /П18.Ф6) - (cos /J).

код d угла ci , коды sin of. Ф10, cos 0 Ф10, а также промежуточные коды, каждый из которых обозначается

буквой Ф с соответствующим номером,

Связь между кодом ot, сигналом П 20, кодами Ф21 и Ф22 и углом d характеризуется выражениями

п iti

/

ci,- 2 ;

(1)

20

Преобразователь является комбинационным устройством и по каждому изменению сигнала П19 или кода о/ через время, определяемое в основном временем обращения к блоку памяти (для ИС 505РЕЗ это время составляет 25 1500 не),

Т .Т2)

ofp

вырабатывает код синуса при П19 или косинуса при П19 I угла rf в 3Q соответствии с алгоритмом

О

2 )v

(3)

(4)

По коду Ф1 J умножитель 3 тывает код ФЗ 0 днанах, по.коду Ф8

умножителя, блок ттамяти, перпый блок элементов ИСК1ЮЧЛЮ1Ш Ш)И, элемент

14

г к УГЛЯ ft- В .-ijitiM ;ri 1 uri ii4ji juj i rv/iitijjj tL ifi c Jit;r-ii-ni

С z: C -.2 , ИСКЛЮЧАЮШЕЕ.ИЛИ, первый вход-которого

коду ФЗ 0 2 и сигналу ПЭ,

|ЧО

имеющему вес. , умножитель А функционирует согласно алгоритму

f4. f

Ф23 2. а - 2 ; Ф24 Z. itfo

а,- 2- (5)

соединен с-входом старшего разряда аргумента преобразователя, вход k младших разрядов аргумента преобразователя (п - m + k + 1 - разрядность аргумента преобразователя) соединен с первьм входом первого блока элемер- JQ тов ИСКЛЮЧАЮЩЕЕ ШШ, выход которого соедянен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом логического нуля преобразователя.

Сумматор 9 по кодам Ф26 и Ф24 вырабатывает сигнал П9 с весом и сиг-; нал А9 с весом 2 , сумматор 2 по

соединен с-входом старшего разряда аргумента преобразователя, вход k младших разрядов аргумента преобразователя (п - m + k + 1 - разрядность аргумента преобразователя) соединен с первьм входом первого блока элемер- JQ тов ИСКЛЮЧАЮЩЕЕ ШШ, выход которого соедянен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом логического нуля преобразователя.

кодам Ф25 и Ф23 и сигналу А9 выраба- j вход выбора режима преобразования тывает код Ф2 и сигнал П2 с весом 1

Ф2 П2

-,-14

Ф25 + Ф23 Л9 2 Г 1 при Ф2 Т; 12- I О во всех остальных случаях,

.)

а по коду Ф2 и сигналу П2 блок 10

вырабатывает согласно алгоритму (2) код sin 0 при и код cos ci при П19 I через время (2). после кавдого изменения кода о( или сигнала П19. .

При этом операция F1 осуществляется подачей на вход перекоса сумматора 29 (этот вход сумматора 29 имеет вес 2 ) сигнала-с весом с выхода второго разряда сумматора 28 умножителя 3, операция F2 осуществляется в умножителе 4 с помощью коммутатора 30, формирующего код частичного произведения по алгоритму

ФЗО(С5+С6)-ФЗ 2 Ч С5-С6-ФЗ 2- ;

. ,- .. (7) . а операции F3 и FA выполняются с помощью сумматора 9 подачей с выхода умножителя А сигнала Л17 с весом на цхрд с весом 2 переноса сумматора 9 и подачей сигнала с весом 2 с выхода перво го рааряда сумма- тора 9 на вход с весом сумматора 2.

Выполнение операции F2 {см.(5) и {)) позволяет исключить влияние ошибпреобразователя соединен -с вторыми

.- входами элемента ИСКЛОЧЛЮЩЕЕ ИЛИ, первого блока элеме 1тов ИСКЛЮЧАЮЩЕЕ ИЛИ и входом переноса первого сумма2Q тора, выход которого соединен с входом первого умножителя, выход которого соединен с входом первого сомножителя второго умножителя, о т л и - . чающийся тем, что, с целью

25 повышения точности, в него введены два коммутатора, блок элементов ИЛИ, блок элементов НЕ, второй блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, три элемента ИЛИ-НЕ, причем блок па30 мяти содержит первый и второй постоянные запоминающие узлы, выходы которых соединены с первым и вторым информационными входами первого- и второго комм утаторов соответственно,

j вход первого старшего разряда,, аргумента преобразователя соединен через элемент НЕ с первыми входами второго . блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и первого элемента ИЛИ-НЕ, выход кото40 роге соединен с первыми входами второго и третьего элементов ИЛИ-НЕ, элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом второго элемента - ИЛИ-НЕ, выход которого соединен с у переноса 45 управляющим входом первото коммутато- - ра и с вторым входом третьего элемента ИЛИ-НЕ, выход которого -соединен с управляющим входом второго копнута-ки угл.а /1 (при П19 О этот угол представлен с погрешностью Z рад) на точность алгоритма (З) за счет округления сомножителя Ф8 А

С В процессе выполнения операции умножения.

.Формула изобретени

Синусно-косинусный преобразова- тель, содержащий три сумматора,

умножителя, блок ттамяти, перпый блок элементов ИСК1ЮЧЛЮ1Ш Ш)И, элемент

:.-ijitiM ;ri 1 uri ii4ji juj i rv/iitijjj tL ifi c Jit;r-ii-ni

ИСКЛЮЧАЮШЕЕ.ИЛИ, первый вход-которого

соединен с-входом старшего разряда аргумента преобразователя, вход k младших разрядов аргумента преобразователя (п - m + k + 1 - разрядность аргумента преобразователя) соединен с первьм входом первого блока элемер- тов ИСКЛЮЧАЮЩЕЕ ШШ, выход которого соедянен с входом первого слагаемого первого сумматора, вход второго слагаемого которого соединен с входом логического нуля преобразователя.

вход выбора режима преобразования

тора, выход которого соединен с вхо- дом второго сомножителя второго умножителя, вьтходы старших разрядов которого соединены с в ход.ами мпа;ш их разрядов первого слагаемого второго с-умматора, входы старших разрядов riepBoro слагаемого которого соединены с входом логического преобразователя, выход младши-х разрядов второго , умножителя, соединен с Б-ХОДОМ первого слагаемого третьего сумматора, вход

переноса которого соединен с выходом младшего разряда второго умножителя, вход переноса которого соединен с вьпсодом переполнения третьего сумматора выход старшего разряда которого соединен с входом переноса второго cyNttiaTopa, входы m средних разрядов аргумента преобразователя соединены с ()-ми входами первого элемента HJUf-HE и вторым входом второго блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с адресным входом

8

первого постоянного зaпo п нaющёгo узла и через блок элементов НЕ с адресным входом второго постоянного

запоминающего узла, выходы старших и младших разрядов первого коммутатора соединены с входами второго слагаемого второго и третьего сумматоров соответственно, выход суммы и

вькод переполнения второго сумматора соединены с первым и вторым входами блока элементов ИЛИ,выход которого является выход ом функции преобразователя

Фиг.2

ЛФ8-СГС2СЗС4СЗСе

св т Ф« cj

J-

Uv Як

t)

jj

-v;

h

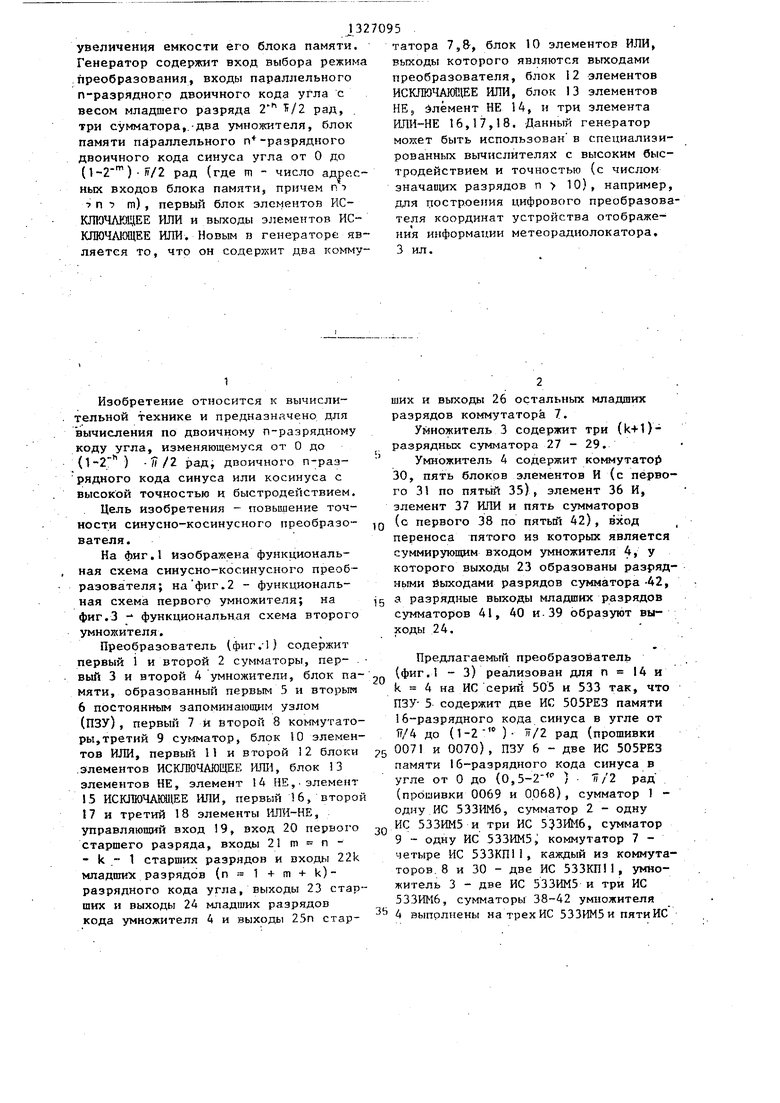

Составитель З.Шершнепа Редактор Е.Копча Техред А.Кравчук Корректор Е .Рошко

Заказ 3605 Тираж 672Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Ра пиская наб., д.4/5

Производственпо-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

(PJ

.J-LA

J4

г4

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Цифровой вычислитель функций | 1986 |

|

SU1354187A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Синусно-косинусный преобразователь | 1981 |

|

SU1005040A1 |

| Синусно-косинусный преобразователь | 1986 |

|

SU1302273A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Генератор напряжений | 1982 |

|

SU1129718A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления параллельных п-раз- рядных двоичных кодов синуса и коси- ну са угла, представленного параллельным двоичным кодом. Цель изобретения повышение точности генератора без СО N5 vj О СО О1 Фиг.1

| Устройство для контроля двухтактного двоичного счетчика | 1981 |

|

SU970375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ТОРМОЖЕНИЯ ПОЕЗДА ПРИ РАСШИРЕНИИ ПУТИ СВЕРХ НОРМЫ | 1925 |

|

SU5040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-30—Публикация

1986-02-24—Подача