О5 СО СО -U

Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных и многопроцессорных магистральных вычислительных систем

Цель изобретения - упрощение организации вычислительного процесса и отладки математического обеспечения

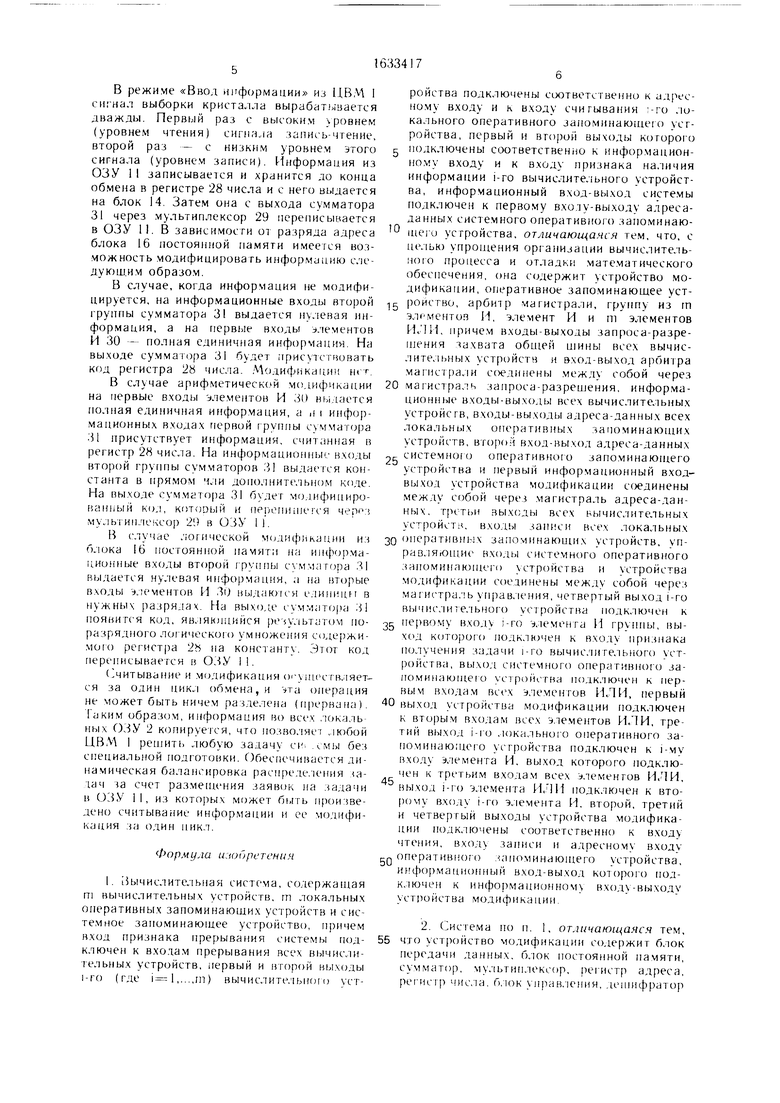

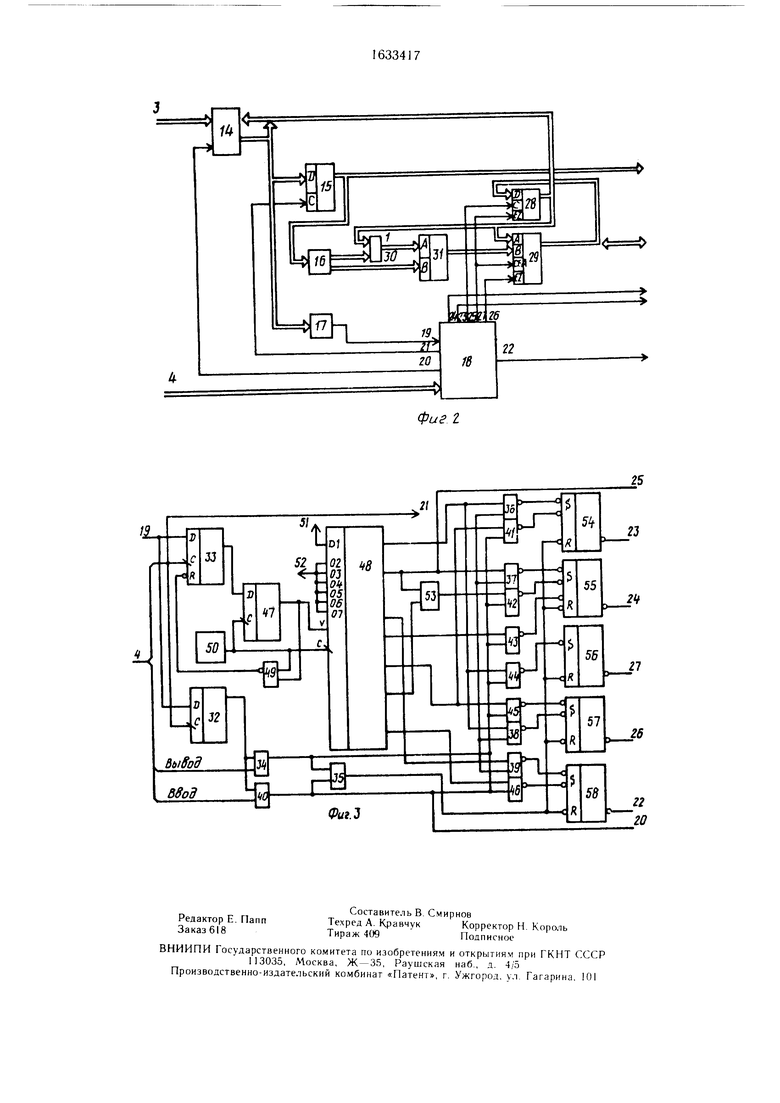

На фиг 1 представлена схема вычислительной системы, на фиг 2 - схема устройства модификации, на фиг 3 - схема блока управления устройства модификации

Вычислительная система содержит m вычислительных устройств 1. m локальных оперативных запоминающих устройств 2, магистраль 3 адреса-данных, магистраль 4 управления, системное оперативное запоминающее устройство 5, устройство 6 модификации, арбитр 7 магистрали, элемент И 8. элементы ИЛИ 9, элементы И 10 группы, оперативное запоминающее устройство 11, информационный вход-выход 12 вычислительной системы, вход 13 признака прерывания вычислительной системы

Устройство 6 модификации содержит блок 14 передачи данных, регистр 15 адреса, блок 16 постоянной памяти, дешифратор 17, блок 18 управления, вход 19 запуска блока управления, выходы с первого по восьмой 20-27 блока управления, регистр 28 числа, мультиплексор 29, элементы И 30 группы, сумматор 31

Блок 18 управления содержит тржгер 32 ключа (ТгКл), триггер 33 запуска (ТгЗап) первый элемент И 34, первый элемент ИЛИ 35, с первого по четвертый элементы И-НЕ 36 -39, второй элемент И 40, с пятого по десятый элементы И - НЕ 41 -46, триггер 47 управления (TiYnp), сдвиговый регистр 48, одиннадцатый элемент И-НЕ 49, генератор 50 тактовых импульсов, вход 51 ло ической единицы, входы 52 ло ического нуля, второй элемент ИЛИ 53, триггер 54 чтения-записи (TYWR), триггер 55 выборки кристалла (TrCS), первый триггер 56 разрешения (TrEZl), второй триггер 57 разрешения (ТгЕ/2), триггер 58 ответа (ТгОтв)

Вычислительная система работает сле- образом

После включения питания производится обнуление всех оперативных запоминающих устройств системы, контроль вычислительных устройств 1 Затем по сигналу преры вания с входа 13 инициируется решение задач в вычислительных устройствах 1 (ЦВМ), которые начинают обращаться к оперативному запоминающему устройству 11 (ОЗУ), послав запрос и получив разрешение на захват магистрали от арбитра 7 Одна из ЦВМ 1, захватывающая магистраль, считывает признак головной ЦВМ 1 из ОЗУ 11, если он есть, становится головной и проводит модификацию этого признака за этот же цикл обмена Далее она обращается к системному оперативному запоминающему устройству (ОЗУ 5) для анализа состояния внешней среды, в зависимости от которого формирует заявки на решение задач и чаносит их в ОЗУ 11 ЦВМ 1, обратившись к ОЗУ 11 и выяснив, что она не является головной, обращается к ячейке заявок, выбирает заявку и модифицирует ячейку Следующая из ЦВМ 1, обратившись к той же ячейке заявок ОЗУ 11, не получит той же информации и начнет решать следующую по приоритету задачу и т д Так

обеспечивается динамическая балансировка распределения задач между ЦВМ 1

Системную информацию все ЦВМ 1 получают от системного ОЗУ 5, связанного с внешними устройствами вычислительной системы через информационный вход-выход 12 Для хранения текущей оперативной информации в ЦВМ 1 имеются внутренние ОЗУ Для хранения копируемой информации используются локальные ОЗУ 2

Запись информации i и ЦВМ 1 в 1-е ло0 кальное ОЗУ 2 производится через внешнюю магистраль При этом все локальные ОЗУ 2 имеют одинаковый ключевой адрес, поэтому информация от любой ЦВМ 1 записывается во все локальные ОЗУ 2, таким образом во все локальные ОЗУ 2 информация копируется При этом информация в одну из ЦВМ 1, производящую запись, поступит только после совпадения ответов от всех локальных ОЗУ 2 на элементы И 8 Затем она, пройдя через соответствующий элемент ИЛИ

о и простробировавшись на соответствующем элементе И 10 сигналом «Обмен, поступает в соответствующую ЦВМ 1 Этим обеспечивается готовность любой из ЦВ 1 выполнять любую задачу

5 Устройство 6 модификации совместно с ОЗУ 11 функционирует следующим образом По магистрали 3 адреса-данных на первый информационный вход-выход блока 14 поступает адрес Младшие разряды адреса с его второго информационного входа-выхода по0 ступают на регистр 5 адреса, где фиксируются передним фронтом сигнала «Обмен, поступающим из магистрали 4 Старшие ключевые разряды адреса расшифровываются дешифратором 17 и устанавливают триггер 33 блока 18 управления по сигналу «Обмен После привязки сигнала запуска на триггере 47 к частоте генератора 50 запускается сдвиговый регистр 48 Одновременно устанавливается триггер 32, разрешая прохождение сигналов «Ввод или «Вывод

0 чере элементы И 34 и 40 для формирования сигналов управления

В режиме «Вывод информации из ЦВМ 1 на триггере 54 формируется импульс, который обеспечивает запись информации в ОЗУ 1 1 На триггере 55 формируется импульс,

5 обеспечивающий срабатывание ОЗУ II В ОЗУ 11 производи п. я запись входных данных, поступающих . з устройства 6 модификации

В режиме «Ввод информации из I с и-на т выборки кристалла вырабатывается дважды Первый раз с высоким уровнем (уровнем чтения) сиг HIM ь чтение второй раз - с низким уровнем зтого еигната (уровнем записи) Информация из ОЗУ 1 I записывается и хранится до конца обмена в регистре 28 числа и с него выдается на блок 14 Затем она с выхода сумматора 31 через мультиппексор 29 переписывается в ОЗУ 11 В зависимости от разряда адреса блока 16 постоянной памяти имеется вот можность модифицировать информацию с к дуюшим образом

В случае, когда информация не модифи цируется на информационные входы второй 1руппы сумматора 31 выдается ну тевая ин формация, а на первые вицы мемснтов И 30 потная единичная информация На выходе суммаюра 31 бу дет трис утс гновать код регистра 28 чис ia Чодифнкаци не г

В случае арифметической мо тиф жации на первые входы цементов И 10 иные гея по тая е типичная информация а ,м инфор мационныч входах первой группы сумматора 51 присутствует информация считанная в регистр 28 чиста На информационны вчош второй группы сумматоров 51 вытается кон станта в прямом ч ш допишите ьном коде На выходе i у юра II будет мотифиииро ван||ЫИ ко1 к т )г)ыи и петппипкчя ч-V1

1У 1Ь|ИП СчСОр 21 В 05х- 11

В /отичсскои )1каиии из б юка Ib постоянной намята нт ипфопма донные второй грмпты СУМ 1 iropa 5| вы tat к я нулевая информация .1 на вторые вхо т,ы - е ментов И 10 вы т поп я е титп цм в нужных разря ах На а еуммаюра i

ПОЯВИТСЯ КОТ. ЯВ ТЯЮТ ТИИСЯ реМУ |ЬГ. ЮМ ПО

ра зря июю тог и чес ко и) у множен и я со т,ержи мою регистра 28 на констанг -Этот KOI, переписывается в O5V II

( читывание и мо шфикапия о ушесгвгяет- ся за о тин цик i обмена, и та операция не может быть ничем рале тс на (прервана)

аким образом информация во всех юктть ных О 2 копируется что позвотсг :юбои ЦВМ 1 решить тюбую задачу ei без специатьной подютовки Обеспечивается т.и намическая батажировка распре ic кния н

1ач за счет размещения заявон на iaj.ain в О iV 11 из которых может быть про и ше

it но считывание информации и ее мо шфи кация за от.ин пикт

Форму ш июирстснич

5ычис жте тьная система соиржащая гп вычис титетьных устройств m токатьных оперативных запоминающих устройств и сие темное запоминающее устройство причем вход признака прерывания системы по i ктючен к вхотам прерывания всех вычисти тетьныч устройств первый и второй выходы i го (г т.с i 1 тп) вычис тите 1ьно о усг

0

5

роиства пожтючены еоответ твенно к а цчс НОМУ входу и к входу считывания то ю ка тьного оперативного запоминающею уст роиства первый и второи выхош которого по тключены соответственно к информацией novy входу и к вхиду признака на шчия информации i го вычислите |Ьного Устройст ва информационный вхот. выхот. системы поткшчен к первому ВХОТУ выхоту атреса данных системного оперативного запоминаю шею устройства отмечающаяся тем что с та 1ью упрощения орт анизации вычис 1итеть

юю процесса и отладки математическою обеспечения она (одержит устройство мо дификапии оперативное запоминающее уст роис гво арбитр магистрат, группу из m эп1 менточ И этемент И и m элементов ИЛ1 причем входы выходы запроса разре шения захвата общей шины всех вычис

титетьных устройств и вло: выхот, арбитра магистрат соетинены меж IA собой через магистраль запроса разрешения информа ционные входы выхот.ы всех вычис тите тьных устройств входы выхотыафеса данных всех токатьных оперативных запоминающих устройств вгоро ( вхо i выхо i а т.рее а данных системно о оперативною запоминающего устройства и первый информационный вход- выхсн устройства модификации соединены меж т собой через магистра ть адреса т.ан ных третьи выхс аы всех ьычис титетьных ус роистз вхош заптчи токатьных оперативщ х за ю пинающих устройств уп рав гяющис вхо ты системного оперативного з шомин тюще п устройства и Устроиства мо 1ИФИ1 ации соединены меж iy собой через мат ис тра ь У прав к ния четвертый выход i го вычти нт е тьною устройства псмктючен к первому вчо ТУ го к мен га И группы вы ход которою потктючен к вхо и признака потучения i го вычис т гетьного УСТ роиства выхсм системного опера г.шною за поминающею устройства потктючсн к пер вым вхотам всех моментов ИЛИ, первый выхот. Устройства мсмификации ттодктючен к вторым вхо1ам всех цементов ИЛИ тре тип выхо i i io юкатьно о оперативного за поминаю цего устройства подктючен к i му вхо u j темен га И выхот, которого подклю чен к третьим вхтым всех тементов И,Г1И выход i го змемента И 1И подктючен к вто рому вхо ТУ i го э |емента И второй третий и четвертый выходы устройства мо тифика ции подкпотены соответственно к входу чтения вхо и записи и атресному входу оперативно, о мпоминаюшего Устройства информационный вхот выхот которою под ктючен к информационному входу ВЫХОДУ устройства модификации

0

0

5

0

2 ( истема по п 1 от гичающачс ч тем что устройство модификации сепержит бток передачи тайных б юк постоянной памяти сумматор му гьтиптексор риистр aipeca ре г ис тр чис та Г юк у прав гения и шифратор

7

и группу элементов И, причем первый информационный вход-выход устройства подключен к первому информационному входу- выходу блока передачи данных, второй информационный вход-выход которого подключен к выходу регистра числа, к первому информационному входу мультиплексора, к первым входам элементов И группы, к информационному входу регистра адреса и к входу дешифратора, выход которого подключен к входу запуска блока управления, второй информационный вход-выход устройства подключен к выходу мультиплексора и к информационному входу регистра числа, управляющий вход устройства подключен к входу режима блока управления, выходы первого по седьмой которого подключены со ответственно к управляющему входу блока передачи данных, к входу записи-считывания

1;

8регистра адреса, к первому, второму, третьему выходам устройства, к входу записи-считывания регистра числа и к входу разрешения мультиплексора, выход регистра адреса подключен к четвертому выходу устройства и к адресному входу блока постоянной памяти, выходы первой группы которого подключены соответственно к вторым входам элементов И группы, выходы которых подключены к информационным входам первой группы сумматора, информационные входы второй группы которого подключены соответственно к выходам второй группы блока постоянной памяти, выход сумматора подключен к второму информационному входу мультиплексора, восьмой выход блока управления подключен к входу разрешения регистра числа и к управляющему входу мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения патологических образований в легких | 1989 |

|

SU1623619A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для контроля хода программ | 1983 |

|

SU1101831A1 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ПАКЕТОВ ИНФОРМАЦИИ | 1994 |

|

RU2075778C1 |

| Устройство для контроля ЦВМ | 1987 |

|

SU1509908A1 |

| Устройство для ввода информации | 1987 |

|

SU1529208A1 |

| Устройство для контроля магистралей в ЭВМ | 1981 |

|

SU970376A1 |

| Устройство для сопряжения ЦВМ с внешним устройством | 1989 |

|

SU1661779A1 |

| Резервированная система | 1990 |

|

SU1785087A1 |

| Устройство для тестового контроля цифровых вычислительных машин | 1981 |

|

SU964647A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многомашинных и многопроцессорных вычислительных систем. Цель изобретения - упрощение организации вычислительного процесса отладки математическою обеспечения. Цель достигается тем, что вычислитечьная система содержит m вычислительных устройств 1, m локальных оперативных запоминающих устройств 2, системное оперативное запоминающее устройство 5, устройство 6 модификации, арбитр 7, элемент И 8, m элементов ИЛИ 9, группу из m элементов И 10. 1 з.п. ф-лы, 3 ил.

Фиг I

| Ларионов А | |||

| М., Майоров С | |||

| А и Новиков Г | |||

| И | |||

| Вычислительные комплексы системы и сети | |||

| - Л.: Энергоатомиздат, 1987, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Панфилов И | |||

| В | |||

| и Половко А | |||

| М | |||

| Вычислительные системы | |||

| - М.: Советское радио, 1980, с | |||

| Машина для добывания торфа и т.п. | 1922 |

|

SU22A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1991-03-07—Публикация

1989-01-02—Подача