ь

Со со

4Ь

СО Јъ

| название | год | авторы | номер документа |

|---|---|---|---|

| Система передачи цифровой информации | 1990 |

|

SU1786679A1 |

| Декодирующее устройство | 1985 |

|

SU1282334A1 |

| Устройство для формирования пачек импульсов | 1991 |

|

SU1812617A1 |

| Устройство для управления ленточным перфоратом | 1988 |

|

SU1658180A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1777143A2 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1290537A1 |

| Устройство для сжатия и передачи телеметрической информации | 1987 |

|

SU1640729A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Устройство для кодирования и декодирования цифрового телевизионного сигнала | 1988 |

|

SU1566485A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации. Устройство осуществляет декодирование кода Манчестер и обнаружение одиночных ошибок, что повышает его помехоустойчивость. Устройство содержит блок 1 выделения синхроимпульсов, триггер 2, элементы НЕ 3 и 4, регистры 5 и 6, блоки 7 и с контроля четности, элемент И 9 и блоки 10 и 11 ключей. 4 ил.

фуг/

Изобретение относится к электросвязи и может использоваться в системах передачи цифровой информации.

Целью изобретения является повыше- ние помехоустойчивости устройства.

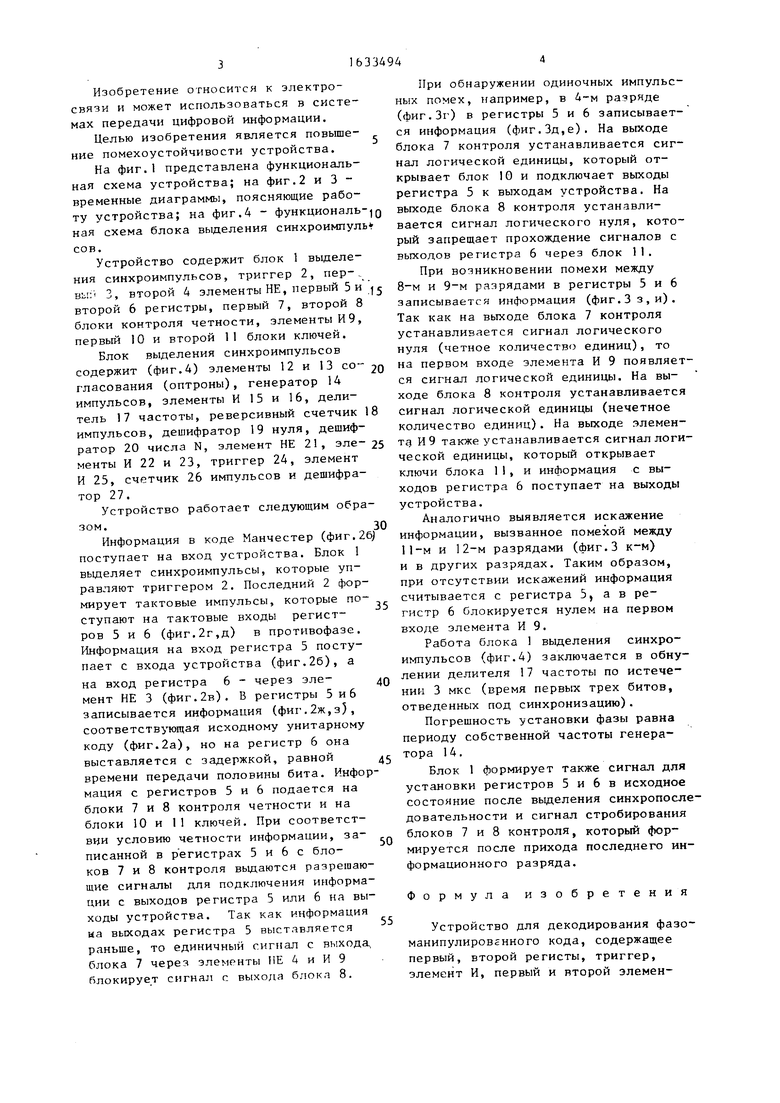

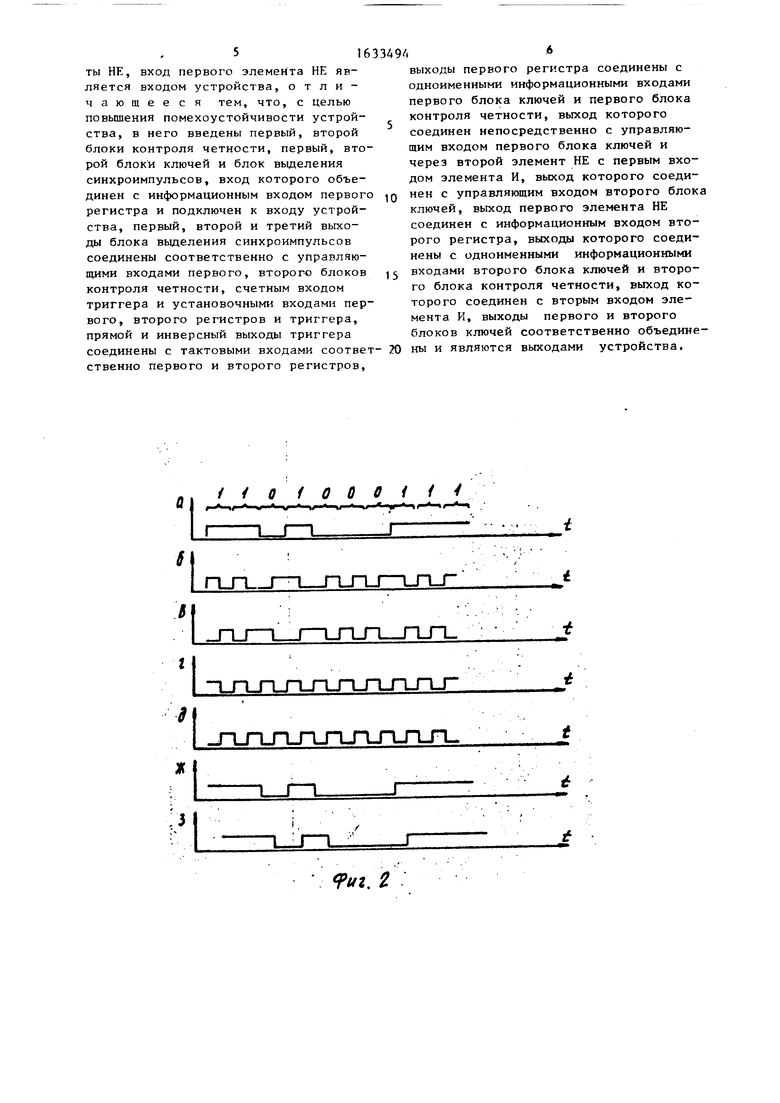

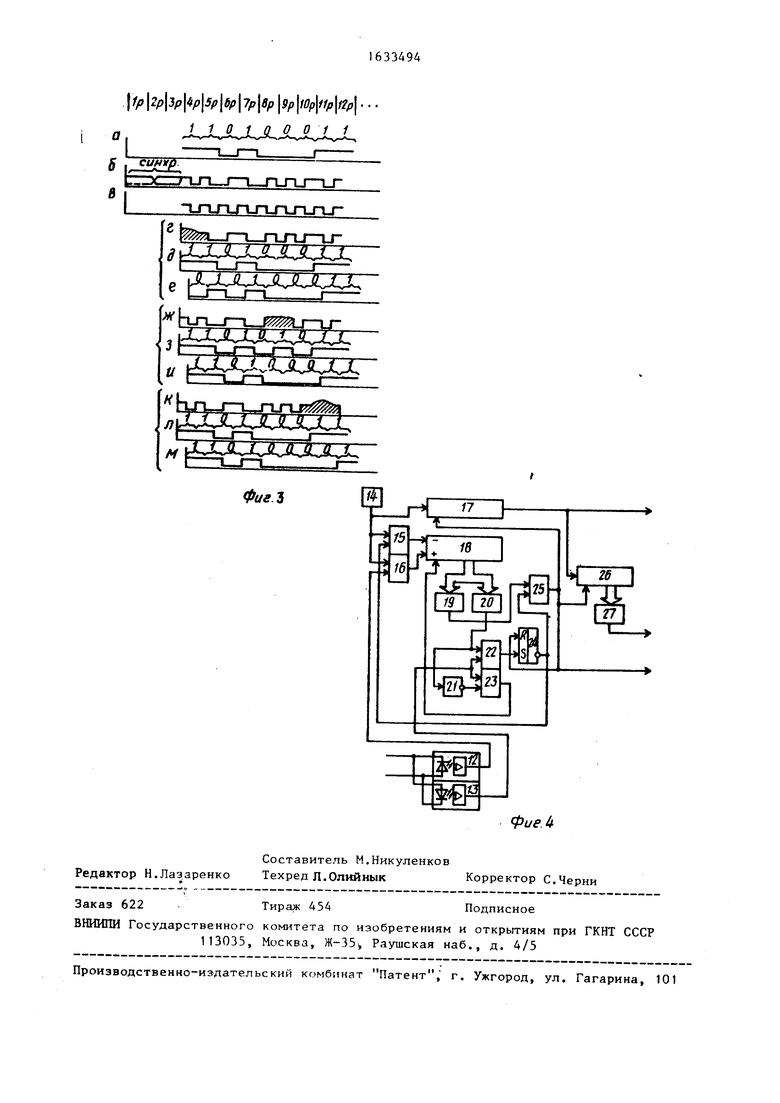

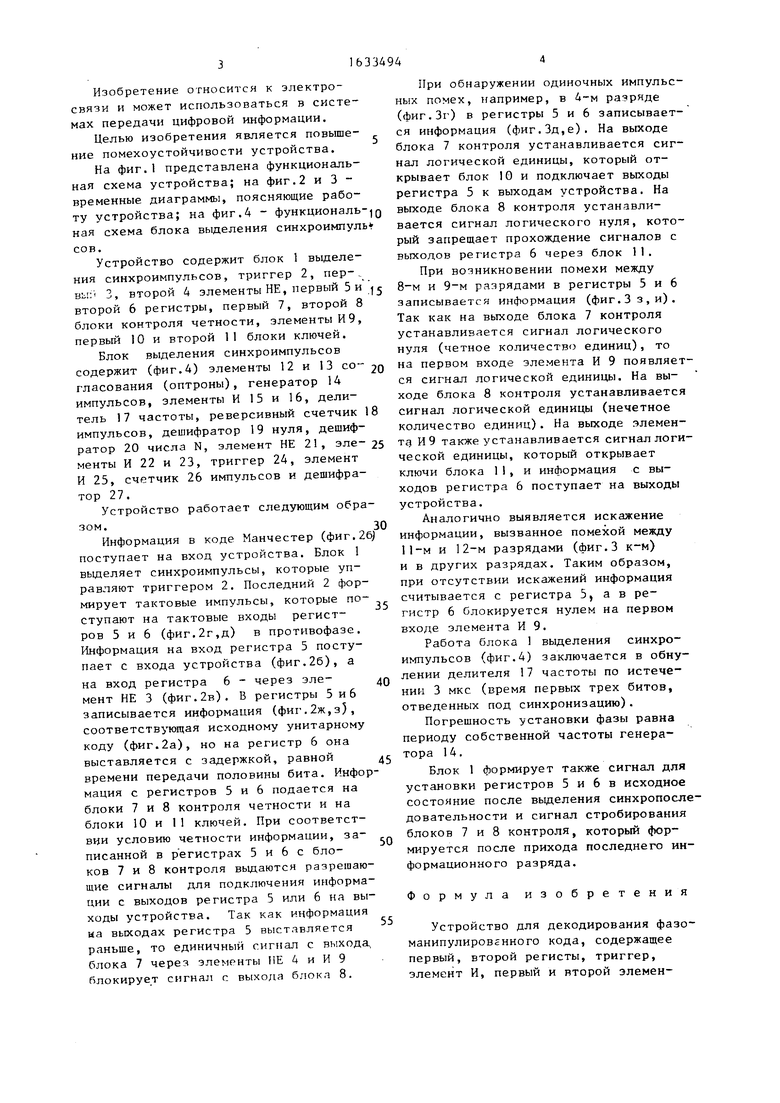

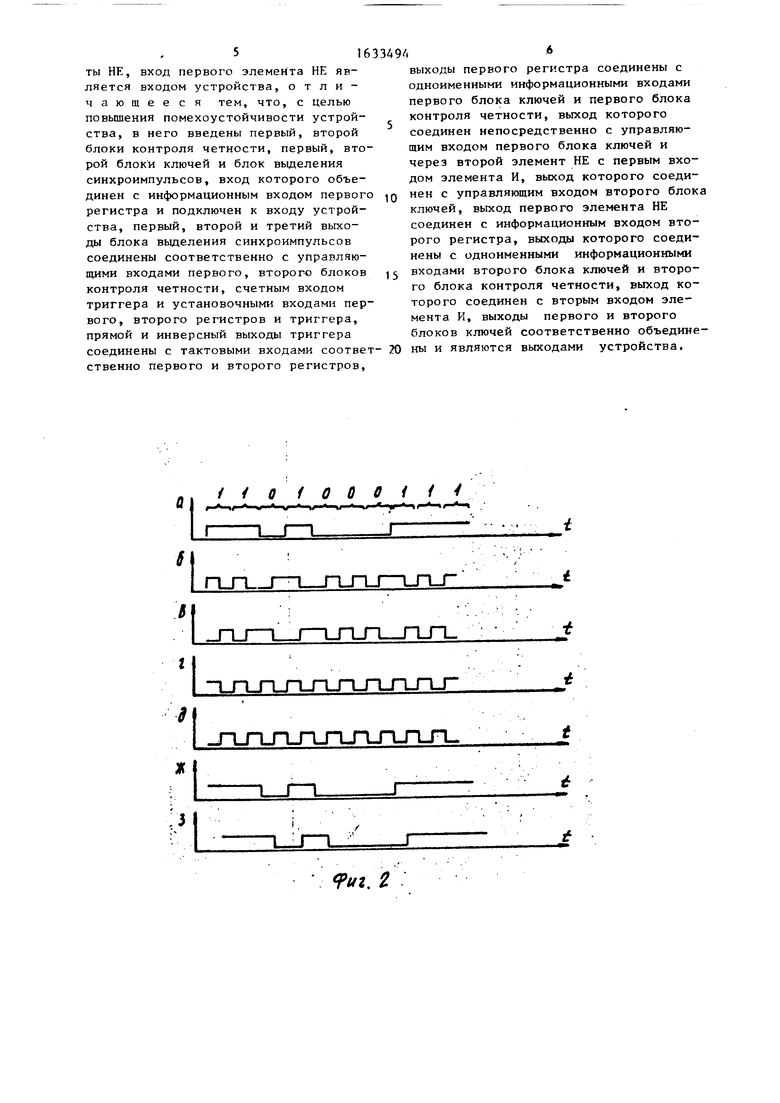

На фиг.1 представлена функциональная схема устройства; на фиг.2 и 3 - временные диаграммы, поясняющие работу устройства; на фиг.4 - функциональ ная схема блока выделения синхроимпул сов.

Устройство содержит блок 1 выделения синхроимпульсов, триггер 2, пер-. вы: 3, второй 4 элементы НЕ, первый 5 и второй 6 регистры, первый 7, второй 8 блоки контроля четности, элементы И9, первый 10 и второй 11 блоки ключей.

Блок выделения синхроимпульсов содержит (фиг.4) элементы 12 и 13 со- гласования (оптроны), генератор 14 импульсов, элементы И 15 и 16, делитель 17 частоты, реверсивный счетчик импульсов, дешифратор 19 нуля, дешифратор 20 числа N, элемент НЕ 21, эле- менты И 22 и 23, триггер 24, элемент И 25, счетчик 26 импульсов и дешифратор 27.

Устройство работает следующим образом.

Информация в коде Манчестер (фиг.2б поступает на вход устройства. Блок 1 выделяет синхроимпульсы, которые управляют триггером 2. Последний 2 формирует тактовые импульсы, которые по- ступают на тактовые входы регистров 5 и 6 (фиг.2г,д) в противофазе. Информация на вход регистра 5 поступает с входа устройства (фиг.2б), а на вход регистра 6 - через эле- мент НЕ 3 (фиг.2в). В регистры 5и6 записывается информация (фиг.2ж,з), соответствующая исходному унитарному коду (фиг.2а), но на регистр 6 она выставляется с задержкой, равной времени передачи половины бита. Информация с регистров 5 и 6 подается на блоки 7 и 8 контроля четности и на блоки 10 и 11 ключей. При соответствии условию четности информации, за- писанной в регистрах 5 и 6 с блоков 7 и 8 контроля выдаются разрешающие сигналы для подключения информации с выходов регистра 5 или 6 на выходы устройства. Так как информация иа выходах регистра 5 выставляется раньше, то единичный сигнал с выхода, блока 7 через элементы НЕ 4 и И 9 блокирует сигнал с выхода блока 8.

При обнаружении одиночных импульсных помех, например, в 4-м разряде (фиг.Зг) в регистры 5 и 6 записывается информация (фиг.Зд.е). На выходе блока 7 контроля устанавливается сигнал логической единицы, который открывает блок 10 и подключает выходы регистра 5 к выходам устройства. На выходе блока 8 контроля устанавливается сигнал логического нуля, который запрещает прохождение сигналов с выходов регистра 6 через блок 11.

При возникновении помехи между 8-м и 9-м разрядами в регистры 5 и 6 записывается информация (фиг.3 з , и). Так как на выходе блока 7 контроля устанавливается сигнал логического нуля (четное количество единиц), то на первом входе элемента И 9 появляется сигнал логической единицы. На выходе блока 8 контроля устанавливается сигнал логической единицы (нечетное количество единиц). На выходе элемента И 9 также устанавливается сигнал логической единицы, который открывает ключи блока 11, и информация с выходов регистра 6 поступает на выходы устройства.

Аналогично выявляется искажение информации, вызванное помехой между 11-ми 12-м разрядами (фиг.З ) и в других разрядах. Таким образом, при отсутствии искажений информация считывается с регистра 5, а в регистр 6 блокируется нулем на первом входе элемента И 9.

Работа блока 1 выделения синхроимпульсов (фиг.4) заключается в обнулении делителя 17 частоты по истечении 3 мкс (время первых трех битов, отведенных под синхронизацию).

Погрешность установки фазы равна периоду собственной частоты генератора 14.

Блок 1 формирует также сигнал для установки регистров 5 и 6 в исходное состояние после выделения синхропосле довательности и сигнал стробирования блоков 7 и 8 контроля, который формируется после прихода последнего информационного разряда.

Формула изобретения

Устройство для декодирования фазо- манипулировснного кода, содержащее первый, второй регисты, триггер, элемент И, первый и второй элементы НЕ, вход первого элемента НЕ является входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены первый, второй блоки контроля четности, первый, второй блоки ключей и блок выделения синхроимпульсов, вход которого объединен с информационным входом первого регистра и подключен к входу устройства, первый, второй и третий выходы блока выделения синхроимпульсов соединены соответственно с управляющими входами первого, второго блоков контроля четности, счетным входом триггера и установочными входами первого, второго регистров и триггера, прямой и инверсный выходы триггера соединены с тактовыми входами соответ ственно первого и второго регистров,

/ / 0 f О О О 1 1 4

ж )

фиг. 2

10

15

70

выходы первого регистра соединены с одноименными информационными входами первого блока ключей и первого блока контроля четности, выход которого соединен непосредственно с управляющим входом первого блока ключей и через второй элемент НЕ с первым входом элемента И, выход которого соединен с управляющим входом второго блока ключей, выход первого элемента НЕ соединен с информационным входом второго регистра, выходы которого соединены с одноименными информационными входами второго блока ключей и второго блока контроля четности, выход которого соединен с вторым входом элемента К, выходы первого и второго блоков ключей соответственно объединены и являются выходами устройства.

(

1 1 0 1 0 Q 0 1 1

i

I

TJTJT-TLruriJ-lJ-Lr

г Ыйц-л ц-титигу

.

if

/7

Фиг.Ъ

Составитель М.Никуленков Редактор Н.Лазаренко Техред Л.Олийнык Корректор С.Черни

Заказ 622Тираж 454Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35 Раушская наб., д. 4/5

фие b

| Автоматика и вычислительная техника, 1989, 2, с.55-63 | |||

| Декодер | 1987 |

|

SU1474852A1 |

Авторы

Даты

1991-03-07—Публикация

1989-04-04—Подача