1

(21)4674715/24

(22)07.04.89

(46) 15.03.91. Бюл. № 10 (72) Е.Я. Ваврук, A.M. Бисык и С.Я. Нерепичка

(53)681.325(088.8)

(56)Авторское свидетельство СССР W 1283754, кл. G 06 F 7/544, 1985.

Авторское свидетельство СССР 1509879, по заявке № 4383839, кл. G 06 F 7/544, 1988.

(54)УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПРОИЗВЕДЕНИЙ

(57)Изобретение относится к вычислительной технике и может быть использовано з арифметических устройствах

цифровых вычислительных машин. Цель изобретения - расширение функциональных возможностей за счет организации режима последовательного приема и выполнения операции над несколькими суммами произведений чисел. Это достигается тем, что в устройство, содержащее блоки промежуточных вычислений, многовходояый сумматор 8, регистр 9 коэффициента, группу элементов НЕ 11, мультиплексор 12, регистр 10 результата, причем каждый блок 1 промежуточных вычислений содержит два регистра 2 и 3, сумматор 5, мультиплексор 6, группу элементов 4 запрета квадратор 7, введены вычислительный узел 10 и буферный регистр 13 с соответствующими связями. 2 ил.

с

Ј

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1988 |

|

SU1509879A1 |

| Устройство для вычисления суммы произведений | 1985 |

|

SU1283754A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Устройство для вычисления преобразования Фурье-Галуа и свертки | 1985 |

|

SU1295415A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для деления | 1990 |

|

SU1711149A1 |

| Микропроцессор | 1985 |

|

SU1273939A1 |

| Устройство для вычисления квадратного корня из суммы квадратов чисел | 1985 |

|

SU1285466A1 |

| Устройство для умножения матриц | 1991 |

|

SU1807499A1 |

| Арифметико-логическое устройство | 1988 |

|

SU1599853A1 |

18

-,

10

24-

15

14

П

Ъ;

О

со ел

vl

1

Изобретение относится к вычислительной технике и может быть использо ванов арифметических устройствах цифровых вычислительных машин.

Цель изобретения - расширение функциональных возможностей устройства за счет организации режима последовательного приема и выполнения операций над несколькими суммами произведений чисел.

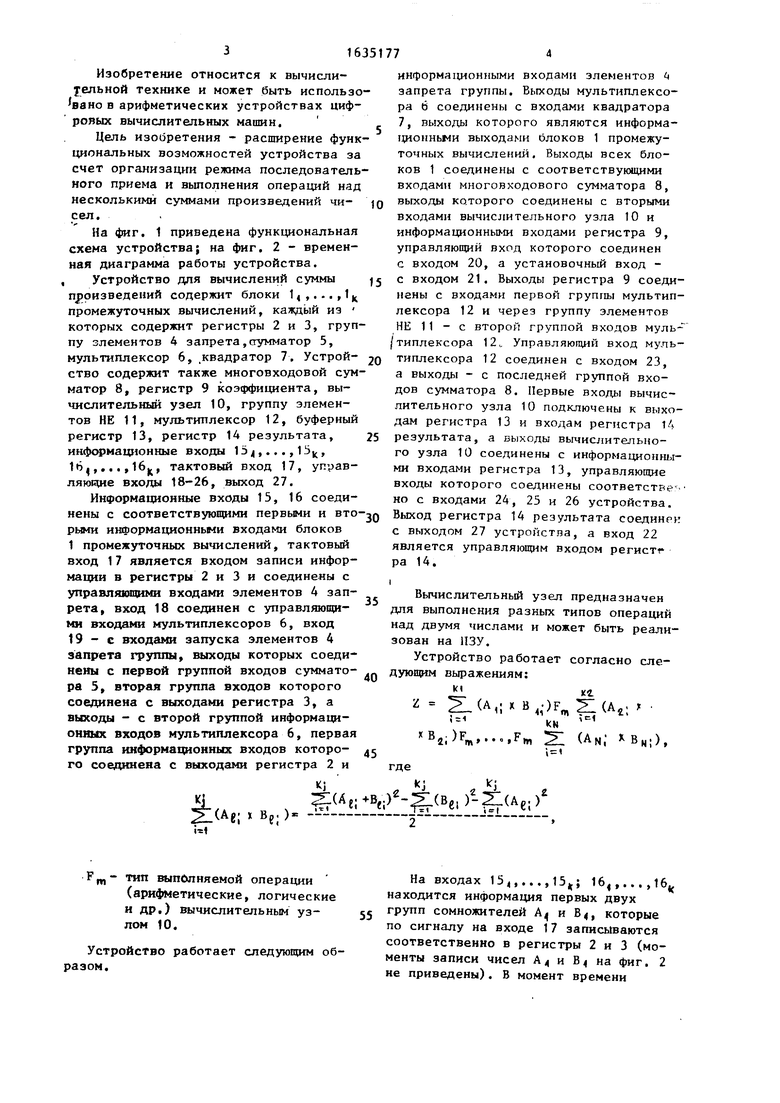

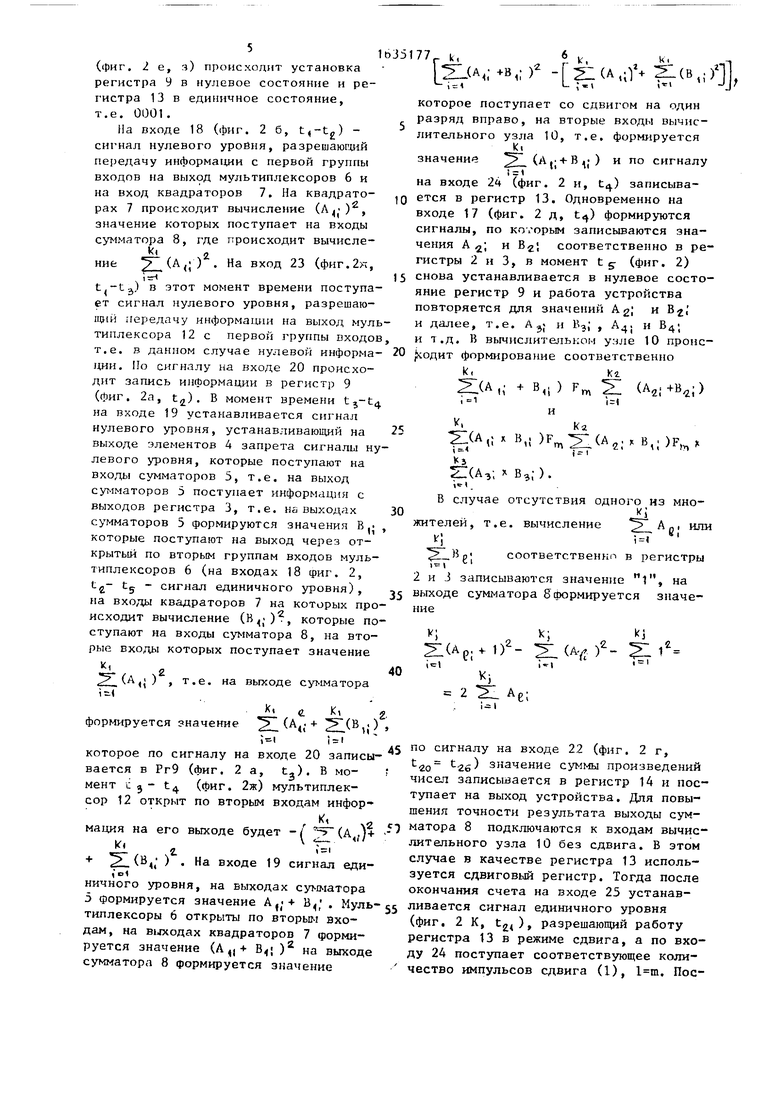

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временная диаграмма работы устройства. , Устройство для вычислений суммы произведений содержит блоки 14 ,. .. , 1 к промежуточных вычислений, каждый из которых содержит регистры 2 и 3, группу элементов 4 запрета,сумматор 5, мультиплексор 6, .квадратор 7. Устройство содержит также многовходовой сумматор 8, регистр 9 коэффициента, вычислительный узел 10, группу элементов НЕ 11, мультиплексор 12, буферный регистр 13, регистр 14 результата, информационные входы 15,...,15, 16,,...,l6fc, тактовый вход 17, управляющие входы 18-26, выход 27.

Информационные входы 15, 16 соединены с соответствующими первыми и вторыми информационными входами блоков 1 промежуточных вычислений, тактовый вход 17 является входом записи информации в регистры 2 и 3 и соединены с управляющими входами элементов 4 запрета, вход 18 соединен с управляющими входами мультиплексоров 6, вход 19 - с входами запуска элементов 4 запрета группы, выходы которых соединены с первой группой входов сумматора 5, вторая группа входов которого соединена с выходами регистра 3, а выходы - с второй группой информационных входов мультиплексора 6, первая группа информационных входов которого соединена с выходами регистра 2 и

KL i(Ae; .

i-1

Fm- тип выполняемой операции

(арифметические, логические и др.) вычислительным узлом 10.

Устройство работает следующим образом.

информационными входами элементов запрета группы. Выходы мультиплексора 6 соединены с входами квадратора 7, выходы которого являются информационными выходами блоков 1 промежуточных вычислений. Выходы всех блоков 1 соединены с соответствующими входами многовходового сумматора 8,

Q выходы которого соединены с вторыми входами вычислительного узла 10 и информационными входами регистра 9, управляющий вход которого соединен с входом 20, а установочный вход 5 с входом 21. Выходы регистра 9 соединены с входами первой группы мультиплексора 12 и через группу элементов НЕ 11 - с второй группой входов нуль- /типлексора 12„ Управляюгций вход муль0 типлексора 12 соединен с входом 23, а выходы - с последней группой входов сумматора 8. Первые входы вычислительного узла 10 подключены к выходам регистра 13 и входам регистра 14

5 результата, а выходы вычислительного узла 10 соединены с информационными входами регистра 13, управляющие входы которого соединены соответствен но с входами 24, 25 и 26 устройства.

0 Выход регистра 14 результата соединен с выходом 27 устройства, а вход 22 является управляющим входом регистг ра 14.

Вычислительньй узел предназначен

для выполнения разных типов операций над двумя числами и может быть реализован на ПЗУ.

Устройство работает согласно сле- ДУЮЩИМ выражениям:

Z Z-(A,;«B4.)FmЈ(At;

«N М

. 51 (AN; хв„;),

где

вг;)2-(ве1)2-2:(Ае;){ .

На входах 15,..., 16,16

находится информация первых двух групп сомножителей А и 84, которые по сигналу на входе 17 записываются соответственно в регистры 2 и 3 (моменты записи чисел А„ и В на фиг. 2 не приведены). В момент времени

ib.m// k,e , k,. -.

(фиг. 2 e, з) происходит установка - I EL.( +B,; Г - 2 (A ,;) + 5()J регистра 9 в нулевое состояние и ре- - ; Г ;- J

регистра 9 в нулевое состояние и регистра 13 в единичное состояние, т.е. 0001.

На входе 18 (фиг. 2 б, t,-tg) - сигнал нулевого уровня, разрешаквдий передачу информации с первой группы входов на выход мультиплексоров 6 и на вход квадраторов 7. На квадраторах 7 происходит вычисление (Л(-) , значение которых поступает на входы сумматора 8, где происходит вычислеk 2 ние 2L() На вход 23 (Фиг 2л1

которое поступает со сдвигом на один разряд вправо, на вторые входы вычислительного узла 10, т.е. формируется

10

15

Ki

значение

(А.- + В.;) и по сигналу

«

на входе 24 (фиг. 2 и, t) записывается в регистр 13. Одновременно на входе 17 (фиг. 2 д, t) формируются сигналы, по когорым записываются значения А 2; и , соответственно в регистры 2 и 3, в момент t 5- (фиг. 2) снова устанавливается в нулевое состояние регистр 9 и работа устройства повторяется для значений Ag, и и далее, т.е. А 3; и В3; , A4i и Ъ и т.д. В вычислительном узле 10 проис- Јсодит формирование соответственно

trtB)

в этот момент времени поступает сигнал нулевого уровня, разрешающий передачу информации на выход мультиплексора 12 с первой группы входов, т.е. в данном случае нулевой информа- ции. По сигналу на входе 20 происходит запись информации в регистр 9 (фиг. 2а, tg) . В момент времени на входе 19 устанавливается сигнал нулевого уровня, устанавливающий на выходе элементов 4 запрета сигналы нулевого уровня, которые поступают на входы сумматоров 5, т.е. на выход сумматоров 5 поступает информация с выходов регистра 3, т.е. невыходах сумматоров 5 формируются значения В , , которые поступают на выход через открытый по вторым группам входов мультиплексоров 6 (на входах 18 фиг. 2, t-g- t5 - сигнал единичного уровня) , на входы квадраторов 7 на которых происходит вычисление (), которые поступают на входы сумматора 8, на вторые входы которых поступает значение

„

(А

i.

)Z,

формируется значение

т.е. на выходе сумматора

К,

-А. ,j,

ю

ч. Ki f

А41.+ ,{

которое по сигналу на входе 20 записывается в Рг9 (фиг. 2 a, t-). В мо- мент з С4 СФИГ« 2ж) мультиплексор 12 открыт по вторым входам инфорI/

нация на его выходе будет -/ (А,)+

( ) . На входе 19 сигнал единичного уровня, на выходах сумматора 5 формируется значение А(--«- . Муль-е5 тиллексоры 6 открыты по вторым входам, на выходах квадраторов 7 формируется значение (А ( + В,,; )2 на выходе сумматора 8 формируется значение

которое поступает со сдвигом на один разряд вправо, на вторые входы вычислительного узла 10, т.е. формируется

Ki

значение

(А.- + В.;) и по сигналу

«

на входе 24 (фиг. 2 и, t) записывается в регистр 13. Одновременно на входе 17 (фиг. 2 д, t) формируются сигналы, по когорым записываются значения А 2; и , соответственно в регистры 2 и 3, в момент t 5- (фиг. 2) снова устанавливается в нулевое состояние регистр 9 и работа устройства повторяется для значений Ag, и и далее, т.е. А 3; и В3; , A4i и Ъ и т.д. В вычислительном узле 10 проис- Јсодит формирование соответственно

k,

SA,- + В,, ) Fm (A2j+Buj)

V.Ka

B«i ,

fi

ZT(A3; B3;).

icl.

В случае отсутствия одного из

т.е. вычисление

с;

или

el

соответственно в регистры

2 и 3 записываются значение 1, на выходе сумматора 8формируется значение

v;k; kj

21 (Ае; О2- 21 (А-/, )2- 11г

|С 1«1

2

Le;

по сигналу на входе 22 (фиг. 2 г, t2o t26) значение суммы произведений чисел записывается в регистр 14 и поступает на выход устройства. Для повышения точности результата выходы сумматора 8 подключаются к входам вычислительного узла 10 без сдвига. В этом случае в качестве регистра 13 используется сдвиговый регистр. Тогда после окончания счета на входе 25 устанавливается сигнал единичного уровня (фиг. 2 К, t24)у разрешающий работу регистра 13 в режиме сдвига, а по входу 24 поступает соответствующее количество импульсов сдвига (1), . После сдвига по сигналу (фиг. 2г, tjg) по входу 22 значение суммы записывается в регистр 14.

Формула изобретения

Устройство для вычисления сумм произведении, содержащее группу бло- ьов промежуточных вычислений, много- в .одетый сумматор, регистр коэффициента, группу элегентов НЕ, мультиплексор, регистр результата, причем

:ж,„ын блок промежуточных вычислений содержит два регистра, сумматор, муль т-пшексор, группу элементов запрета, . шратор, при этом в каждом блоке г. омежуточных вычислений вхоцы квад- Р-чтора соединены с выходами мультип- пэксора, первая группа информацией- tu входов которого соединена с выходами первого регистра и информацион- нымь входами элементов запрета группы jj. ая группа информационных входов tтиплексора соединена с выходами умматора, первая группа входов кото- JFO соединена с выходами элементов i-фета грунт 1, вторая группа вхо- ,i ;в - с выходами второго регистра, информационные входы первого и второ- го регистров являются информационными входами данного блока промежуточных начислений и соединены с соответствующий информационными входами устройства, входы управления блоков промежуточных вычислений соединены с соответствующими входами управления устройства и соединены с управляющими входами мультиплексоров, регистров и

1 цементов запрета группы соответствул/дих блоков промежуточных вычислении,

JQ

0 5 JQ

0

5

выходы квадраторов блоков промежутти- ных вычислении являются их выходами и соединены с соответствующими группами входов многовходового сумматора, выходы которого соединены с информационными входами регистра коэффициента, управляющий вход которого соединен с соответствующим управляющим входом устройства, а выходы - с первой группой входов мультиплексора и через элементы НЕ группы - с второй группой входов мультиплексора, управляющий вход которого соединен с соответствующим управляющим входом устройства, а выходы - с последней группой входов многовходового сумматора, управляющий вход регистра результата соединен с соответствующим управляющим входом устройства, а выходы являются выходами устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет организации режима последовательного приема и выполнения операции над несколькими суммами произведений чисел, в него введены вычислительный узел и буферный регистр, выходы которого соединены с информационными вхе дами регистра результата и первыми входами вычислительного узла, вторые входы которого соединены с выходами многовходового сумматора, а выходы - с информационными входами регистра, управляющие входы которого соединены с соответствующими управляющими входами устройства, установочный вход регистра коэффициента соединен с соответствующим управляющим входом устройства.

Авторы

Даты

1991-03-15—Публикация

1989-04-07—Подача