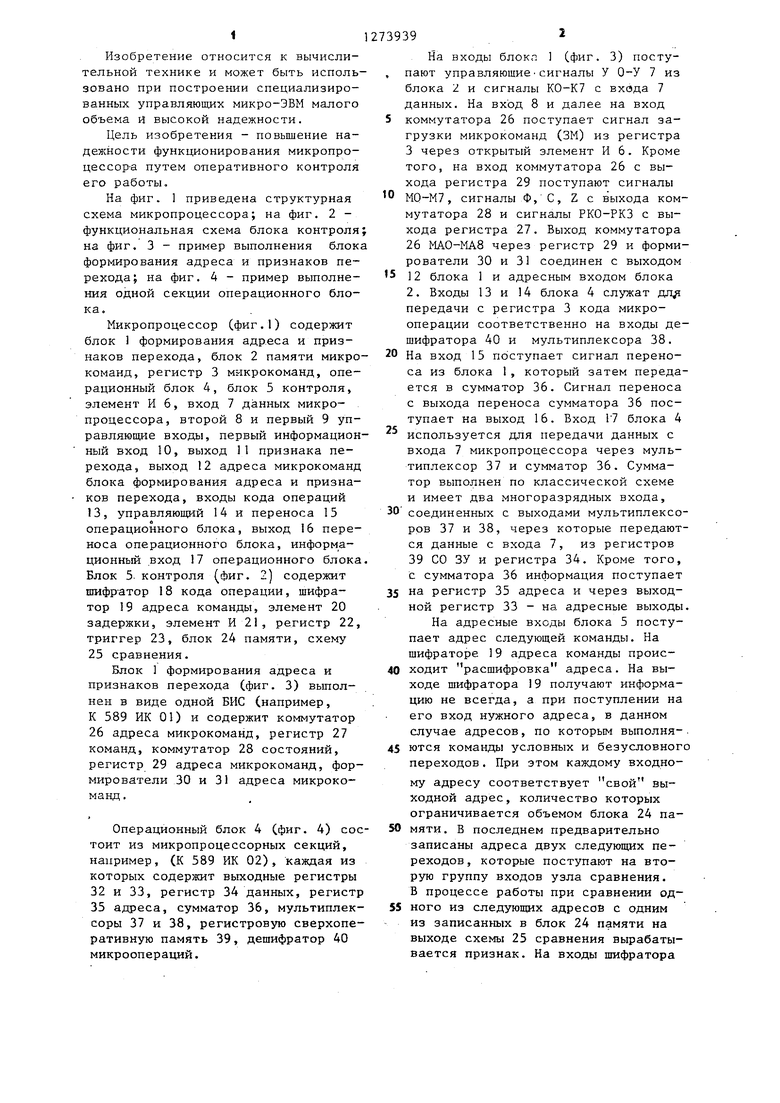

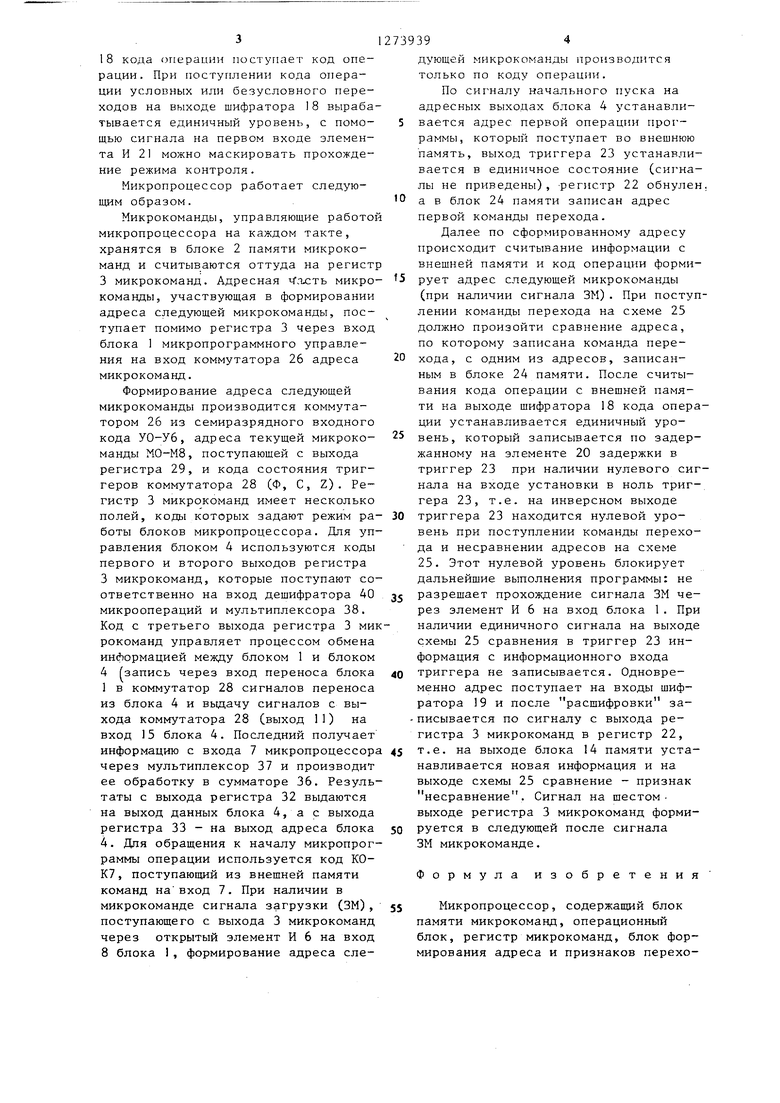

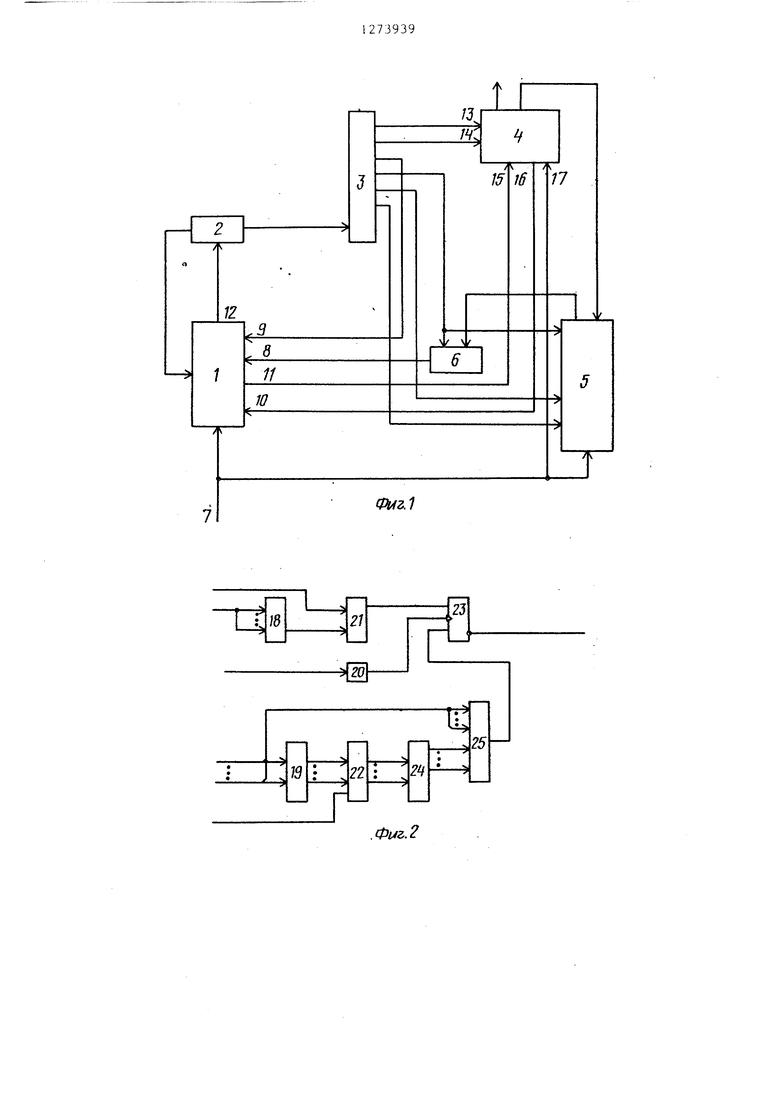

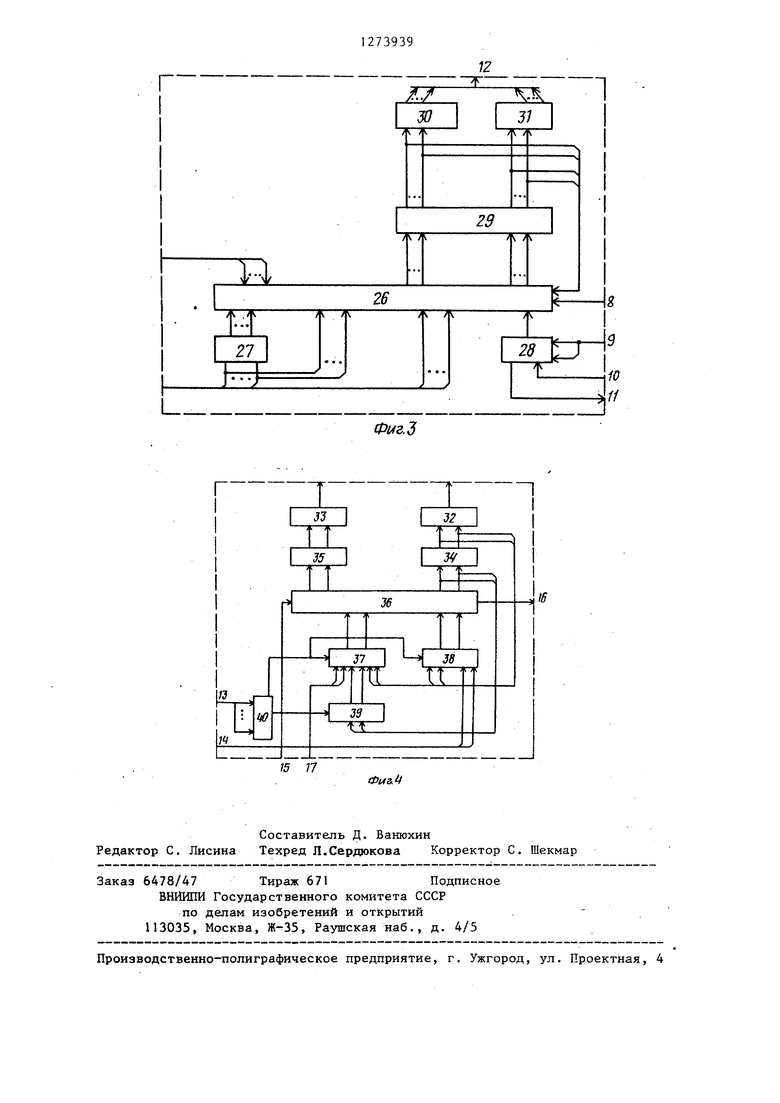

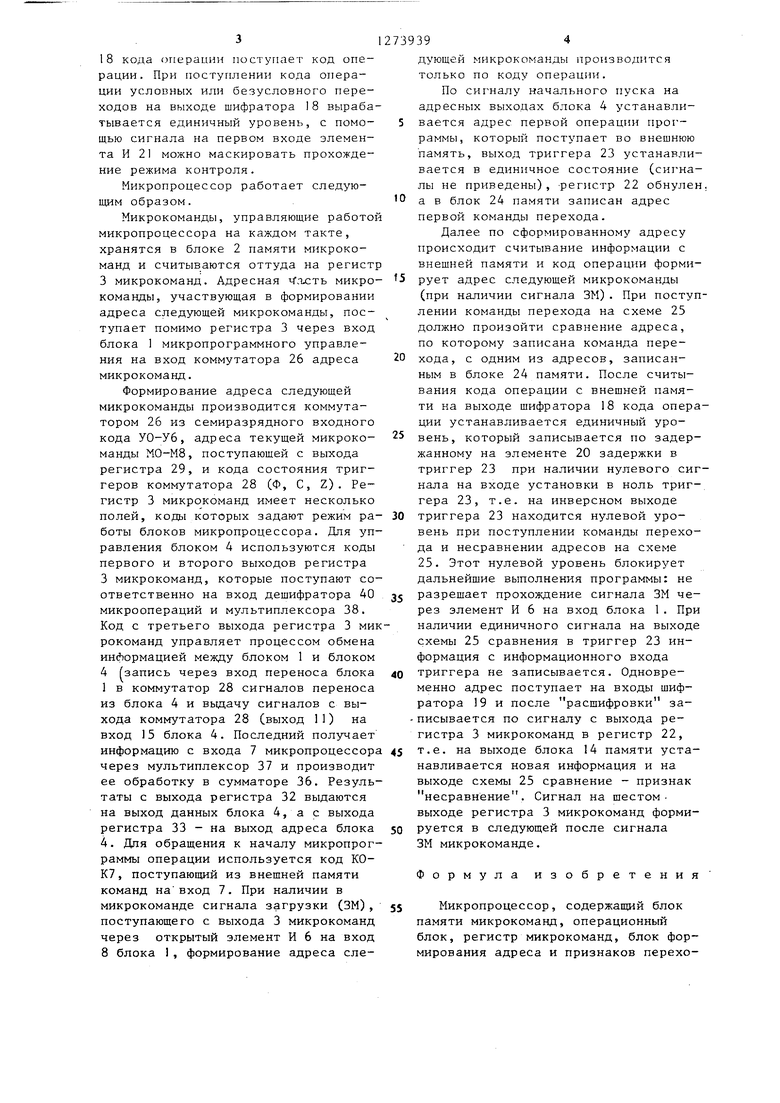

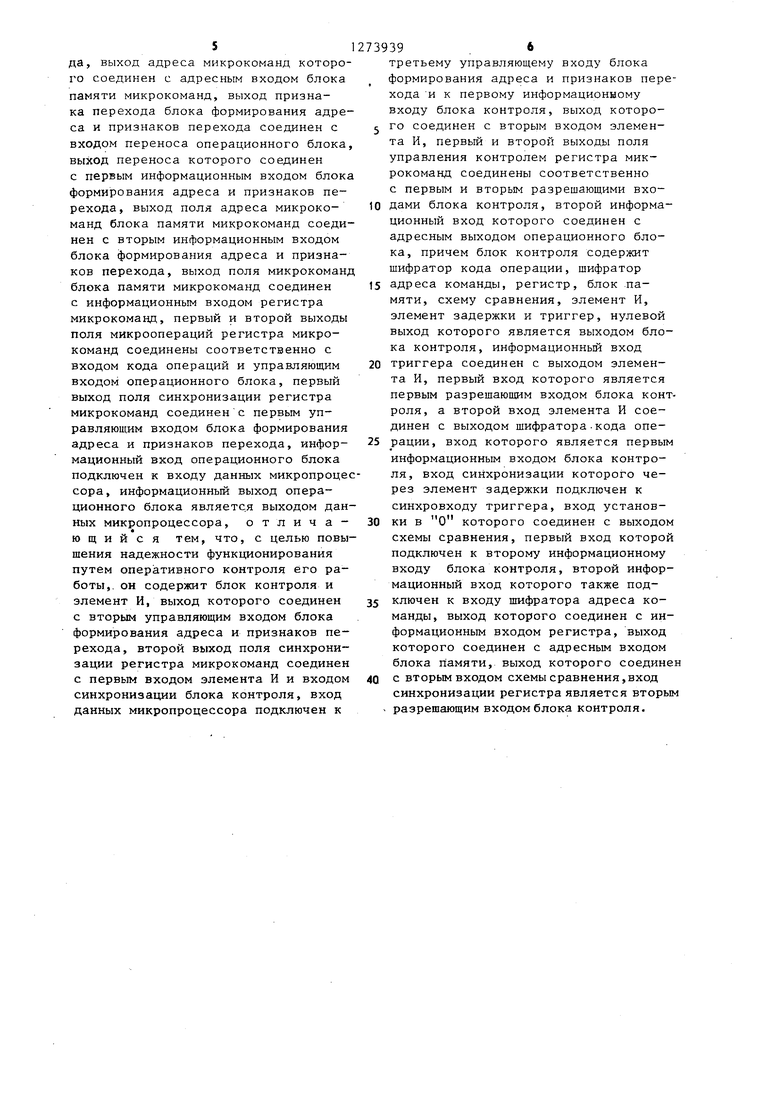

1 Изобретение относится к вычислительной технике и может быть исполь зовано при построении специализированных управляющих микро-ЭВМ малого объема и высокой надежности. Цель изобретения - повышение надежности функционирования микропроцессор-а путем оперативного контроля его работы. На фиг. 1 приведена структурная схема микропроцессора; на фиг. 2 функциональная схема блока контроля на фиг. 3 - пример выполнения блок формирования адреса и признаков перехода; на фиг. 4 - пример выполнения одной секции операционного блока. Микропроцессор (фиг.1) содержит блок 1 формирования адреса и признаков перехода, блок 2 памяти микро команд, регистр 3 микрокоманд, операционный блок 4, блок 5 контроля, элемент И 6, вход 7 данных микропроцессора, второй 8 и первый 9 управляющие входы, первый информацион ный вход 10, выход 11 признака перехода, выход 12 адреса микрокоманд блока формирования адреса и признаков перехода, входы кода операций 13, управляющий 14 и переноса 15 операционного блока, выход 16 переноса операционного блока, информационный вход 17 операционного блока Блок 5. контроля (фиг. 2) содержит шифр-атор 18 кода операции, шифратор 19 адреса команды, элемент 20 задержки, элемент И 21, регистр 22, триггер 23, блок 24 памяти, схему 25сравнения. Блок 1 формирования адреса и признаков перехода (фиг. 3) выполнен в виде одной БИС (например, К 589 ИК 01) и содержит коммутатор 26адреса микрокоманд, регистр 27 команд, коммутатор 28 состояний, регистр 29 адреса микрокоманд, формирователи 30 и 31 адреса микрокоманд , Операционный блок 4 (фиг. 4) сос тоит из микропроцессорных секций, например, (К 589 ИК 02), каждая из которых содержит выходные регистры 32 и 33, регистр 34 данных, регистр 35 адреса, сумматор 36, мультиплек соры 37 и 38, регистровую сверхопе ративную память 39, дешифратор 40 микроопераций. 9i На входы блокп 1 (фиг. 3) поступают управляющиесигналы У 0-У 7 из блока 2 и сигналы КО-К7 с входа 7 данных. На вход 8 и далее на вход коммутатора 26 поступает сигнал загрузки микрокоманд (ЗМ) из регистра 3 через открытый элемент И 6. Кроме того, на вход коммутатора 26 с выхода регистра 29 поступают сигналы МО-М7, сигналы Ф,С, Z с выхода коммутатора 28 и сигналы РКО-РКЗ с выхода регистра 27. Выход коммутатора 26 МАО-МАЗ через регистр 29 и формирователи 30 и 31 соединен с выходом 12 блока 1 и адресным входом блока 2. Входы 13 и 14 блока 4 служат дл; передачи с регистра 3 кода микрооперации соответственно на входы дешифратора 40 и мультиплексора 38. На вход 15 поступает сигнал переноса из блока 1, который затем передается в сумматор 36. Сигнал переноса с выхода переноса сумматора 36 поступает на выход 16. Вход 7 блока 4 используется для передачи данных с входа 7 микропроцессора через мультиплексор 37 и сумматор 36. Сумматор выполнен по классической схеме и имеет два многоразрядных входа, соединенных с выходами мультиплексоров 37 и 38, через которые передаются данные с входа 7, из регистров 39 СО ЗУ и регистра 34. Кроме того, с сумматора 36 информация поступает на регистр 35 адреса и через выходной регистр 33 - на адресные выходы. На адресные входы блока 5 поступает адрес следующей команды. На шифраторе 19 адреса команды происходит расшифровка адреса. На выходе шифратора 19 получают информацию не всегда, а при поступлении на его вход нужного адреса, в данном случае адресов, по которым выполня-. ются команды условных и безусловного переходов. При этом каждому входному адресу соответствует свой выходной адрес, количество которых ограничивается объемом блока 24 памяти. В последнем предварительно записаны адреса двух следующих переходов, которые поступают на вторую группу входов узла сравнения. В процессе работы при сравнении од- ного из следующих адресов с одним из записанных в блок 24 памяти на выходе схемы 25 сравнения вырабатывается признак. На входы шифратора

18 кода операции поступает код операции. При поступлении кода операции условных или безусловного переходов на выходе шифратора 18 вырабатывается единичный уровень, с помощью сигнала на первом входе элемента И 2 1 можно маскировать прохождение режима контроля.

Микропроцессор работает следующим образом.

Микрокоманды, управляющие работой микропроцессора на каждом такте, хранятся в блоке 2 памяти микрокоманд и считываются оттуда на регистр 3 микрокоманд. Адресная Ч-гсть микрокоманды, участвующая в формировании адреса следующей микрокоманды, поступает помимо регистра 3 через вход блока 1 микропрограммного управления на вход коммутатора 26 адреса микрокоманд.

Формирование адреса следующей микрокоманды производится коммутатором 26 из семиразрядного входного кода УО-У6, адреса текущей микрокоманды МО-М8, поступающей с выхода регистра 29, и кода состояния триггеров коммутатора 28 (Ф, С, Z). Регистр 3 микрокоманд имеет несколько полей, коды которых задают режим работы блоков микропроцессора. Для управления блоком 4 используются коды первого и второго выходов регистра

3микрокоманд, которые поступают соответственно на вход дешифратора 40 микроопераций и мультиплексора 38. Код с третьего выхода регистра 3 микрокоманд управляет продессом обмена информацией между блоком 1 и блоком

4(запись через вход переноса блока 1 в коммутатор 28 сигналов переноса из блока 4 и выдачу сигналов с выхода коммутатора 28 (выход 11) на вход 15 блока 4. Последний получает информацию с входа 7 микропроцессора через мультиплексор 37 и производит ее обработку в сумматоре 36. Результаты с выхода регистра 32 выдаются на выход данных блока 4, а с выхода регистра 33 - на выход адреса блока 4. Для обращения к началу микропрограммы операции используется код КОК7, поступающий из внещней памяти команд навход 7. При наличии в микрокоманде сигнала загрузки (ЗМ), поступающего с выхода 3 микрокоманд через открытый элемент И 6 на вход 8 блока 1, формирование адреса следующей микрокоманды производится только по коду операции.

По сигналу начального пуска на адреснь х выходах блока 4 устанавливается адрес первой операции программы, который поступает во внешнюю память, выход триггера 23 устанавливается в единичное состояние (сигналы не приведены), -регистр 22 обнулен.

а в блок 24 памяти записан адрес первой команды перехода.

Далее по сформированному адресу происходит считывание информации с внешней памяти и код операции формирует адрес следующей микрокоманды

(при наличии сигнала ЗМ). При поступлении команды перехода на схеме 25 должно произойти сравнение адреса, по которому записана команда перехода, с одним из адресов, записанным в блоке 24 памяти. После считывания кода операции с внешней памяти на выходе шифратора 18 кода операции устанавливается единичный уровень, который записывается по задержанному на элементе 20 задержки в триггер 23 при наличии нулевого сигнала на входе установки в ноль триггера 23, т.е. на инверсном выходе

триггера 23 находится нулевой уровень при поступлении команды перехода и несравнении адресов на схеме 25. Этот нулевой уровень блокирует дальнейшие выполнения программы: не

разрешает прохождение сигнала ЗМ через элемент И 6 на вход блока 1. При наличии единичного сигнала на выходе схемы 25 сравнения в триггер 23 информация с информационного входа

триггера не записывается. Одновременно адрес поступает на входы шифратора 19 и после расшифровки записывается по сигналу с выхода регистра 3 микрокоманд в регистр 22,

т.е. на выходе блока 14 памяти устанавливается новая информация и на выходе схемы 25 сравнение - признак несравнение. Сигнал на шестомвыходе регистра 3 микрокоманд формируется в следующей после сигнала ЗМ микрокоманде.

Формула изобретения

Микропроцессор, содержащий блок памяти микрокоманд, операционный блок, регистр микрокоманд, блок формирования адреса и признаков перехо5

да, выход адреса микрокоманд которого соединен с адресным входом блока памяти микрокоманд, выход признака перехода блока формирования адреса и признаков перехода соединен с входом переноса операционного блока выход переноса которого соединен с первым информационным входом блока формирования адреса и признаков перехода, выход поля адреса микрокоманд блока памяти микрокоманд соединен с вторым информационным входом блока формирования адреса и признаков перехода, выход поля микрокоманд блока памяти микрокоманд соединен с информационным входом регистра микрокоманд, первый и второй выходы поля микроопераций регистра микрокоманд соединены соответственно с входом кода операций и управляющим входом операционного блока, первый выход поля синхронизации регистра микрокоманд соединенс первым управляющим входом блока формирования адреса и признаков перехода, информационный вход операционного блока подключен к входу данных микропроце сора, информационный выход операционного блока является выходом данных микропроцессора, о т л и ч а

ю щ и и с я тем, что, с целью повышения надежности функционирования путем оперативного контроля его работы,, он содержит блок контроля и элемент И, выход которого соединен с вторым управляющим входом блока формирования адреса и признаков перехода, второй выход поля синхронизации регистра микрокоманд соединен с первым входом элемента И и входом синхронизации блока контроля, вход данных микропроцессора подключен к

73939 . 6

третьему управляющему входу блока формирования адреса и признаков перехода И к первому информационному входу блока контроля, выход которо го соединен с вторым входом элемента И, первый и второй выходы поля управления контролем регистра микрокоманд соединены соответственно с первым и вторым разрешающими вхо10 дами блока контроля, второй информационный вход которого соединен с адресным выходом операционного блока, причем блок контроля содержит шифратор кода операции, шифратор

)5 адреса команды, регистр, блок .памяти, схему сравнения, элемент И, элемент задержки и триггер, нулевой выход которого является выходом блока контроля, информационньй вход

20 триггера соединен с выходом элемента И, первый вход которого является первым разрешающим входом блока контроля, а второй вход элемента И соединен с выходом шифратора-кода опе25 рации, вход которого является первым информационным входом блока контроля, вход синхронизации которого через элемент задержки подключен к синхровходу триггера, вход установ30 ки в О которого соединен с выходом схемы сравнения, первый вход которой подключен к второму информационному входу блока контроля, второй информационный вход которого также под35 ключей к входу шифратора адреса команды, выход которого соединен с информационным входом регистра, выход которого соединен с адресным входом блока памяти, выход которого соединен

40 с вторым входом схемы сравнения,вход

синхронизации регистра является вторым разрешающим входом блока контроля.

8

11

Ю

г

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1985 |

|

SU1280378A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропроцессор | 1985 |

|

SU1290340A1 |

| Микропроцессор | 1982 |

|

SU1037263A1 |

| Микропроцессор | 1981 |

|

SU1012266A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении специализированных управляющих микро-ЭВМ малого объема и высокой надежности. Цель изобретения - повьшение надежности функционирования микропроцессора за счет оперативного контроля его работы. Микропроцессор содержит, блок формирования адреса и признаков перехода, блок памяти микрокоманд, регистр микрокоманд, операционный блок, блок контроля и злемент И. 4 ил.

ш

-I

.Фиг.

Г

12

х:

zz

Фиг.

| Каган Б.М., Сташин В.В | |||

| Микро.процессоры в цифровых системах | |||

| М.: Энергия, 1979 | |||

| Микропроцессор | 1981 |

|

SU1012266A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-06-26—Подача