СЛ С

СП

О

со

00

QD

Фие.1

Изобретение относится к вычислительной технике и может быть исполь- зовано в качестве сопроцессора в цифровых вычислительных системах, производящих обработку акустических, сейс- моразведочных и других сигналов.

Цель изобретения - уменьшение аппаратных затрат.

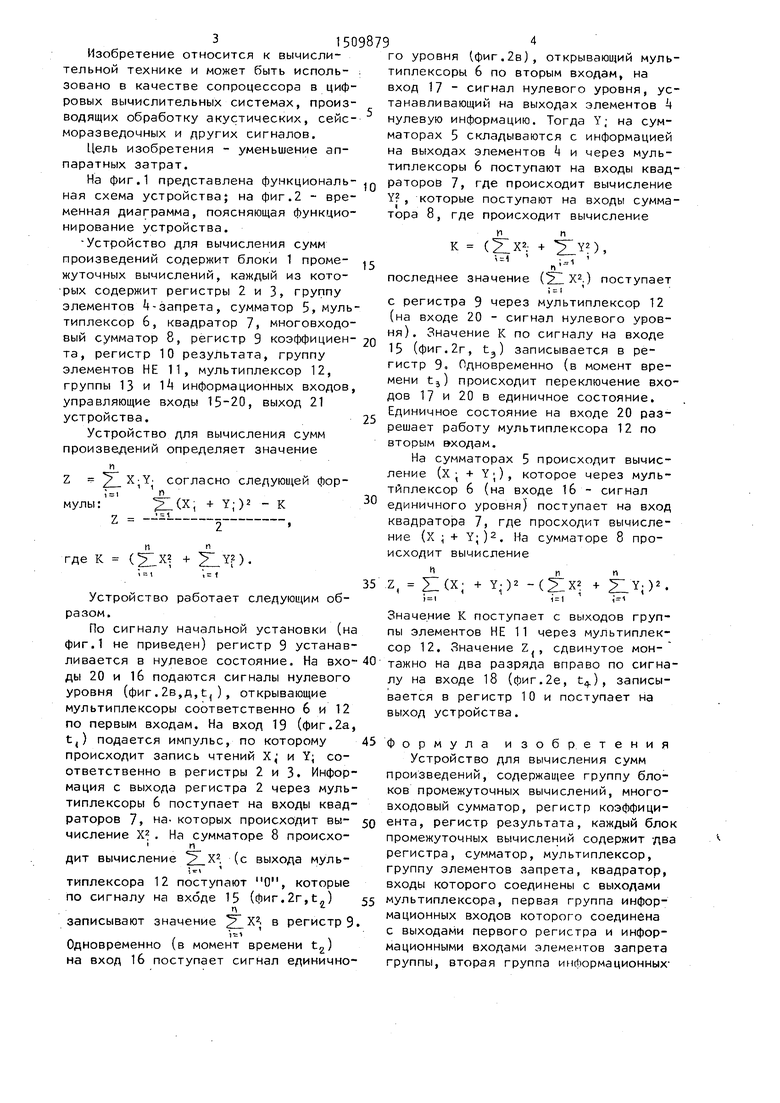

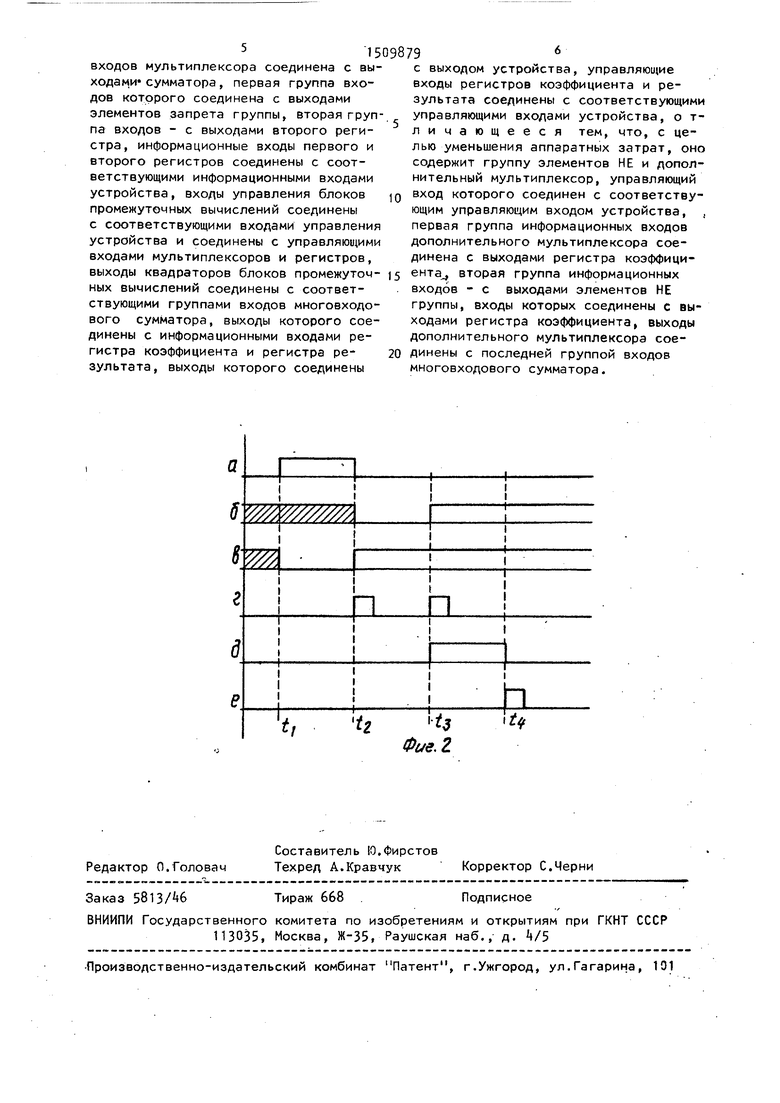

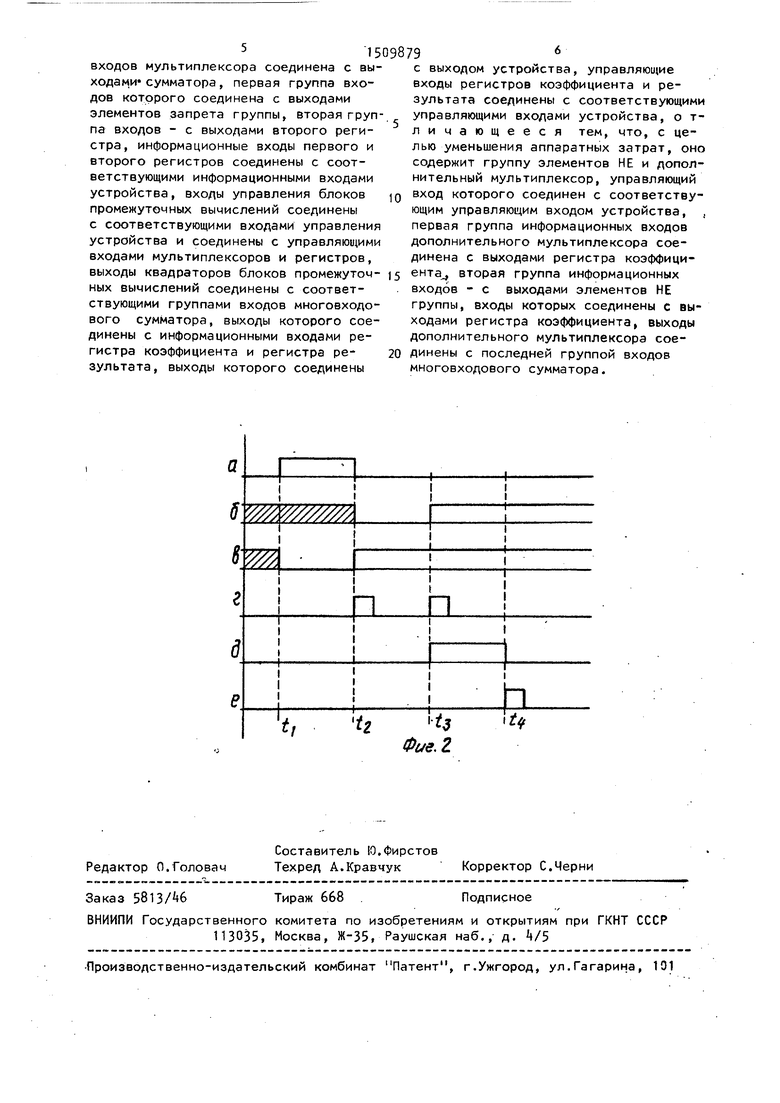

На фиг.1 представлена функциональная схема устройства; на фиг.2 - временная диаграмма, поясняющая функционирование устройства.

Устройство для вычисления сумм произведений содержит блоки 1 промежуточных вычислений, каждый из кото- рых содержит регистры 2 и 3, группу элементов -запрета, сумматор 5, мультиплексор 6, квадратор 7, многовходо- вый сумматор 8, регистр 9 коэффициен- та, регистр 10 результата, группу элементов НЕ 11, мультиплексор 12, группы 13 и lA информационных входов управляющие входы 15-20, выход 21 устройства.

Устройство для вычисления сумм произведений определяет значение

п

Z - согласно следующей формулы: (Х, + Y;)2 - К

Of

где К (Х + 21 Yf).

Устройство работает следующим образом.

По сигналу начальной установки (на фиг.1 не приведен) регистр 9 устанавливается в нулевое состояние. На вхо-40 тажно на два разряда вправо по сигна- ды 20 и 16 подаются сигналы нулевого лу на входе 18 (фиг.2е, t), записы- уровня (фиг.2в,д,t,

Z, ЦСХ; + Y.)2 -(Х + ilY;)2.

Значение К поступает с выходов группы элементов НЕ 11 через мультиплексор 12, Значение Z., сдвинутое мон, открывающие

мультиплексоры соответственно 6 и 12 по первым входам. На вход 19 (фиг.2а, t,) подается импульс, по которому 45 происходит запись чтений X, и Y; соответственно в регистры 2 и 3. Информация с выхода регистра 2 через мультиплексоры 6 поступает на входы квадраторов 7, на- которых происходит вы- зо числение Х, На сумматоре 8 происховается в регистр 10 и поступает на выход устройства.

Формула изобретения

Устройство для вычисления сумм произведений, содержащее группу блоков промежуточных вычислений, много- входовый сумматор, регистр коэффициента, регистр результата, каждый блок промежуточных вычислений содержит два регистра, сумматор, мультиплексор, группу элементов запрета, квадратор, входы которого соединены с выходами 55 мультиплексора, первая группа информационных входов которого соединена с выходами первого регистра и информационными входами элементов запрета группы, вторая группа информационныхдит вычисление Х. (с выхода мультиплексора 12 поступают О, которые

по сигналу на входе 15 (фиг,2г,t„)

ч записывают значение в регистр 9,

, , Одновременно (в момент времени tgj

на вход 16 поступает сигнал единично0

го уровня (фиг.2в), открывающий мультиплексоры 6 по вторым входам, на вход 17 - сигнал нулевого уровня, устанавливающий на выходах элементов k нулевую информацию. Тогда Y; на сумматорах 5 складываются с информацией на выходах элементов k и через мультиплексоры 6 поступают на входы квадраторов 7, где происходит вычисление Y, которые поступают на входы сумматора 8, где происходит вычисление

К (Х2.- + 1

Y,

последнее значение ( Х.) поступает

с регистра 9 через мультиплексор 12 (на входе 20 - сигнал нулевого уровня). Значение К по сигналу на входе 15 (фиг.2г, tj) записывается в регистр 9. Одновременно (в момент времени

tJ

происходит переключение вхо

тажно на два разряда вправо по сигна- лу на входе 18 (фиг.2е, t), записы-

дов 17 и 20 в единичное состояние. Единичное состояние на входе 20 разрешает работу мультиплексора 12 по вторым входам.

На сумматорах 5 происходит вычисление (Х ; + Y;), которое через мультиплексор 6 (на входе 1б - сигнал единичного уровня) поступает на вход квадратора 7, где просходит вычисление (Х + Y;)2. На сумматоре 8 происходит вычисление

Z, ЦСХ; + Y.)2 -(Х + ilY;)2.

Значение К поступает с выходов группы элементов НЕ 11 через мультиплексор 12, Значение Z., сдвинутое монтажно на два разряда вправо по сигн лу на входе 18 (фиг.2е, t), записы

вается в регистр 10 и поступает на выход устройства.

Формула изобретения

Устройство для вычисления сумм произведений, содержащее группу блоков промежуточных вычислений, много- входовый сумматор, регистр коэффициента, регистр результата, каждый блок промежуточных вычислений содержит два регистра, сумматор, мультиплексор, группу элементов запрета, квадратор, входы которого соединены с выходами мультиплексора, первая группа информационных входов которого соединена с выходами первого регистра и информационными входами элементов запрета группы, вторая группа информационныхвходов мультиплексора соединена с выходами сумматора, первая группа входов которого соединена с выходами элементов запрета группы, вторая группа входов - с выходами второго регистра, информационные входы первого и второго регистров соединены с соответствующими информационными входами устройства, входы управления блоков промежуточных вычислений соединены с соответствующими входами управления устройства и соединены с управляющими входами мультиплексоров и регистров,

с выходом устройства, управляющие входы регистров коэффициента и результата соединены с соответствующими управляющими входами устройства, о т- личающееся тем, что, с целью уменьшения аппаратных затрат, оно содержит группу элементов НЕ и дополнительный мультиплексор, управляющий вход которого соединен с соответствующим управляющим входом устройства, первая группа информационных входов дополнительного мультиплексора соединена с выходами регистра коэффици

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления сумм произведений | 1989 |

|

SU1635177A1 |

| Устройство для вычисления суммы произведений | 1985 |

|

SU1283754A1 |

| Устройство для вычисления значения модуля вектора | 1984 |

|

SU1236468A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для вычисления функций двух аргументов | 1986 |

|

SU1413626A1 |

| Устройство для вычисления координат | 1989 |

|

SU1635178A1 |

| Устройство для вычисления функций в модулярной системе счисления | 1985 |

|

SU1322268A1 |

Изобретение относится к вычислительной технике и может быть использовано для построения сопроцессоров цифровых вычислительных машин. Цель изобретения - уменьшение аппаратных затрат. Устройство содержит группу блоков 1 промежуточных вычислений, каждый из которых вымогает два регистра 2 и 3, группу элементов 4 запрета, мультиплексор 6 и квадратор 7, многовходовой сумматор 8, два регистра 9 и 10, группу элементов НЕ 11 и мультиплексор 12. Группа элементов НЕ 11 и мультиплексор 12 позволяют уменьшить аппаратные затраты на выполнение блоков промежуточных вычислений. 2 ил.

выходы квадраторов блоков промежуточ- 15 ента вторая группа информационных ных вычислений соединены с соответ- входов - с выходами элементов НЕ

группы, входы которых соединены с выходами регистра коэффициента, выходы дополнительного мультиплексора сое- 20 динены с последней группой входов

ствующими группами входов многовходо- вого сумматора, выходы которого соединены с информационными входами регистра коэффициента и регистра результата, выходы которого соединены

многовходового сумматора.

многовходового сумматора.

| Операционное устройство для суммирования произведений двух массивов чисел | 1976 |

|

SU788105A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Гайковерт ударного действия | 1959 |

|

SU128375A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-09-23—Публикация

1988-01-05—Подача