ё

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Преобразователь время-код | 1983 |

|

SU1087954A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство фазирования шкалы времени электронных часов | 1990 |

|

SU1746356A1 |

| Рециркуляционный измерительный преобразователь время-код | 1977 |

|

SU721796A1 |

| Цифровой измеритель длительности одиночных импульсов | 1986 |

|

SU1318986A1 |

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Вычислительное устройство для управления лучом плоской антенной решетки | 1981 |

|

SU1013967A1 |

| Измеритель временных интервалов | 1977 |

|

SU673976A1 |

| Мажоритарное декодирующее устройство | 1987 |

|

SU1471313A1 |

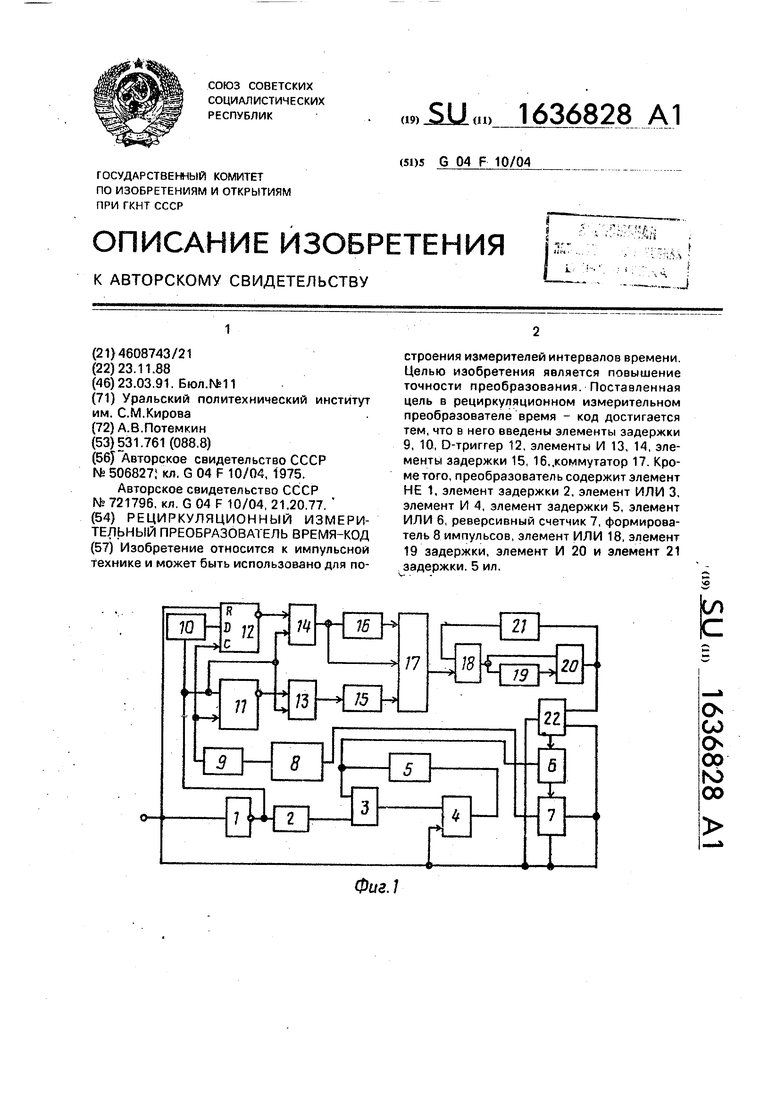

Изобретение относится к импульсной технике и может быть использовано для построения измерителей интервалов времени. Целью изобретения является повышение точности преобразования. Поставленная цель в рециркуляционном измерительном преобразователе время - код достигается тем, что в него введены элементы задержки 9, 10, D-триггер 12, элементы И 13, 14, элементы задержки 15, 16,.коммутатор 17. Кроме того, преобразователь содержит элемент НЕ 1, элемент задержки 2, элемент ИЛИ 3, элемент И 4, элемент задержки 5, элемент ИЛИ 6, реверсивный счетчик 7, формирователь 8 импульсов, элемент ИЛИ 18, элемент 19 задержки, элемент И 20 и элемент 21 задержки. 5 ил.

QS CJ

О

со

го

00

Фиг.1

Изобретение относится к импульсной технике и может быть использовано для построения измерителей .интервалов времени.

Целью изобретения является повыше- ние точности преобразования за счет устранения неоднозначности при формировании импульса ошибки.

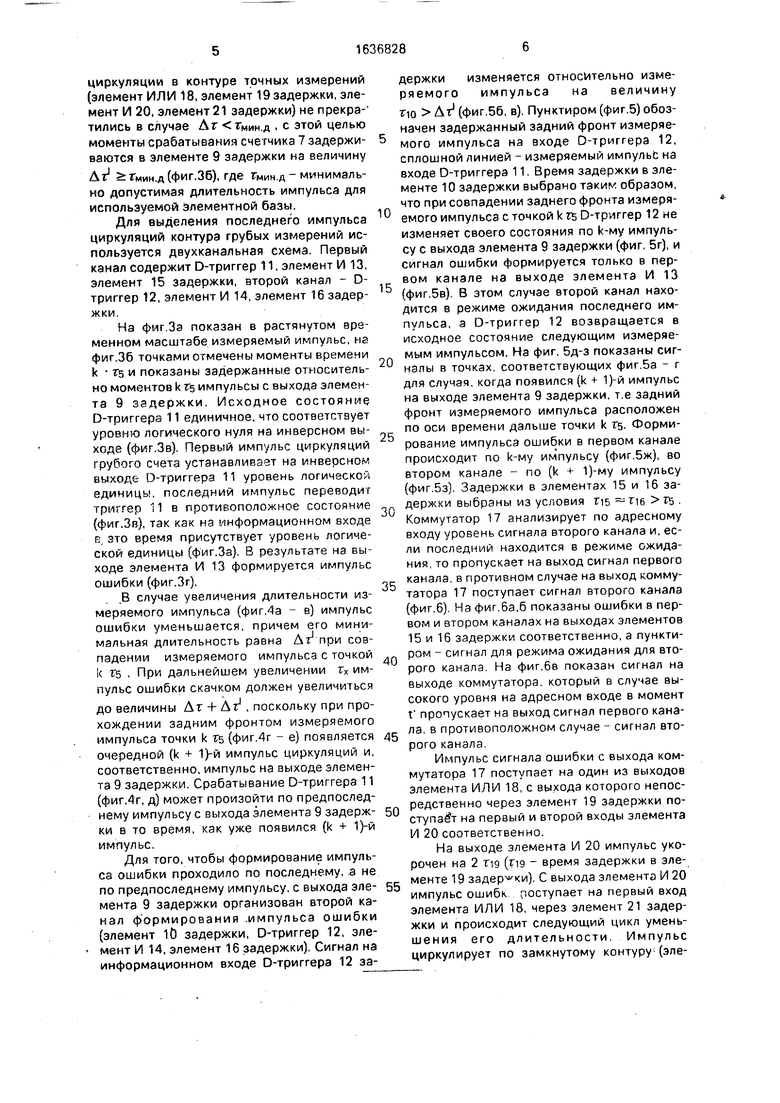

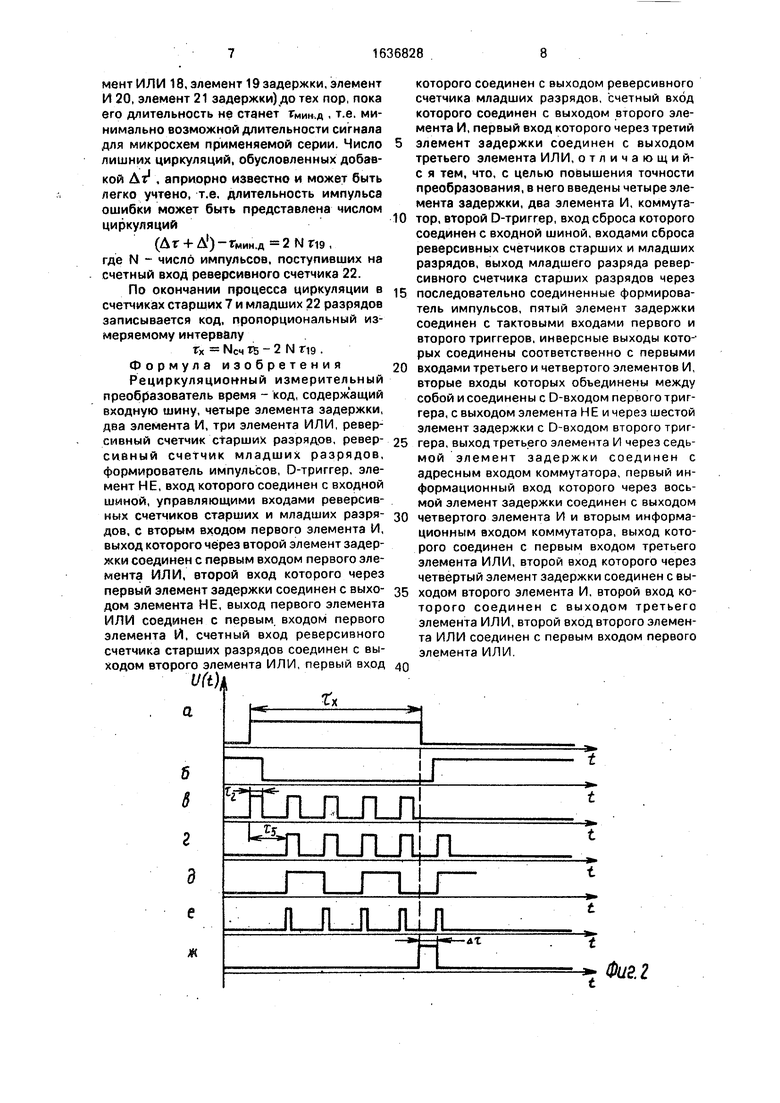

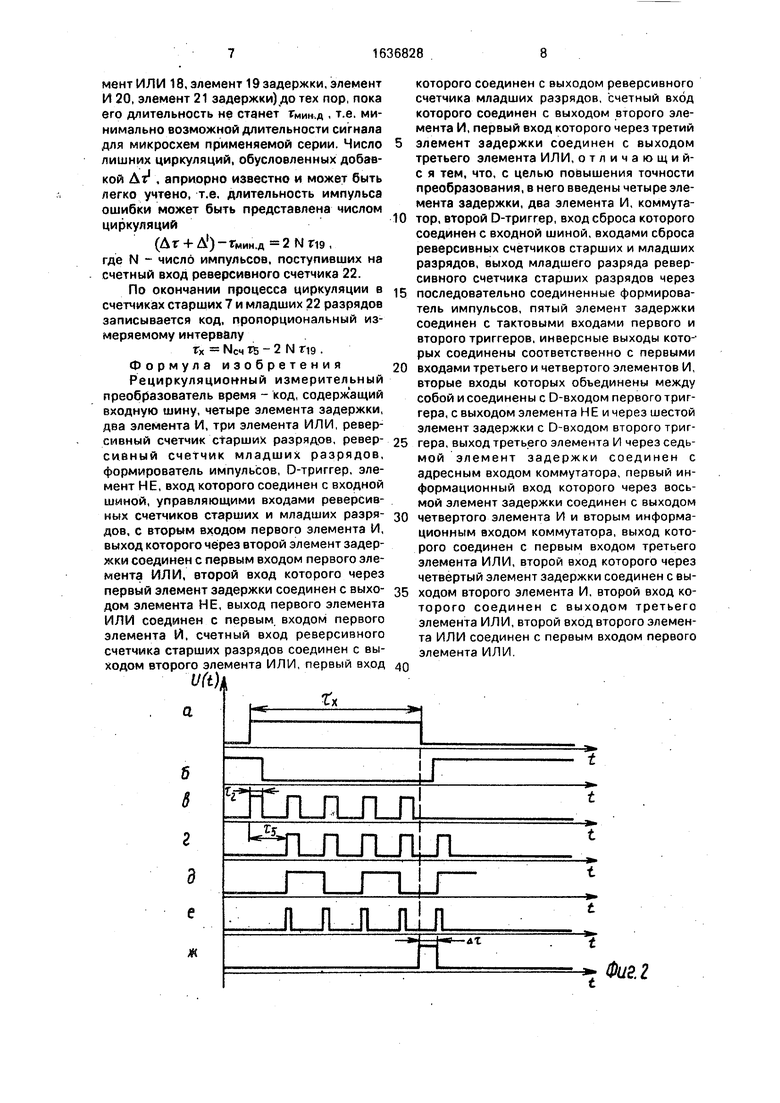

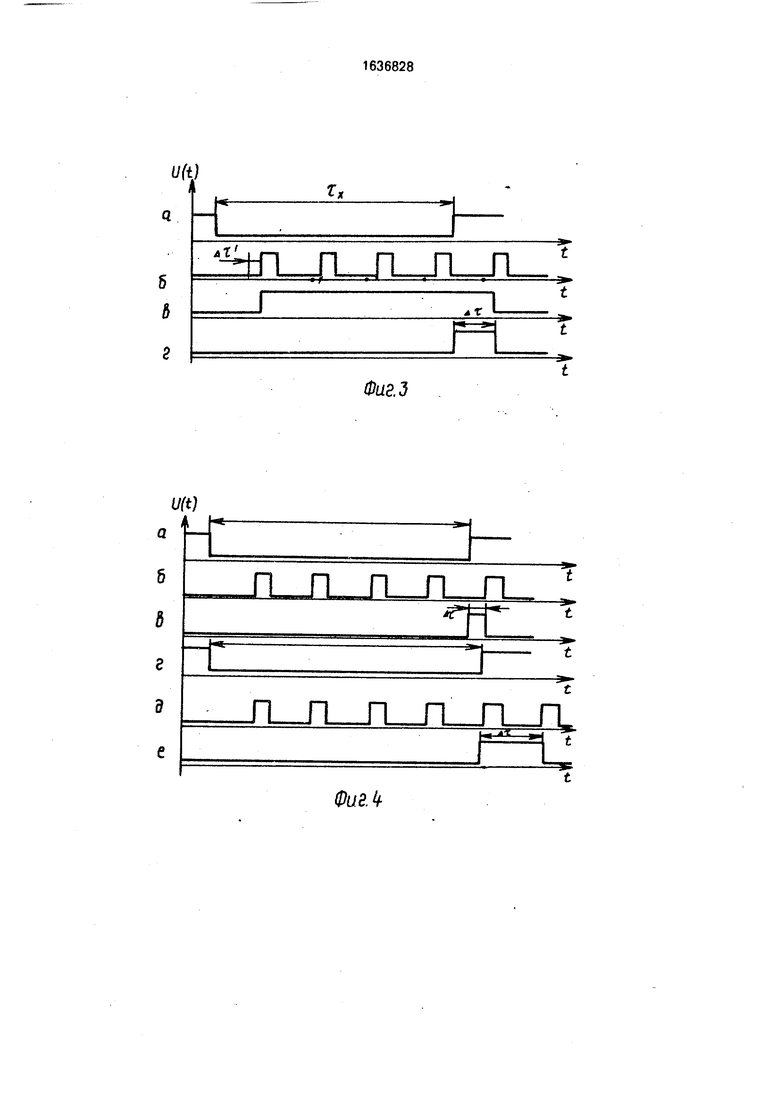

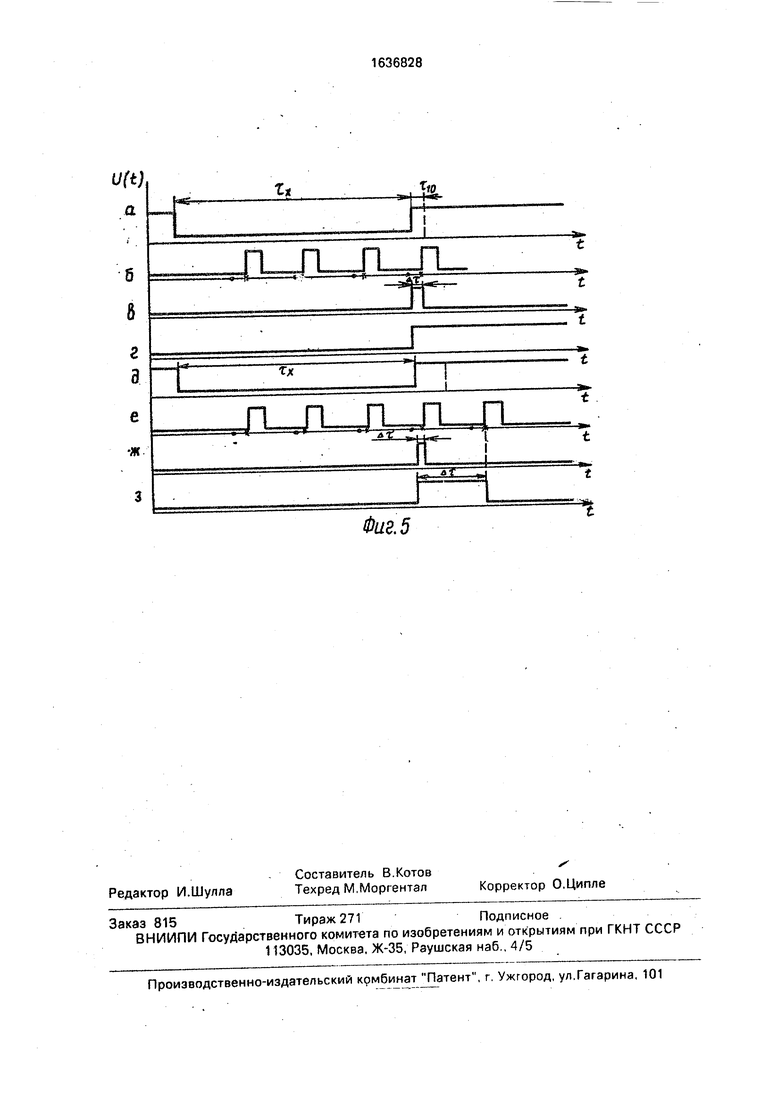

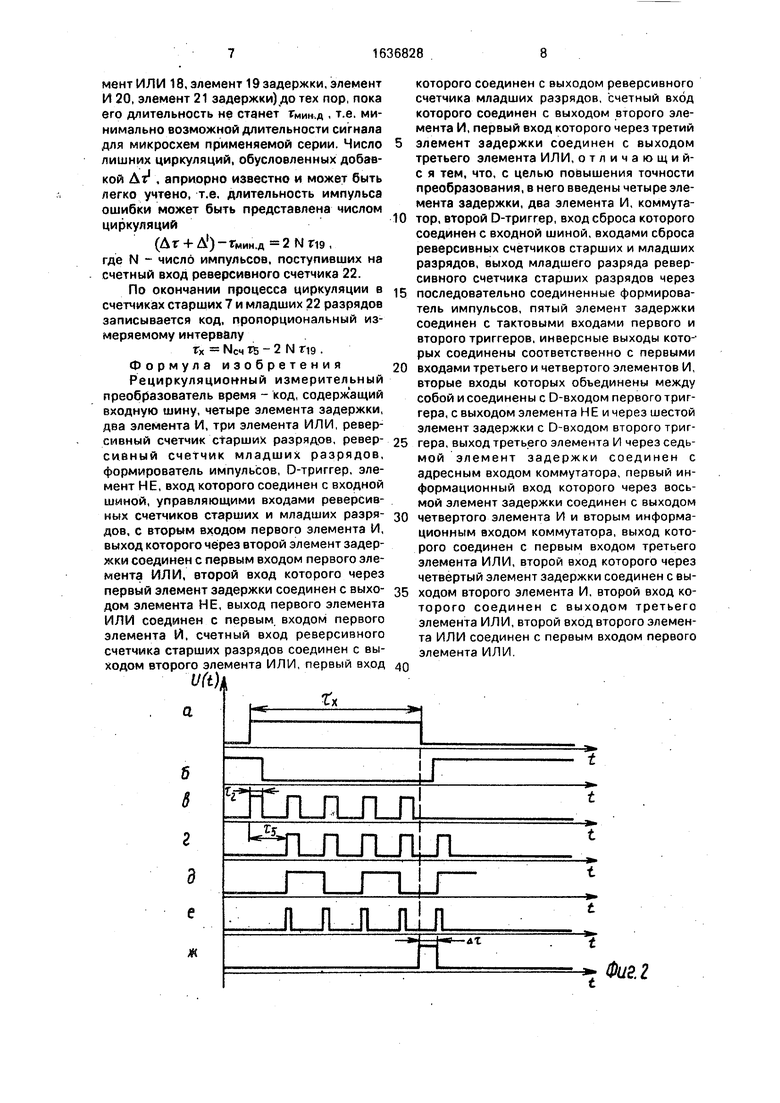

. На фиг.1 приведена структурная схема рециркуляционного измерительного преоб- разователя время - код; на фиг.2 - времен- ные диаграммы работы канала грубых измерений; на фиг.З - 5 - временные диаграммы работы составных частей устройства по преобразованию величины Дт.

Рециркуляционный преобразователь время - код (фиг.1) содержит элемент НЕ 1, элемент 2 задержки, элемент ИЛИ 3, элемент И 4, элемент 5 задержки, элемент ИЛИ 6, реверсивный счетчик 7 старших разря- дов, формирователь 8 импульсов, элементы 9 и 10 задержки, D-триггеры 11 и 12, элементы-И 13 и 14, элементы 15 и 16 задержки, коммутатор 17, элем.ент ИЛИ 18, элемент 19 задержки, элемент И 20, элемент 21 задер- жки, реверсивный счетчик 22 младших разрядов.

Входная шина соединена с входами сброса и входами управления реверсивных счетчиков 7 и 22, R-входом D-триггера 12, вторыми входами элемента И 4 и входом элемента НЕ 1, выход которого соединен с D-входом триггера 11, вторыми входами элементов И 13 и 14, через элемент 10 задержки с D-входом триггера 12 и через эле- мент 2 задержки с вторым входом элемента ИЛИ 3. выход которого соединен с первым входом элемента И 14, выход которого через элемент 5 задержки соединен с первыми входами элементов ИЛИ 3 и 6. выход эле- мента ИЛИ 6 соединен со счетным входом реверсивного счетчика 7, выход первого разряда которого через последовательно соединенные формирователь 8 импульсов, элемент 9 задержки соединен с С-входами триггеров 11 и 12, инверсные выходы которых соединены соответственно с первыми входами элементов И 13 и 14, выход элемента И 13 через элемент 15 задержки соединен с адресным входом коммутатора 17, второй информационный вход которого соединен с выходом элемента И 14 и через элемент 16 задержки с первым информационным входом коммутатора 17, выход которого соединен с первым входом элемента ИЛИ 18, выход которого соединен с первым входом элемента И 20 и через элемент 19 задержки с вторым входом элемента И 20, выход которого соединен со счетным входом реверсивного счетчика 22 и через элемент 21 задержки с вторым входом элемента ИЛИ 18, второй вход элемента ИЛИ 6 соединен с выходом реверсивного счетчика 22.

Преобразователь работает следующим образом.

Измеряемый импульс положительной полярности длительностью гх (фиг.2а) поступает на входы установки в О реверсивных счетчиков 7 и 22, D-триггера 12 и через элемент НЕ 1 на вход элемента 2 задержки. Задержанный импульс отрицательной полярности (фиг.26) через элемент ИЛИ 3 поступает на первый вход элемента И 4, на второй вход которого поступает незадержанный измеряемый импульс положительной полярности с входной шины устройства. На выходе элемента И 4 формируется положительный импульс длительностью га (время задержки в элементе 2 задержки), поступающий через элемент 5 задержки на вход элемента ИЛИ 3. Время задержки в элементе 5 задержки TS выбрано больше TZ , таким образом, импульс длительностью Г2 циркулирует по замкнутому контуру гру- б.ых измерений (элементы ИЛИ 3, И 4, элемент 5 задержки) с периодом TS, определяющим дискретность грубых измерений (фиг.Зв).

Импульсы циркуляции через элемент ИЛИ 6 поступают на счетный вход датчика 1 старших разрядов. Реверсивные счетчики 7 и 22 работают в режиме суммирования в течение времени гх, а при отсутствии измеряемого сигнала гх - в режиме вычитания. Срыв циркуляции в контуре грубых измерений происходит в момент прихода заднего фронта измеряемого импульса. За время тх на реверсивный счетчик 7 поступает число импульсов МСч. на единицу больше целой

части отношения - .

Временный интервал, заключенный между задним фронтом измеряемого импульса и передним фронтом последнего задержанного импульса циркуляции с выхода элемента 5 задержки (фиг.Зг), является ошибкой счета Дг . Для уточнения измерений необходимо из веса младшего разряда счетчика 7 вычесть величину Дг

Тх Г5 (Меч - 1) ь (Г5 - Дг) Г5 NCH - Дг.

Выделение и точное измерение Дг проводится по фронту последнего импульса контура грубых измерений только в том случае, если сработал младший разряд счетчика 7 (фиг.2д,ж).

Для повышения точности измерения импульс ошибки увеличивается на некоторую фиксированную величину Дг , чтобы

циркуляции в контуре точных измерений (элемент ИЛИ 18, элемент 19 задержки, элемент И 20, элемент 21 задержки) не прекра- тились в случае А г тМИн.д , с этой целью моменты срабатывания счетчика 7 задерживаются в элементе 9 задержки на величину

Дг Тмин.д(фиг.Зб), где Гмин.д минимально допустимая длительность импульса для используемой элементной базы.

Для выделения последнего импульса циркуляции контура грубых измерений используется двухканальная схема. Первый канал содержит D-триггер 11, элемент И 13, элемент 15 задержки, второй канал - D- триггер 12, элемент И 14, элемент 16 задержки.

На фиг.За показан в растянутом временном масштабе измеряемый импульс, на фиг.36 точками отмечены моменты времени k TS и показаны задержанные относительно моментов k rs импульсы с выхода элемента 9 задержки. Исходное состояние D-триггера 11 единичное, что соответствует уровню логического нуля на инверсном выходе (фиг.Зв). Первый импульс циркуляции грубого счета устанавливает на инверсном выходе D-триггера 11 уровень логической единицы, последний импульс переводит триггер 11 в противоположное состояние (фиг.Зв), так как на информационном входе в, это время присутствует уровень логической единицы (фиг.За). В результате на выходе элемента И 13 формируется импульс ошибки (фиг.Зг).

,В случае увеличения длительности измеряемого импульса (фиг.4а - в) импульс ошибки уменьшается, причем его минимальная длительность равна Az при совпадении измеряемого импульса с точкой k TS , При дальнейшем увеличении гх импульс ошибки скачком должен увеличиться

до величины Аг + Дг , поскольку при прохождении задним фронтом измеряемого импульса точки k T5 (фиг.4г - е) появляется очередной (k + 1)-й импульс циркуляции и, соответственно, импульс на выходе элемента 9 задержки. Срабатывание D-триггера 11 (фиг.4г, д) может произойти по предпоследнему импульсу с выхода элемента 9 задержки в то время, как уже появился (k + 1)-й импульс.

Для того, чтобы формирование импульса ошибки проходило по последнему, а не по предпоследнему импульсу, с выхода элемента 9 задержки организован второй канал формирования .импульса ошибки (элемент 10 задержки, D-триггер 12, элемент И 14, элемент 16 задержки). Сигнал на информационном входе D-триггера 12 задержки изменяется относительно измеряемого импульса на величину

гю Дт (фиг.56, в). Пунктиром (фиг.5) обозначен задержанный задний фронт измеряе- мого импульса на входе D-триггера 12, сплошной линией - измеряемый импульс на входе D-триггера 11. Время задержки в элементе 10 задержки выбрано таким образом, что при совпадении заднего фронта измеря- емого импульса с точкой k тв D-триггер 12 не изменяет своего состояния по k-му импульсу с выхода элемента 9 задержки (фиг. 5г), и сигнал ошибки формируется только в первом канале на выходе элемента И 13 (фиг.5в). В этом случае второй канал находится в режиме ожидания последнего импульса, а D-триггер 12 возвращается в исходное состояние следующим измеряемым импульсом. На фиг. 5д-з показаны сигналы в точках, соответствующих фиг.5а - г для случая, когда появился (k + 1)-й импульс на выходе элемента 9 задержки, т.е задний фронт измеряемого импульса расположен по оси времени дальше точки k TS. Формирование импульса ошибки в первом канале происходит по k-му импульсу (фиг.бж), во втором канале - по (k + 1)-му импульсу (фиг.Бз). Задержки в элементах 15 и 16 задержки выбраны из условия Ti5 П6 т$ . Коммутатор 17 анализирует по адресному входу уровень сигнала второго канала и, если последний находится в режиме ожидания, то пропускает на выход сигнал первого канала, в противном случае на выход коммутатора 17 поступает сигнал второго канала (фиг.6). На фиг.6а,б показаны ошибки в первом и втором каналах на выходах элементов 15 и 16 задержки соответственно, а пунктиром - сигнал для режима ожидания для второго канала. На фиг.бв показан сигнал на выходе коммутатора, который в случае высокого уровня на адресном входе в момент t пропускает на выход сигнал первого канала, в противоположном случае - сигнал второго канала.

Импульс сигнала ошибки с выхода коммутатора 17 поступает на один из выходов элемента ИЛИ 18, с выхода которого непосредственно через элемент 19 задержки поступает на первый и второй входы элемента И 20 соответственно.

На выходе элемента И 20 импульс укорочен на 2 Tig (rig - время задержки в элементе 19 задержки). С выхода элемента И 20 импульс ошибк поступает на первый вход элемента ИЛИ 18, через элемент 21 задержки и происходит следующий цикл уменьшения его длительности. Импульс циркулирует по замкнутому контуру (эле0

5

0

0

5

0

5

мент ИЛИ 18, элемент 19 задержки, элемент И 20, элемент 21 задержки) до тех пор, пока его длительность не станет тмин.д , т.е. минимально возможной длительности сигнала для микросхем применяемой серии. Число лишних циркуляции, обусловленных добавкой А т1 , априорно известно и может быть легко учтено, т.е. длительность импульса ошибки может быть представлена числом циркуляции

(Д Т + Л1) - Гмии.д 2 N Т19 ,

где N - число импульсов, поступивших на счетный вход реверсивного счетчика 22.

По окончании процесса циркуляции в счетчиках старших 7 и младших 22 разрядов записывается код, пропорциональный измеряемому интервалу

гх Меч Т5 - 2 N Tig . Формула изобретения Рециркуляционный измерительный преобразователь время - код, содержащий входную шину, четыре элемента задержки, два элемента И, три элемента ИЛИ, реверсивный счетчик старших разрядов, реверсивный счетчик младших разрядов, формирователь импульсов, D-триггер, элемент НЕ, вход которого соединен с входной шиной, управляющими входами реверсивных счетчиков старших и младших разрядов, с вторым входом первого элемента И, выход которого через второй элемент задержки соединен с первым входом первого элемента ИЛИ, второй вход которого через первый элемент задержки соединен с выходом элемента НЕ, выход первого элемента ИЛИ соединен с первым, входом первого элемента И, счетный вход реверсивного счетчика старших разрядов соединен с выходом второго элемента ИЛИ, первый вход

u(t)l а

б Ь

a

е АК

которого соединен с выходом реверсивного счетчика младших разрядов, счетный вход которого соединен с выходом второго элемента И, первый вход которого через третий

элемент задержки соединен с выходом третьего элемента ИЛИ, отличающий- с я тем, что, с целью повышения точности преобразования, в него введены четыре элемента задержки, два элемента И, коммутатор, второй D-триггер, вход сброса которого соединен с входной шиной, входами сброса реверсивных счетчиков старших и младших разрядов, выход младшего разряда реверсивного счетчика старших разрядов через

последовательно соединенные формирователь импульсов, пятый элемент задержки соединен с тактовыми входами первого и второго триггеров, инверсные выходы кото-1 рых соединены соответственно с первыми

входами третьего и четвертого элементов И, вторые входы которых объединены между собой и соединены с D-входом первого триггера, с выходом элемента НЕ и через шестой элемент задержки с D-входом второго триггера, выход третьего элемента И через седьмой элемент задержки соединен с адресным входом коммутатора, первый информационный вход которого через восьмой элемент задержки соединен с выходом

четвертого элемента И и вторым информационным входом коммутатора, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого через четвертый элемент задержки соединен с выходом второго элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ, второй вход второго элемента ИЛИ соединен с первым входом первого элемента ИЛИ.

0

Фиг. 2

им

ЛП ПП

ФигЛ

Фиг.З

Фиг. 5

| Устройство дискретного измерения временных интервалов | 1975 |

|

SU506827A2 |

| Рециркуляционный измерительный преобразователь время-код | 1977 |

|

SU721796A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-03-23—Публикация

1988-11-23—Подача