Изобретение относится к вычислительной технике и может быть использовано для отладки в реальном масштабе времени цифровых программ многопроцессорных систем управления многомерными непрерывными и непрерывно-дискретными объектамио

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения отладки в реальном масштабе времени параллельно работающих цифровых процессоров,.

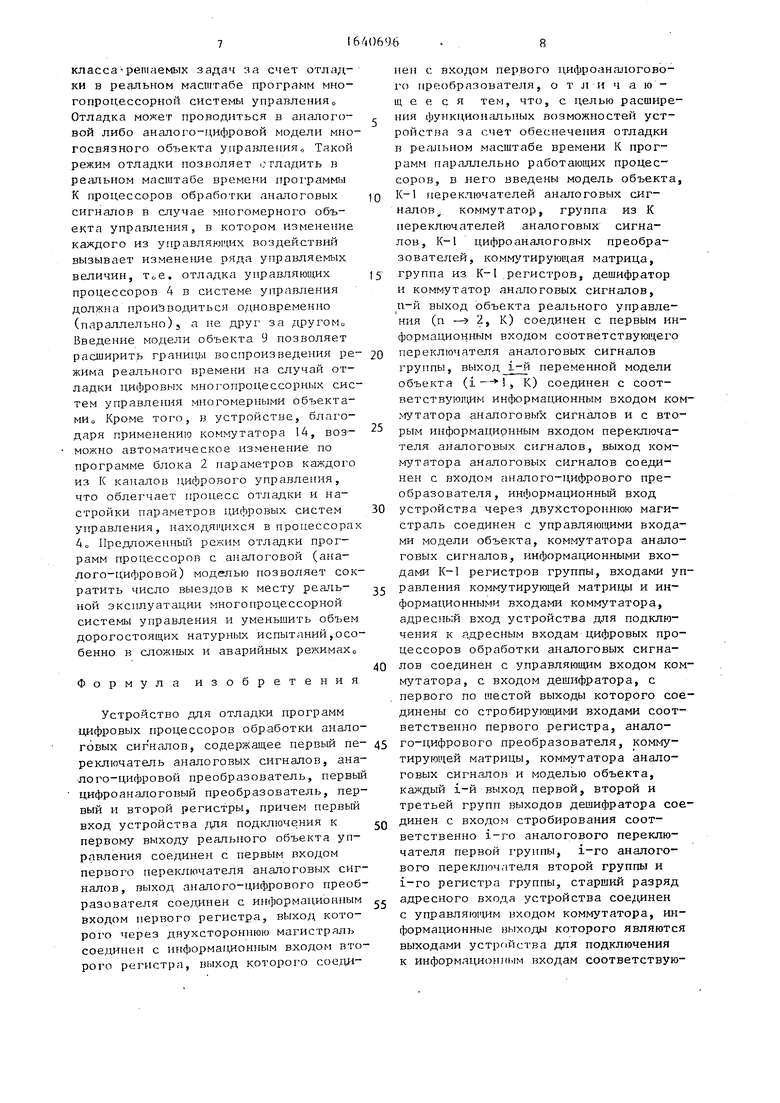

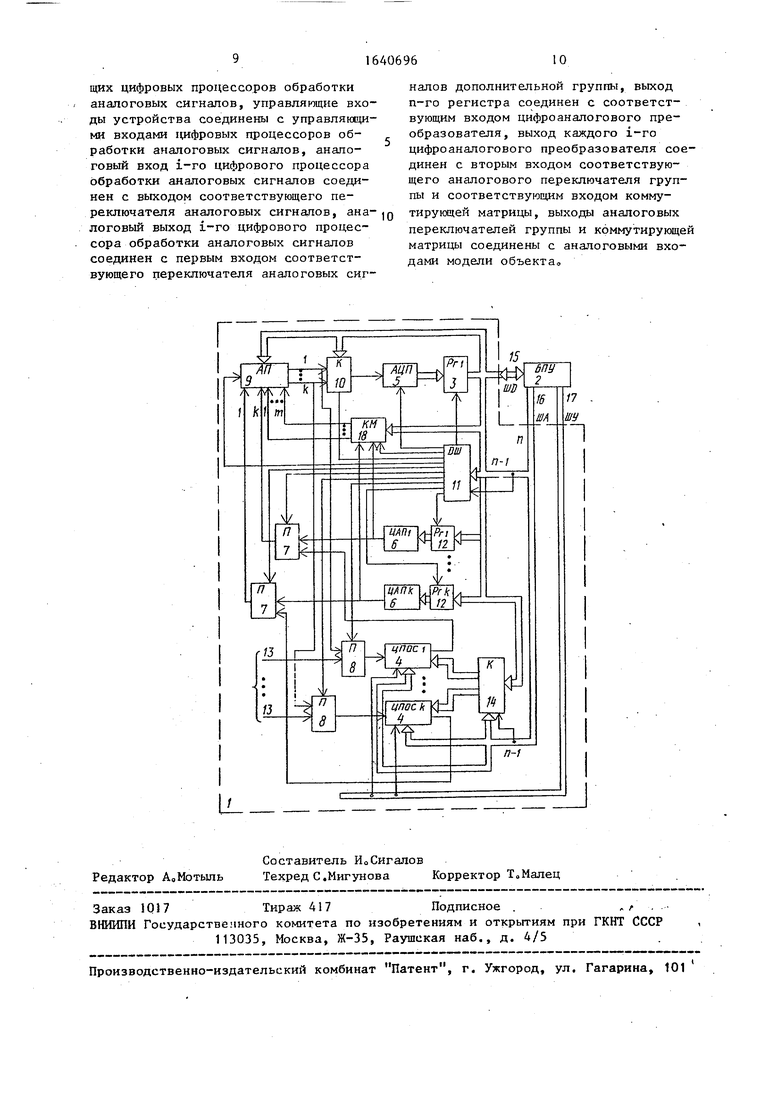

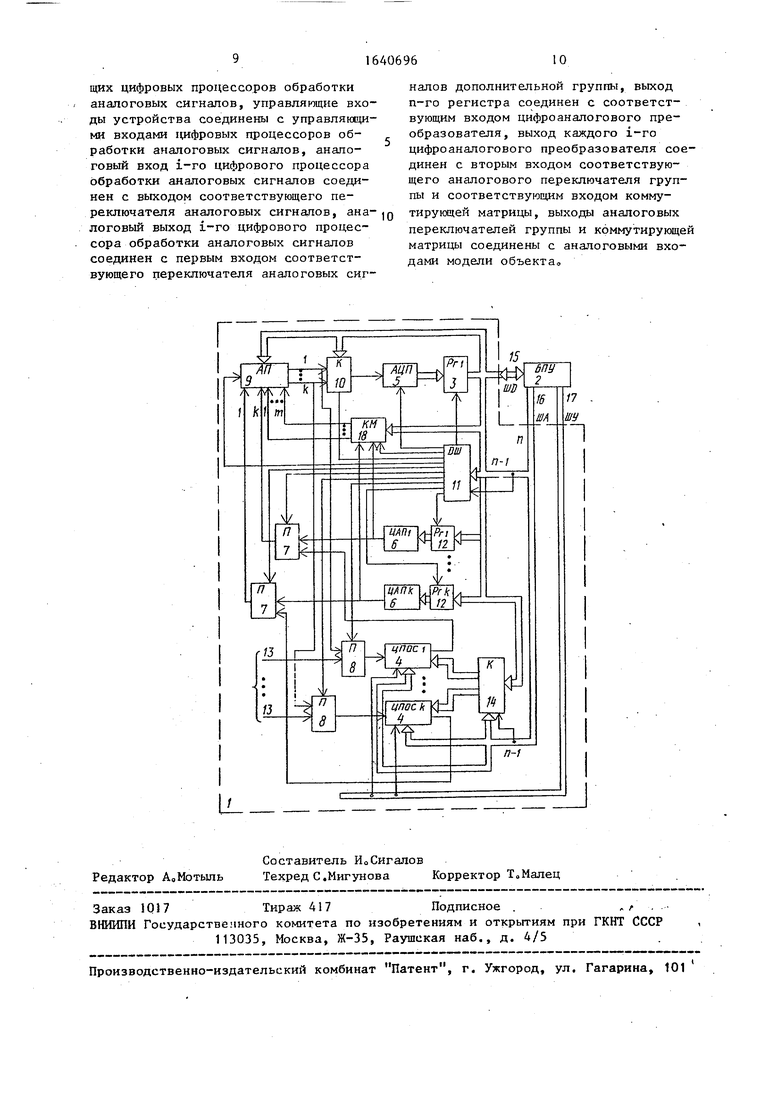

На чертеже изображена блок-схема

устройства

Кроме устройства 1 для отладки программ цифровых процессоров обработки аналоговых сигналов на фиг01 изображен блок 2 программного управленияо Устройство 1 содержит регистр 3 ввода, К цифровых процессоров 4 обработки аналоговых сигналов, аналого-цифровой преобразователь 5, К циф- роаналоговых преобразователей 6, переключатели 7 и 8 аналоговых сигналов, модель объекта 9, коммутатор 10 аналоговых сигналов, дешифратор 11, К регистров 12 вывода, выходы 13 реального объекта управления, коммутатор 14, выходные шины 15 - 17 соответственно данных адреса и управления устройства 1, причем шина 15 является двунаправленной, коммутирующую матрицу 18 Для пояснения работы устройства 1 к шинам 15-17 подключен блок 2 программного управления, в качестве которого может быть использована мини- или микро-ЭВМ с соответст-, вующими кросс-системамио

СЭ 4

О

оэ со

О5

В качестве модели объекта 9, например, может быть использована аналоговая вычислительная машина АВК-32 либо аналоговый процессор АП-410 В качестве коммутатора 10 аналоговых сигналов может быть использована БИС К 591 КН Зо Коммутирующая матрица 18 может быть реализована на БИС К 590 КН 14о

Устройство работает следующим образом

На этапе подготовки программ для цифровых процессоров 4 обработки аналоговых сигналов производится последовательная откладка программ для каждого цифрового процессора 4 на блоке 2 программного управления0

Программа, написанная на языке ассемблера 1-го процессора 4, вводится с помощью стандартных средств в блок 2 и отлаживается известным способом на программной модели в замедленном масштабе временно Работа блока 2 осуществляется в соответствии с алгоритмом, приведенным на фиг020Это позволяет проверить выполнение логических условий в реализованном алгоритме управления, вывести на экран или печать содержимое внутренних блоков процессоров 4 (ячейки ОЗУ, резултат в АЛУ и т„До) и результат работы отлаживаемой программы при фиксированных входных параметрах0 Если 1-я программа работает неправильно, то производится коррекция программы, а отлаженная таким образом программа записывается во внутреннее ППЗУпрограмм 1-го процессора 4 с помощью стандартного программатора Процесс повторяется до отладки и записи в ППЗУ соответствующих процессоров 4 всех К программе

В результате выполнения этапа подготовки в ППЗУ процессоров 4 загружены отлаженные в нормальном масштабе времени программы управления, а в ОЗУ этих процессоров внесены параметры воспроизводимых на этих процессорах законов управления (например, для П-, ПИ- и ПИД-регуляторов в качестве параметров могут служить коэффициенты усиления, постоянные времени, для оптимальных по быстродействию регуляторов - моменты времени изменения параметров и сами параметры И То По)о

Запись параметров ОЗУ процессоров 4 производится блоком 2 через комму

10

15

20

25

406964

татор 14„ При этом адресное пространство, определяемой разрядностью шины 16 адреса, играет роль управляющего разряда, в зависимости от состояния 5 которого осуществляется работа либо дешифратора 11, либо коммутатора 140 Оставшиеся (п-1) разрядов шины 16 адреса используются для адресации к ячейкам ОЗУ процессоров 4„ Таким образом, часть разрядов 1 (где ) уп- равляет коммутатором 14, подключая шину 15 данных к шине данных 1-го процессора 4, а остальные разряды задают адрес ячеек ОЗУ выбранного процессора 4 о

На этапе подготовки аналоговой модели многомерного объекта управления производятся разработка схемы моделирования для модели объекта 9, набор схемы моделирования на операционных блоках процессора и контроль работоспособности модели при тестовых управляющих и возмущающих воздействиях0 Исходные дифференциальные уравнения, описывающие динамику многомерного объекта управления (объекта, в котором используются значения нескольких управляющих координат и нескольких управляемых координат), вводятся в блок 2, в который предварительно загружается система автоматизации программирования аналогового процессора. В результате работы системы автоматизации программирования получается схема набора модели и выполняется ее набор в блоке 90 Контроль работы модели объекта выполняется путем подачи тестовых сигналов на входы модели объекта 9 с блока 2 через регистры 12, ЦАП 6 и переключатели 7« Реакция модели объекта в виде показателей качества процесса управления (перерегулирование, число колебаний, время установления процесса, статическая точность и TO По) записывается в блок 2 и сравнивается со значениями, полученными экспериментально на реальном объекте0 При необходимости параметры модели на блоке 9 корректируются до достижения удовлетворительного совпадения модели с объекТОМо

О

35

40

45

50

Подача тестовых управляющих и возмущающих воздействий на входы модели объекта 9 из блока 2 и запись в блок 2 их значений производится таким образом, что через дешифратор 1I выбирается один из регистров 12,в который вводится по шине 15 данных необходимый код, преобразуемый с помощью ЦАП 6 в аналоговую величину, подающуюся на соответствующий вход модели 9 через переключатель 7, Аналогично через дешифратор 11 выбирается коммутатор 10 аналоговых сигналов, на цифровой вход которого по шине 15 подается код, определяющий номер канала, подключаемого к АЦП 50 Затем запускается АЦП 5 сигналом от дешифратора 11 о Цифровое значение аналогового сигнала считывается с регистра 3 в блок 2о При этом выбор регистра 3 также производится блоком 2 через дешифратор 1 1 „

В результате выполнения этапа подготовки модели объекта управления на модели 9 набрана и отлажена модель динамики многомерного объекта управления в реальном масштабе временно На этапе откладки в реальном времени программ цифровых процессоров 4 с моделью многомерного объекта переключатели 7 по сигналу от блока 2 через дешифратор адреса переключаются в положение, при котором выходы цифровых процессоров подключаются к входам модели 9 о Блок 2 осуществляет пуск аналогового процессора и всех цифровых процессоров 4 обработки аналоговых сигналово Режим Пуск и другие сигналы управления блоком 9 вырабатываются блоком 2 и поступают в блок 9 по шине 15 данных при выборе блока 9 сигналом с дешифратора 110

Возмущающие воздействия на объект управления организуются путем использования блоков тестовых напряжений, имеющихся на серийных аналоговых вычислительных машинах и управляемых с ее клавиатуры, либо переключениями в схеме моделирования, управление которыми осуществляются по шине 15 при наличии сигнала с дешифратора 11,либо подачей возмущающих воздействий с выходов коммутирующей матрицы 18оПроцессоры управления наблюдаются в реальном масштабе времени на светолуче- вом многоканальном индикаторе (например, ИМ-789), Необходимые процессы записываются в память блока 2,причем с целью сжатия информации в памяти сохраняются только показатели качества управления - значение перерегулирования переходного процесса, количество колебаний, время установ1

10

15

406966

ления процесса регулирования после момента подачи возмущения на объекта Сравнение этих показателей с эталонными значениями или требованиями тех5 нического задания позволяют сделать вывод о качестве процессов управления. Если качество управления не удовлетворяет требованиям, то производится отладка (подстройка) параметров в программах управления, записанных в процессоры 4о Блок 2 переводит блоки 9 и 4 в режим Останов Из блока 2 программного управления на коммутатор 14 задается адрес ячеек ОЗУ выбранного процессора 45 Под управлением сигналов с шины 17 управления производится последовательный ввод параметров в процессор 4„ После

20 ввода новых параметров в ОЗУ процессоров 4 повторяется моделирование процессов управления и их оценка до удовлетворительного исхода., В противном случае процесс откладки повторяет25 ся сначала, например вносятся изменения в алгоритм и программу управления одного или нескольких процессоров 4 о

Предлагаемое устройство позволяет

зр. отлаживать программы управления, за- писанные на цифровых процессорах 4 обработки сигналов и в более сложном случае, когда сам объект управления является непрерывно-дискретнымо В этом случае аналого-цифровая модель

объекта управления реализуется, на модели объекта 9, блоке 2 программного управления и средствах преобразования и обмена информацией между ними, блоках 5, 0, 3, 12, Ь, 18о Коммутирующая матрица 18 при этом обеспечивает передачу данных из блока 2 после преобразования их ЦАП 60 В том случае, когда идет процесс откладки

,с в реальном масштабе времени, переключатели 7 отключают выходы ЦАП 6 от входов модели объекта 9.

На этапе откладки программы процессоров 4 с реальным объектом управ5Q ления переключатели 8 подключают выходы реального объекта к входам процессоров 40 Отладки программ и подстройки параметров в программных процессорах 4 на этом этапе аналогичны предыдущему этапу„

Таким образом, в предложенном устройстве для отладки программ цифровых процессоров обработки аналоговых/ сигналов обеспечивается расширение

40

55

класса-решаемых задач за счет отладки в реальном масштабе программ многопроцессорной системы управления„ Отладка может проводиться в аналоговой либо аналого-цифровой модели многосвязного объекта управления. Такой режим отладки позволяет огладить в реальном масштабе времени программы К процессоров обработки аналоговых сигналов в случае многомерного объекта управления, в котором изменение каждого из управляющих воздействий вызывает изменение ряда управляемых величин, Тсв. отладка управляющих процессоров 4 в системе управления должна производиться одновременно (параллельно)5 а не друг за другом Введение модели объекта 9 позволяет расширить границы воспроизведения ре- жима реального времени на случай отладки цифровых многопроцессорных систем управления многомерными объектами,, Кроме того, в устройстве, благодаря применению коммутатора 14, воз- можно автоматическое изменение по программе блока 2 параметров каждого из К каналов цифрового управления, что облегчает процесс отладки и настройки параметров цифровых систем управления, находящихся в процессорах 4„ Предложенный режим отладки программ процессоров с аналоговой (аналого-цифровой) моделью позволяет сократить число выездов к месту реаль- ной эксплуатации многопроцессорной системы управления и уменьшить объем дорогостоящих натурных испытаний,особенно в сложных и аварийных режимах

Формула изобретения

Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов, содержащее первый пе- реключатель аналоговых сигналов, аналого-цифровой преобразователь, первый цифроаналоговый преобразователь, первый и второй регистры, причем первый вход устройства для подключения к

первому выходу реального объекта управления соединен с первым входом первого переключателя аналоговых сигналов, выход аналого-цифрового преобразователя соединен с информационным входом первого регистра, выход которого через двухстороннюю магистраль соединен с информационным входом второго регистра, выход которого соединен с входом первого цифроаналогово- го преобразователя, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения отладки в реальном масштабе времени К программ параллельно работающих процес- соров, в него введены модель объекта, К-1 переключателей аналоговых сигналов, коммутатор, группа из К переключателей аналоговых сигналов, К-1 цифроаналоговых преобразователей, коммутирующая матрица, группа из К-1 регистров, дешифратор и коммутатор аналоговых сигналов, u-й выход объекта реального управления (п. - 2, К) соединен с первым информационным входом соответствующего переключателя аналоговых сигналов группы, выход i-й переменной модели объекта (i -- 1 , К) соединен с соответствующим информационным входом коммутатора аналоговых сигналов и с вторым информационным входом переключателя аналоговых сигналов, выход коммутатора аналоговых сигналов соединен с входом аналого-цифрового преобразователя, информационный вход устройства через двухстороннюю магистраль соединен с управляющими входами модели объекта, коммутатора аналоговых сигналов, информационными входами К-1 регистров группы, входами управления коммутирующей матрицы и информационными входами коммутатора, адресный вход устройства для подключения к адресным входам цифровых процессоров обработки аналоговых сигналов соединен с управляющим входом коммутатора, с входом дешифратора, с первого по тестой выходы которого соединены со стробиругащими входами соответственно первого регистра, аналого-цифрового преобразователя, коммутирующей матрицы, коммутатора аналоговых сигналов и моделью объекта, каждый i-й выход первой, второй и третьей групп выходов дешифратора соединен с входом стробирования соответственно 1-го аналогового переключателя первой группы, 1-го аналогового переключателя второй группы и 1-го регистра группы, старший разряд адресного входа устройства соединен с управлякицим входом коммутатора, информационные выходы которого являются выходами устройства для подключения к информационным входам соответствующих цифровых процессоров обработки аналоговых сигналов, управляющие входы устройства соединены с управляющи- ми входами цифровых процессоров обработки аналоговых сигналов, аналоговый вход 1-го цифрового процессора обработки аналоговых сигналов соединен с выходом соответствующего переключателя аналоговых сигналов, аналотовый выход 1-го цифрового процессора обработки аналоговых сигналов соединен с первым входом соответствующего переключателя аналоговых сигналов дополнительной группы, выход n-го регистра соединен с соответствующим входом цифроаналогового преобразователя, выход каждого 1-го цифроаналогового преобразователя соединен с вторым входом соответствующего аналогового переключателя группы и соответствующим входом коммутирующей матрицы, выходы аналоговых переключателей группы и коммутирующей матрицы соединены с аналоговыми входами модели объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ цифровых процессоров обработки сигналов | 1986 |

|

SU1339570A1 |

| Устройство формирования сигнала для коррекции искажений телевизионного изображения | 1985 |

|

SU1317687A2 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Цифро-аналоговая система для регистрации и статистической обработки информации | 1979 |

|

SU858023A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для отладки управляющего комплекса сортировочной горки | 1984 |

|

SU1237528A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006941C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ПОТОКА НА ВЫХОДЕ ИЗ СОПЛА | 1990 |

|

RU2047119C1 |

Изобретение относится к вычислительной технике и может быть использовано для отладки в реальном масштабе времени цифровых программ многопроцессорных систем управления„ Цель изобретения - расширение функциональных возможностей Устройство содержит регистр ввода, аналого-цифровой преобразователь, К цифроанало- говых преобразователей, два переключателя аналоговых сигналов,модель объекта, коммутатор аналоговых сигналов, дешифратор, К регистров вывода, коммутатор, коммутирующую матрицу„ Устройство обеспечивает отладку в реальном масштабе времени параллельно работающих цифровых процессоров0 1 ил „ S (Л

| Устройство для отладки программ | 1986 |

|

SU1327112A1 |

Авторы

Даты

1991-04-07—Публикация

1988-06-20—Подача