руемых сигналов, а выход соединен с входом блока сопряжения с объектом отлаживаемого управляющего комплекса сортировочной горки, блок автономных режимов снабжен счетчиком импульсов, третьим мультиплексором, элементом ручного формирования команды, элементом ИЛИ, формирователем синхросигналов, выход которого соединен с входом счетчика импульсов, выход которого соединен с нервым информационным входом третьего мультиплексора, второй информационный вход которого соединен с первым выходом элемента ручного форми1

Изобретение относится к автоматизиро- 15ан1;ым системам управления технологическими процессами на железнодорожном транспорте и может быть использовано для проведения отладки и испытаний автоматизированных систем у |равле1гия роспуском составов па сортировочных горках.

Цель изобретения - повышение точности устройства.

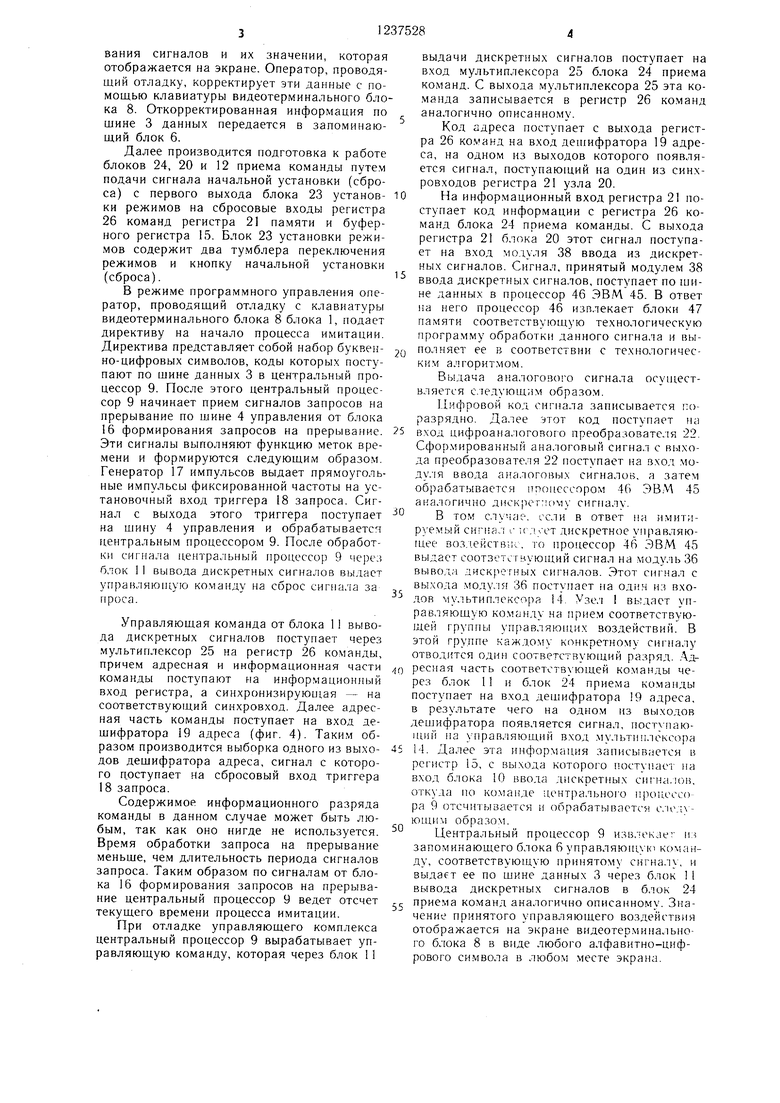

На фиг. представлена С1руктурная схема устройства для отладки управляющего комплекса со.;.УГ}|ров()чпой Г оркн.

Устройство содержит узел 1 имитации сигналов технологических объектов сортировочной горки.. имеюн1ий центральный iipoHCC- сор 2 с шиной 3 данных, 1ниной 4 управления и адресной щииой 5, которыми соединены входящие в узел 1 запоминающий блок 6, блок 7 памяти, видеотер- мпнальный блок 8, блок 9 ввода--вывода И1 формации на перфоленту, блок 10 вво;.1,а диск1и:-тных сигналов и блок 1 вывода дис; :;:егн1з1х сигналов. Устройство содерж1гг так/КС подключенный выходом к входу узла I блок 12 прие.ча управ. яющих воздействий, кпгг1р лй имеет аналого-цифровой преоб- paioii-s 3. подкл Оченн ый входом к его выходу му.-|ьтиплексор 14 и подключенный к вы.хо.гу 1 -оследнего буферный регистр 15.

В устройство входит блок 16 формирования запросов на ирерыванне, содержащий генератор 17 импульсов и соединенный с ним Ti rMfrep 18 запроса, де1пи(|)ратор 19 ад- ресгг, узел 20 хранения имитируемых сигна- ло:;., в ыотогчый входят регистр 21 памяти и ц:.1фроа ало1Ч)зый преобразователь 22, б.лок 23 установки режимов и соединенный с последним 6.ЛОК 24 приема команд, в который входят мультиплексор 25 и регистр 26 команд, блок 27 автономных режимов, име- юихий фор.мирователь 28 синхросигналов, под к:1ючен1;ый к нему счетчик 29 импульсов, соединенный входом с выходом последнего

рования команд, а выход -- с вторым информационным входом первого мультиплексора блока приема команды, второй выход элемента ручного формирования команд соединен с нервым входом элемента ИЛИ, второй вход которого соединен с вых-) формирователя дискретных сигналов, выход - с третьим информационным входом первого мультиплексора, четвертый информационный вход которого соединен с выходом формирователя синхросигна. юв, а управляющий вход третьего мул1/ги 1лексора соединен с третьим выходом блока установки режимов отладки.

мультиплексор 30, гюдключенный одним вы ходом к входу последнего элемергг 31 ручного формирования команды, связанный одним входом с другим выходом носледнего

элемента ИЛИ 32, соединенный с другим входом элемента 32 формирователь 33 дискретных сигналов и 1формирователь 34 сиг- синхронизации, с которым связан узел 35 сопряжения с объектом отлаживаемого комплекса, в который входяг модули 36--41

соответственно вывода 42 дискретных ана;1О- гичных сигналов, ввода 43 дискретных и ввода 44 аналоговых ,:1ов. к узлу 35 сопряжения нодк.лючается ЭВМ 45, имеющая процессор 46 и блок 47 памяти.

Устройство работает следую ц|--;м образом.

Для проведения отладки н испытания системы прежде всего необходимо выполнить операции по подготовке .имитатора к работе. Временная диаграмма им тгир емых сигналов необходимо1Ю набора 1 ехнологических

у зон горки (рассчита П ая заранее один раз для .данного обт..екта па ЭВМ общего назначения путем модели К)вания процесса роспуска состава с горки) вводится в запоминающий блок 6 узла 1 имитации сигналов технологического объекта с перфо.лен- ты через блок 9 ввода-вывода или с гибкого магнитного диска через блок 7 па.мяти, либо вручную с помощью клавиатуры видеотерминального блока 8 в виде носледователь- ностн кодов команд формирования нужных сигналов, содержащих информацию о времени, выдачи сигналов и их значении.

При необходимости может бьпъ произве- д.ека оперативная корректировка временной диаграммы сигналов, а также выбор определенного набора сигналов в технологических зонах нри номонли видеотерминального блока 8. Это осуществляется следующим образом. Из запоминающего блока 6 на вкдеотерминальный блок 8 по щине 3 данных поступает информация о времени срабатыO

5

вания сигналов и их значении, которая отображается на экране. Оператор, проводящий отладку, корректирует эти данные с помощью клавиатуры видеотерминального блока 8. Откорректированная информация по шине 3 данных передается в запоминающий блок 6.

Далее производится подготовка к работе блоков 24, 20 и 12 приема команды путем подачи сигнала начальной установки (сброса) с первого выхода блока 23 установки режимов на сбросовые входы регистра 26 команд регистра 21 памяти и буферного регистра 15. Блок 23 установки режимов содержит два тумблера переключения режимов и кнопку начальной установки (сброса).

В режиме программного управления оператор, проводящий отладку с клавиатуры видеотерминального блока 8 блока 1, подает директиву на начало процесса имитации. Директива представляет собой набор букве - но-цифровых символов, коды которых поступают по шине данных 3 в центральный процессор 9. После этого центральный процессор 9 начинает прием сигналов запросов на прерывание по шине 4 управления от блока 16 формирования запросов на прерывар|ие. Эти сигналы выполняют функцию меток времени и формируются следующим образо.м. Генератор 17 импульсов выдает прямоугольные импульсы фиксированной частоты на установочный вход триггера 18 запроса. Сигнал с выхода этого триггера поступает на шину 4 управления и обрабатывается центральным процессором 9. После обработки сигнала центральный процессор 9 через блок 11 вывода дискретных сигналов выдаст управляюп ую команду на сброс сигнала за проса.

Управляющая команда от блока 11 вывода дискретных сигналов поступает через мультиплексор 25 на регистр 26 команды, причем адресная и информационная части команды поступают на информационный вход регистра, а синхронизирующая - на соответствующий синхровход. Далее адресная часть команды поступает на вход дешифратора 19 адреса (фиг. 4). Таким образом производится выборка одного из выходов дешифратора адреса, сигнал с которого аоступает на сбросовый вход триггера 18 запроса.

Содержимое информационного разряда команды в данном случае может быть любым, так как оно нигде не используется. Время обработки запроса на прерывание меньше, чем длительность периода сигналов запроса. Таким образом по сигналам от блока 16 формирования запросов на прерывание центральный процессор 9 ведет отсчет текущего времени процесса имитации.

При отладке управляющего комплекса центральный процессор 9 вырабатывает управляющую команду, которая через блок 11

выдачи дискретных сигналов поступает на вход мультиплексора 25 блока 24 приема команд. С выхода мультиплексора 25 эта команда записывается в регистр 26 команд аналогично описанному.

Код адреса поступает с выхода регистра 26 команд на вход дешифратора 19 адреса, на одном из выходов которого появляется сигнал, поступающий на один из синх- ровходов регистра 21 узла 20. 0 На информационный вход регистра 21 поступает код информации с регистра 26 команд блока 24 приема команды. С выхода регистра 21 блока 20 этот сигнал поступает на вход модуля 38 ввода из дискретных сигналов. Сигнал, принятый модулем 38 ввода дискретных сигналов, поступает по шине данных в про ;ессор 46 ЭВМ 45. В ответ lia него процессор 46 извлекает блоки 47 памяти соответствующую технологическую программу обработки данного сигнала и вы5

20

полняет ее в соответствии с технологичесKiiM алгоритмом.

Выдача аналогового сигнала осуществляется с.тедующим образом.

Цифровой код сигнала записывается по- разрядно. Далее этот код поступает на

5 вход цифроаналогового преобразователя 22. Сформированный аналоговый сигнал с выхода преобразователя 22 поступает на вход мо- ду. 1Я ввода aiia.noroBbix сигналов, а затем обрабатывается I noiicccopoM 46 ЭВЛ1 45 аналогично дискретному сигналу.

В том случае, если в ответ на H.VIHTH- руемый сигнал . if Л . ет дискретное управляющее возл.ействис. то процессор 46 ЭВМ 45 выдает соответствующий сигнал на модуль 36 выво.та дискретных сигналов. Этот сигнал с выхода модуля 36 поступает на один из вхо- дов мультиплексо)а 14. Узе.ч 1 выдает управляющую команду на прием соответствующей группы управляющих воздействий. В этой группе кaждo y конкретному сигналу отводится один соответствую ций разряд, .дQ ресная часть соответствующей команды через блок 11 и блок 24 приема команды поступает на вход дешифратора 9 адреса, в результате чего на одном из выходов дешифратора появляется сигнал, поступающий на управляющий вход .мультиплексора

5 14. Далее эта информация записывается в регистр 15, с выхода которого поступает на вход блока 10 ввода дискретных си гнался), откуда по кома1 де центрально1 о происссо ра 9 отсчитывается и обрабатывается с. кмх- ющмм образом.

Центральный процессор 9 извлекает из запоминающего блока 6 управляющую коман- ду, соответствующую принятому сигналу, и выдает ее по шине дранных 3 через блок 1 1 вывода дискретных сигналов в блок 24

t; приема команд аналогично описанному. Значение принятого управляющего воздействия отображается на экране видеотерминального б;гока 8 в виде любого алфавитно-цифрового символа в любом месте экрана.

Аналогов -;;; у11р;:1МЯК1М ,ий сиснал о выхода модуля 37 Hi.nio. Ui аня. юговых сигналов поступает на вход аналого-цифрового преобразователя 13 и далее в виде параллельного кода на мультиплексор 14. Дальнейшая обработка сигнала производится аналогично обработке дискретного у11равляюп;е- го сигнала.

Имитируемый сигнал, который является ответом на принятое управляюп1.ее воздействие, формируется в момент времени, определяемый специальным программным обеспечением устройства, аналогично рассмотренному.

В режиме ручного управления возможно формирование управляющей команды оператором, проводящим отладку вручную. Причем возможны два способа формирования адресной части команды -- тактовый или циклический, которые могут быть заданы оператором с помощью тумблера блока 23 установки режимов. При тактовом способе адресная часть команды формируется следующим образом. Элемент 31 ручного формирования команды представляет собой 11-разрядный тумблерный регистр, десять разрядов которого отведены под код адреса, а один - под код информации. Код адреса с элемента 31 поступает на вход мультиплексора 30, а с его выхода на второй ип- (|)ормациониый вход мультиплексора 25 бло ка 24 приема команды. Код информациои- ного разряда формируется либо вручную тумблеоом элемента 31, либо формирователем 35 ,1искг)етиых сигналов. Оба эти сиг

5

0

5

П

нала поступают на вход элемента 32 ИЛИ, а с его выхода - на информационный вход мультиплексора 25 блока 24 приема команд. Синхросигнал в данном случае вырабатывается формирователем 28 синхросигнала при нажатии оператором соответствующей кнопки и поступает на информационный вход мультиплексора 25 блока 24 приема команд.

При циклическом способе формирования адресной части команды с выхода формирователя 28 синхросигналов на вход счетчика 29 импульсов поступают имг1ульсы определенной частоты, которые пересчитываются. Таким образом, на выходе счетчика 29 формируется адресная часть команды путем последовательного циклического перебора всех возможных комбинаций, которая затем через мультиплексор 30 юступает на вход мультиплексора 25 блока 24 приема ко.манд. В этом случае происходит ци.кли- ческий перебор всех адресов дешифратора 19 адреса. Код информационного разряда формируется аналогично описанно.му. Синхронизирующие импульсы формируются формирователем 28 и поступают на вход мультиплексора 25 блока 24 приема команд.

В этом же режиме ручного управления на входы модулей 39 и 4 ввода дискретных и аналоговых сигналов отлаживаемого управляющего комплекса могут быгь выданы дискретные или аналоговые сигналы соответствующими формирователями 33 и 34 блока 27 автономных режимов.

ВНИИИИ 5;iK;.:(:i2i( Фи.ииа. ; ГПП «11а-и Ит- i.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1672455A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство управления | 1989 |

|

SU1654820A1 |

| Устройство для сопряжения процессора с внешним устройством | 1988 |

|

SU1550524A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Система для отладки программ | 1987 |

|

SU1481774A1 |

| Устройство для отладки программ | 1985 |

|

SU1317444A2 |

| Имитатор сигналов для отладки специального программного обеспечения АСУ РСГ | |||

| Техническое описание ДИИТ, 40035,001 ТО (отчет), госрегистрация № 81084887 | |||

| Днепропетровск, 1981. |

Авторы

Даты

1986-06-15—Публикация

1984-05-24—Подача