водится при помощи первого регистра, цифроаналогового преобразователя и перестраиваемого фильтра, а ввод результатов обработки сигналов в устройство от ЦПОС - при помощи аналого- цифрового преобразователя и второго

1

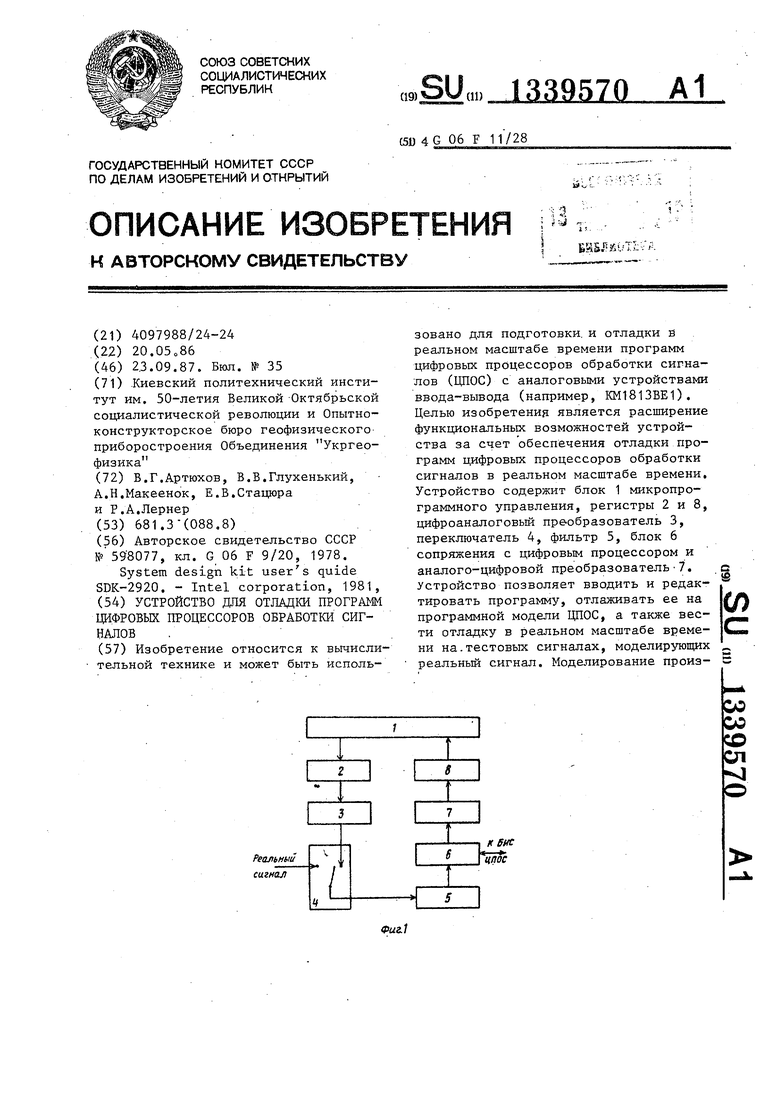

Изобретение относится к вычислительной технике и может быть использовано для подготовки .и отладки в реальном масштабе времени программ специализированных однокристальных БИС цифровых процессоров обработки сигналов (ЦПОС) с аналоговыми устройствами ввода-вывода.

Цель изобретения - расширение фун кциональных возможностей устройства за счет обеспечения отладки программ цифровых процессоров обработки сигналов в реальном масштабе времени.

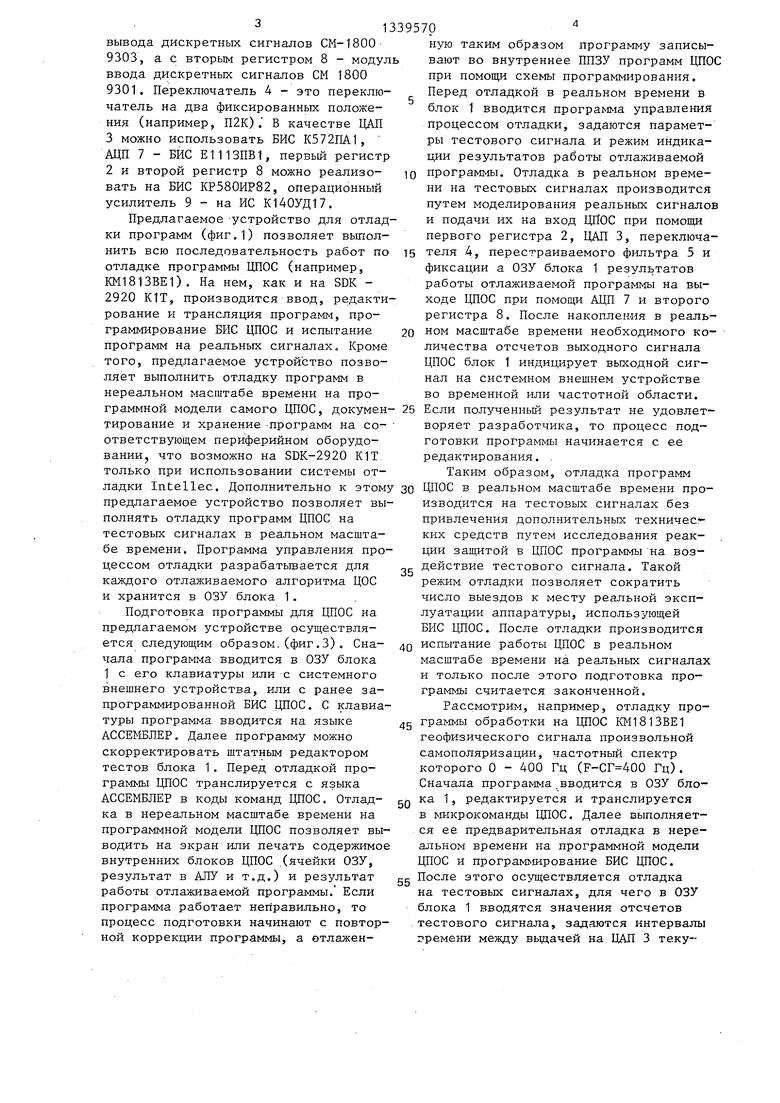

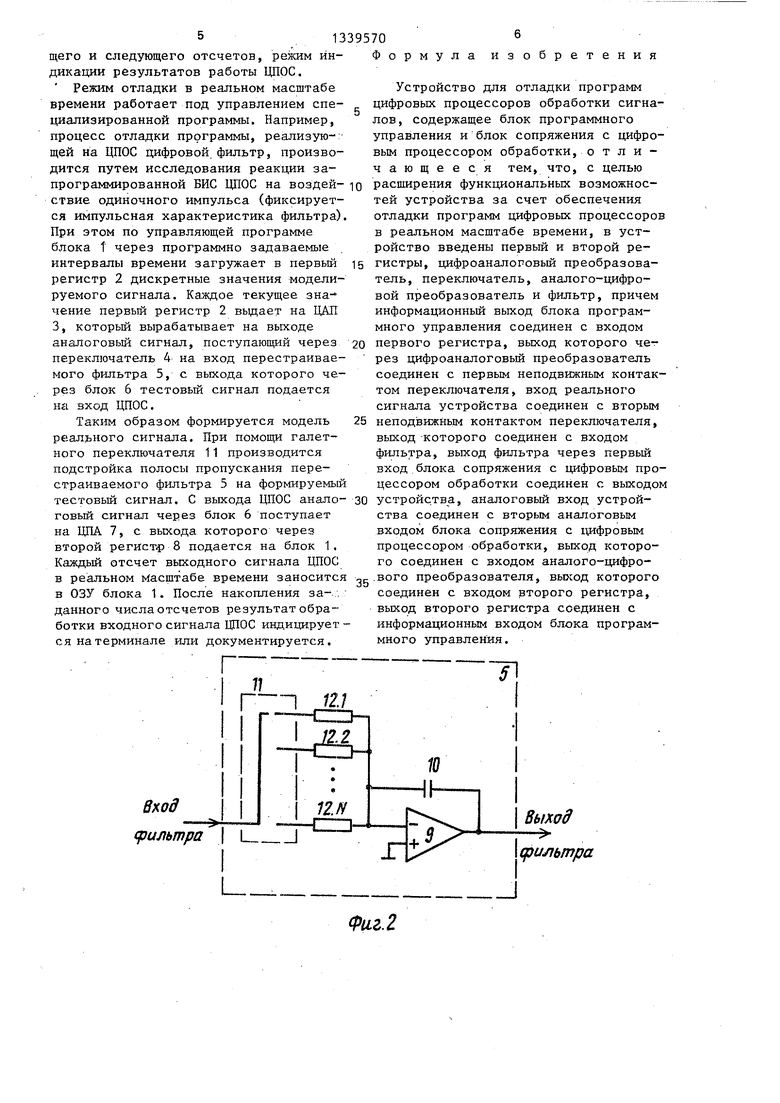

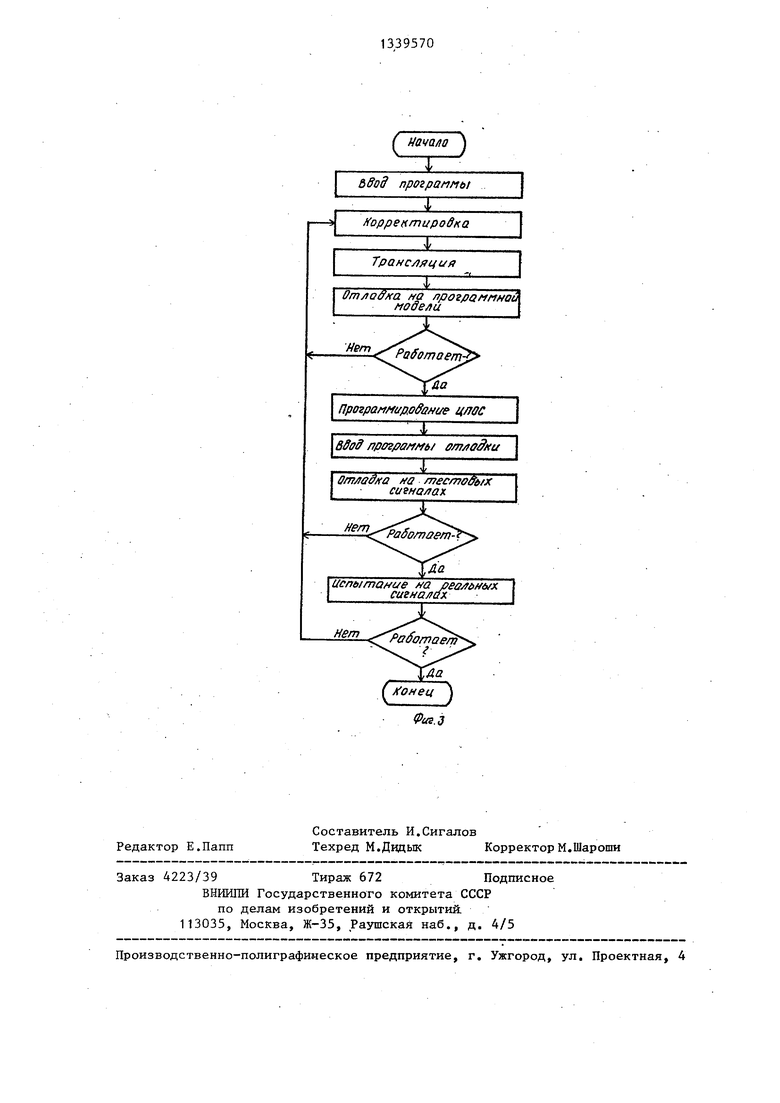

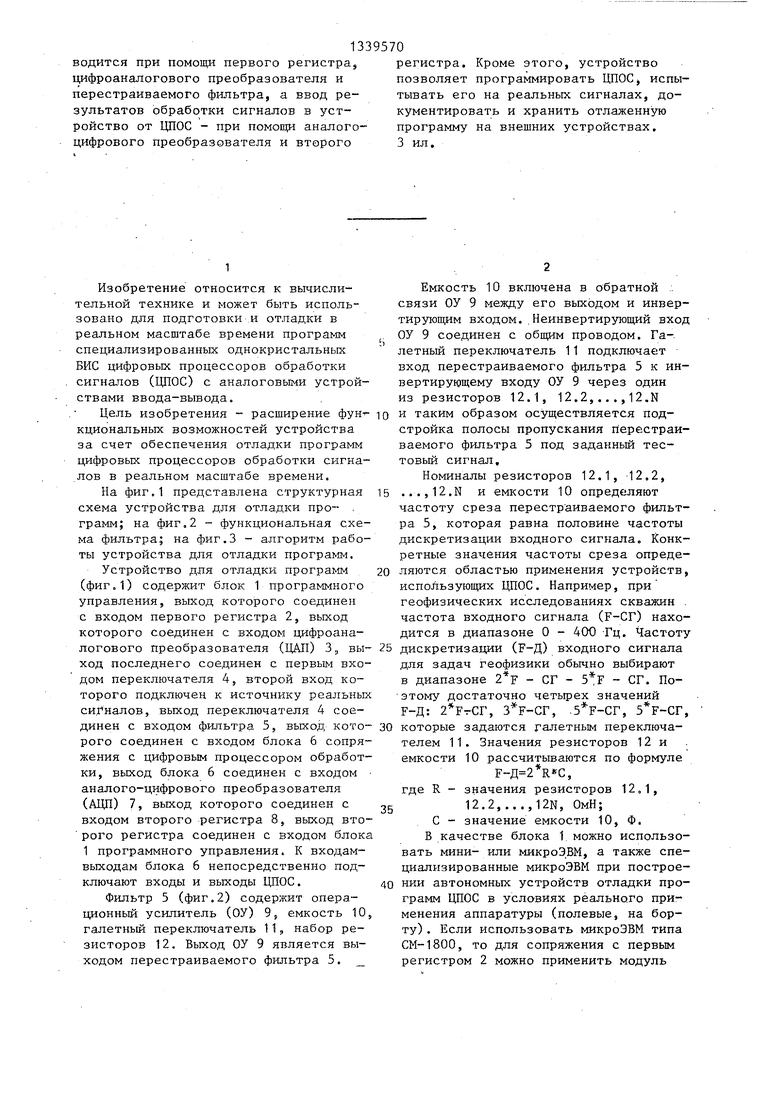

На фиг,1 представлена структурная схема устройства для отладки про- . грамм; на фиг.2 - функциональная схема фильтра; на фиг.З - алгоритм работы устройства для отладки программ.

Устройство для отладки программ (фиг.1) содержит блок 1 программного управления, выход которого соединен с входом первого регистра 2, выход которого соединен с входом цифроаналогового преобразователя (ЦАП) 3, вы- ход последнего соединен с первым входом переключателя 4, второй вход которого подключен к источнику реальных сигналов, выход переключателя 4 соединен с входом фильтра 5, выход кото- рого соединен с входом блока 6 сопряжения с цифровым процессором обработки, выход блока 6 соединен с входом аналого-цифрового преобразователя (АЦП) 7, выход которого соединен с входом второго регистра 8, выход вто- рого регистра соединен с входом блока 1 программного управления. К входам- выходам блока 6 непосредственно подключают входы и выходы ЦПОС.

Фильтр 5 (фиг,2) содержит операционный усилитель (ОУ) 9 емкость 10 галетный переключатель 11, набор резисторов 12. Выход ОУ 9 является выходом перестраиваемого фильтра 5.

регистра. Кроме этого, устройство позволяет программировать ЦПОС, испытывать его на реальных сигналах, документировать и хранить отлаженную программу на внешних устройствах, 3 ил.

Емкость 10 включена в обратной . связи ОУ 9 между его выходом и инвертирующим входом..Неинвертирующий вход ОУ 9 соединен с общим проводом. Га-, летный переключатель 11 подключает вход перестраиваемого фильтра 5 к инвертирующему входу ОУ 9 через один из резисторов 12.1, 12.2,.. .,12.N и таким образом осуществляется подстройка полосы пропускания перестраиваемого фильтра 5 под заданный тестовый сигнал.

Номиналы резисторов 12.1, -12.2, ...,12.N и емкости 10 определяют частоту среза перестраиваемого фильтра 5, которая равна половине частоты дискретизации входного сигнала. Конкретные значения ч.астоты среза определяются областью применения устройств, используюш х ЦПОС. Например, при геофизических исследованиях скважин , частота входного сигнала (F-СГ) находится в диапазоне О - 400 Тц, Частоту дискретизации (F-Д) входного сигнала для задач геофизики обычно выбирают в диапазоне - СГ - - СГ. По- этому достаточно четырех значений F-Д: , , ., , которые задаются галетным переключателем 11. Значения резисторов 12 и емкости 10 рассчитываются по формуле

, где R - значения резисторов 12,1,

12.2,...,12N, ОмН; С - значение емкости 10, Ф,

В качестве блока 1 можно использовать мини- или микроэвм, а также специализированные микроэвм при построении автономных устройств отладки программ ЦПОС в условиях реального применения аппаратуры (полевые, на борту) . Если использовать микроЭВМ типа СМ-1800, то для сопряжения с первым регистром 2 можно применить модуль

вывода дискретных сигналов СМ-1800 9303, а с вторым регистром 8 - модул ввода дискретных сигналов СМ 1800 9301. Переключатель 4 - это переключатель на два фиксированных положения (например, П2К) . В качестве ЦАП 3 можно использовать БИС К572ПА1, АЦП 7 - БИС Е1113ПВ1, первый регистр 2 и второй регистр 8 можно реализовать на БИС КР580ИР82, операционный усилитель 9 - на ИС К140УД17.

Предлагаемое -устройство для отладки программ (фиг,1) позволяет вьшол- нить всю последовательность работ по отладке программы ЦПОС (например, КМ1813ВЕ1). На нем, как и на SDK - 2920 KIT, производится ввод, редактирование и трансляция программ, программирование БИС ЦПОС и испытание программ на реальных сигналах. Кроме того, предлагаемое устройство позволяет выполнить отладку программ в нереальном масштабе времени на про35

40

граммной модели самого ЦПОС, докумен- 25 Если полученньш результат не удовлет- тирование и хранение программ на со- ответствующем периферийном оборудовании, что возможно на SDK-2920 К1Т только при использовании системы от ладки lutellec. Дополнительно к этому зо предлагаемое устройство позволяет выполнять отладку программ ЦПОС на тестовых сигналах в реальном масштабе времени. Программа управления процессом отладки разрабатьгоается для каждого отлаживаемого алгоритма ЦОС и хранится в ОЗУ блока 1.

Подготовка программы для ЦПОС на предлагаемом устройстве осуществляется следующим образом.(фиг.3). Сначала программа вводится в ОЗУ блока 1 с его клавиатуры или с системного внешнего устройства, или с ранее запрограммированной БИС ЦПОС. С клавиатуры программа вводится на языке АССЕЬКЛЕР. Далее программу можно скорректировать штатным редактором тестов блока 1, Перед отладкой программы ЦПОС транслируется с языка АССЕМБЛЕР в коды команд ЦПОС. Отладка в нереальном масштабе времени на программной модели ЦПОС позволяет выводить на экран или печать содержимое внутренних блоков ЦПОС (ячейки ОЗУ, результат в АЛУ и т.д.) и результат работы отлаживаемой программы. Если программа работает неправильно, то процесс подготовки начинают с повторной коррекции программы, а отлаженворяет разработчика, то процесс подготовки программы начинается с ее редактирования. .

Таким образом, отладка программ ЦПОС в реальном масштабе времени производится на тестовых сигналах без привлечения дополнительных технических средств путем исследования реакции защитой в ЦПОС программы на воздействие тестового сигнала. Такой режим отладки позволяет сократить число выездов к месту реальной эксплуатации аппаратуры, использующей БР1С ЦПОС. После отладки производится испытание работы ЦПОС в реальном масштабе времени на реальных сигналах и только после этого подготовка программы считается законченной.

Рассмотрим, например, отладку про- 45 граммы обработки на ЦПОС КМ1813ВЕ1 геофизического сигнала произвольной самополяризации, частотный спектр которого О - 400 Гц ( Гц). Сначала программа.вводится в ОЗУ блока 1, редактируется и транслируется в микрокоманды ЦПОС. Далее выполняется ее предварительная отладка в нереальном времени на программной модели ЦПОС и программирование БИС ЦПОС. После этого осуществляется отладка на тестовых сигналах, для чего в ОЗУ блока 1 вводятся значения отсчетов тестового сигнала, задаются интервалы : ремени между выдачей на ЦАП 3 теку50

55

ную таким образом программу записывают во внутреннее ППЗУ программ ЦПОС при помощи схемы программирования. Перед отладкой в реальном времени в блок 1 вводится программа управления процессом отладки, задаются параметры тестового сигнала и режим индикации результатов работы отлаживаемой

0 программы. Отладка в реальном времени на тестовых сигналах производится путем моделирования реальных сигналов и подачи их на вход ЦПОС при помощи первого регистра 2, ЦАП 3, переключа5 теля 4, перестраиваемого фильтра 5 и фиксации а ОЗУ блока 1 результатов работы отлаживаемой программы на выходе ЦПОС при помощи АЦП 7 и второго регистра 8. После накопления в реаль0 ном масштабе времени необходимого количества отсчетов выходного сигнала ЦПОС блок 1 индицирует выходной сигнал на системном внешнем устройстве во временной или частотной области.

35

0

25 Если полученньш результат не удовлет- зо

воряет разработчика, то процесс подготовки программы начинается с ее редактирования. .

Таким образом, отладка программ ЦПОС в реальном масштабе времени производится на тестовых сигналах без привлечения дополнительных технических средств путем исследования реакции защитой в ЦПОС программы на воздействие тестового сигнала. Такой режим отладки позволяет сократить число выездов к месту реальной эксплуатации аппаратуры, использующей БР1С ЦПОС. После отладки производится испытание работы ЦПОС в реальном масштабе времени на реальных сигналах и только после этого подготовка программы считается законченной.

Рассмотрим, например, отладку про- 5 граммы обработки на ЦПОС КМ1813ВЕ1 геофизического сигнала произвольной самополяризации, частотный спектр которого О - 400 Гц ( Гц). Сначала программа.вводится в ОЗУ блока 1, редактируется и транслируется в микрокоманды ЦПОС. Далее выполняется ее предварительная отладка в нереальном времени на программной модели ЦПОС и программирование БИС ЦПОС. После этого осуществляется отладка на тестовых сигналах, для чего в ОЗУ блока 1 вводятся значения отсчетов тестового сигнала, задаются интервалы : ремени между выдачей на ЦАП 3 теку0

5

щего и следующего отсчетов, режим индикации результатов работы ЦПОС.

Режим отладки в реальном масштабе времени работает под управлением специализированной программы. Например, процесс отладки программы, реализующей на ЦПОС цифровой фильтр, производится путем исследования реакции запрограммированной БИС ЦПОС на воздей- ю расширения функциональных возможносствие одиночного импульса (фиксируется импульсная характеристика фильтра). При этом по управляющей программе блока Т через программно задаваемые интервалы времени загружает в первый регистр 2 дискретные значения моделируемого сигнала. Каждое текущее значение первый регистр 2 выдает на ЦАП 3, который вырабатывает на выходе аналоговый сигнал, поступающий через переключатель 4 на вход перестраиваемого фильтра 5, с выхода которого через блок 6 тестовый сигнал подается на вход ЦПОС.

Таким образом формируется модель реального сигнала. При помощи галет- ного переключателя 11 производится подстройка полосы пропускания перестраиваемого фильтра 5 на формируемый тестовый сигнал. С выхода ЦПОС аналоговый сигнал через блок 6 поступает на ЦПА 7, с выхода которого через второй регистр 8 подается на блок 1, Каждый отсчет выходного сигнала ЦПОС в реальном масштабе времени заносится в ОЗУ блока 1. После накопления за-.: данного числа отсчетов результат обработки входного сигнала ЦПОС индицирует - ся на терминале или документируется.

тей устройства за счет обеспечения отладки программ цифровых процессоров в реальном масштабе времени, в устройство введены первый и второй ре15 гистры, цифроаналоговый преобразователь, переключатель, аналого-цифровой преобразователь и фильтр, причем информационный выход блока программного управления соединен с входом

20 первого регистра, выход которого че- рез цифроаналоговый преобразователь соединен с первым неподвижным контактом переключателя, вход реального сигнала устройства соединен с вторым

25 неподвижным контактом переключателя, выход -которого соединен с входом фильтра, выход фильтра через первый вход блока сопряжения с цифровьм процессором обработки соединен с выходом

30 устройства, аналоговый вход устройства соединен с вторым аналоговым входом блока сопряжения с 1щфровьм процессором обработки, выход которого соединен с входом аналого-цифро j-.Boro преобразователя, вьпсод которого соединен с входом второго регистра, выход второго регистра соединен с информационным входом блока программного управления.

fpuz.2

Формула изобретения

Устройство для отладки программ цифровых процессоров обработки сигналов , содержащее блок программного управления и блок сопряжения с цифровым процессором обработки, о т л и - чающееся тем, что, с целью

тей устройства за счет обеспечения отладки программ цифровых процессоров в реальном масштабе времени, в устройство введены первый и второй регистры, цифроаналоговый преобразователь, переключатель, аналого-цифровой преобразователь и фильтр, причем информационный выход блока программного управления соединен с входом

первого регистра, выход которого че- рез цифроаналоговый преобразователь соединен с первым неподвижным контактом переключателя, вход реального сигнала устройства соединен с вторым

неподвижным контактом переключателя, выход -которого соединен с входом фильтра, выход фильтра через первый вход блока сопряжения с цифровьм процессором обработки соединен с выходом

устройства, аналоговый вход устройства соединен с вторым аналоговым входом блока сопряжения с 1щфровьм процессором обработки, выход которого соединен с входом аналого-цифро.Boro преобразователя, вьпсод которого соединен с входом второго регистра, выход второго регистра соединен с информационным входом блока программного управления.

ffm/joff/fa на програмпнаи модели

(: QSornQmi

Программир(0&ание цлос

В8од npiKffaffft6f о/п/ю ки

(a ffd mecmoSdiX cusHQ/rax

/ Нича/io Л

5 Sod программы

/{орректировка

Транс/)

испытание a oeaMffu/x. сигналах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ цифровых процессоров обработки аналоговых сигналов | 1988 |

|

SU1640696A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| ТЕХНОЛОГИЧЕСКАЯ УВМ | 2013 |

|

RU2563139C2 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| БОРТОВАЯ ИНФОРМАЦИОННАЯ СИСТЕМА | 2009 |

|

RU2402439C1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| КОСМИЧЕСКИЙ РАДИОЛОКАТОР С СИНТЕЗИРОВАННОЙ АПЕРТУРОЙ, ФОРМИРУЮЩИЙ ИЗОБРАЖЕНИЕ В РЕАЛЬНОМ ВРЕМЕНИ | 1999 |

|

RU2158008C1 |

| Устройство для прерывания при отладке программ | 1984 |

|

SU1171799A2 |

Изобретение относится к вычислительной технике и может быть испольРеильнт сигнал зовано для подготовки, и отладки в реальном масштабе времени программ цифровых процессоров обработки сигналов (ЦПОС) с аналоговыми устройствами ввода-вывода (например, КМ1813ВЕ1). Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения отладки программ цифровых процессоров обработки сигналов в реальном масштабе времени. Устройство содержит блок 1 микропрограммного управления, регистры 2 и 8, цифроаналоговый преобразователь 3, переключатель 4, фильтр 5, блок 6 сопряжения с цифровым процессором и аналого-цифровой преобразователь7. Устройство позволяет вводить и редактировать программу, отлаживать ее на программной модели ЦПОС, а также вести отладку в реальном масштабе времени на.тестовых сигналах, моделирующих реальный сигнал. Моделирование произ(Л С СХ 00 СО ел 1

Редактор Е.Папп

Составитель И.Сигалов

Техред М.Дидык Корректор М.Шароши

Заказ 4223/39Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфинеское предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для отладки программ | 1974 |

|

SU598077A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ изготовления электрических нагревательных приборов | 1924 |

|

SU2920A1 |

| - Intel corporation, 1981, | |||

Авторы

Даты

1987-09-23—Публикация

1986-05-20—Подача