Изобретение относится к вычислительной технике и может быть использовано для функционального аналого- цифрового преобразования с повышенной точностью и широкими функциональными возможностями, а также для сопряжения вычислительных машин и микропроцессоров с источником аналоговой информации.

Цель изобретения - расширение функциональных возможностей за счет обеспечения дополнительных функций

линейного преобразования сигнала и нелинейного преобразования сигнала по закону логарифма с другим осйо- данием.

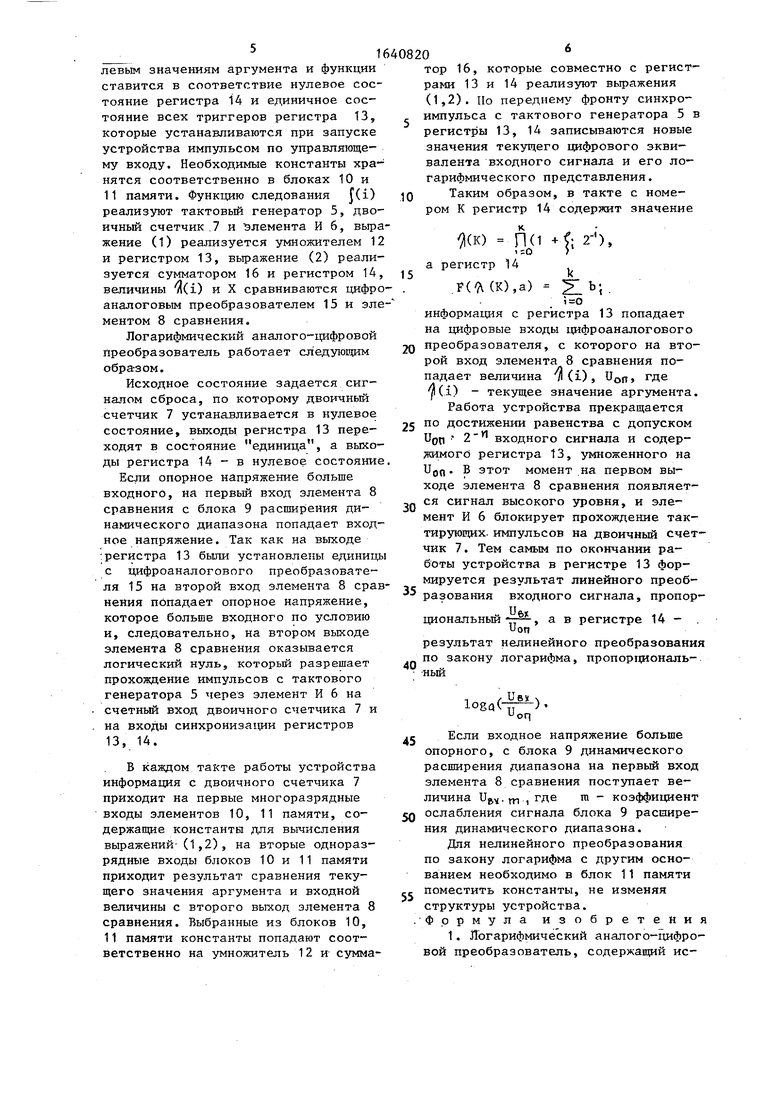

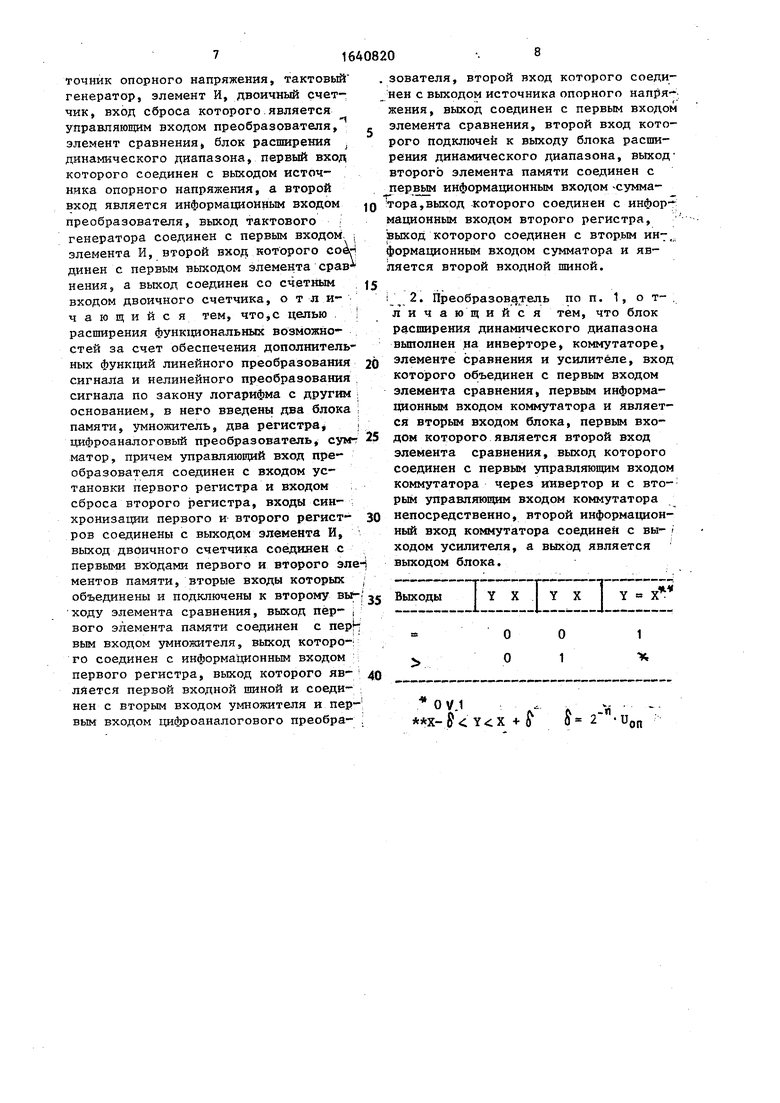

На фиг. 1 изображена функциональная схема логарифмического аналого- цифрового преобразователя} на фиг.2 приведен пример реализации элемента сравненияJ на фиг. 3 - пример выполнения блока расширения динамического диапазона.

316

Логарифмический аналого-цифровой преобразователь (АЦП) содержит управляющий вход 1, первую выходную шину 2, информационный вход 3, ис- точник 4 опорного напряжения, тактовый генератор 5, элемент И 6, двоичный счетчик 7, элемент 8 сравнения, блок 9 расширения динамического диапазона, два блока 10, 11 памяти, умножитель 12, два регистра 13, 14-, цифроаналоговый преобразователь 15, сумматор 16, вторую выходную шину 17. Регистры 13, 14 являются синхронными элементами, запись в которые осуществляется по переднему фронту синхронизирующего импульса.

Элементы сравнения (фиг,2) содержат первый и второй аналоговые сумматоры 18, 19, первый и второй компараторы 20, 21 и источник 22 напряжения смещения.

В нижеприведенной таблице указаны состояния выходов устройства в сравнении в зависимости от величины входных сигналов.

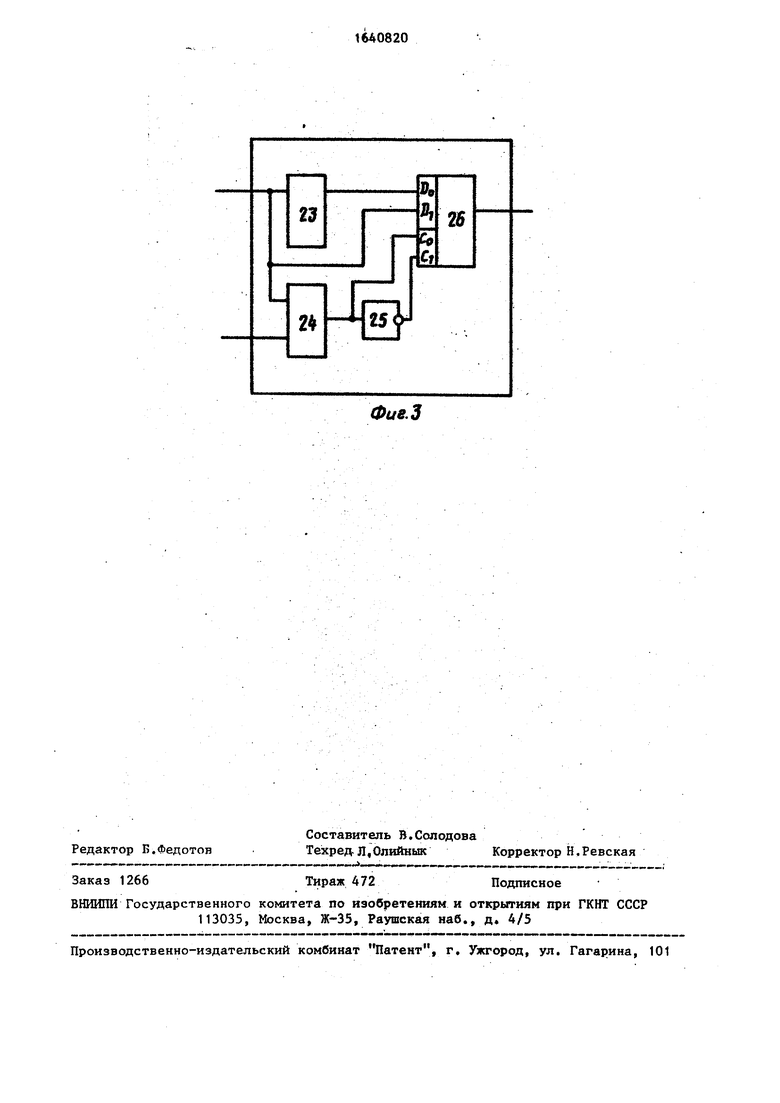

г Блок 9 расширения динамического диапазона содержит усилитель 23, второй элемент 24 сравнения, инвертор 25, коммутатор 26.

Работа устройства основана на рекурсивном способе описания реализуемых функций и заключается в вычислении по рекуррентным соотношениям значений функций.

Логарифмическая функция

f(x,a) logax ,

где хЈ(0;1), ах - значение аргумента,

может быть представлена с помощью базы и правил композиции (рекурсии), задаваемых в виде следующей схемы примитивной рекурсии:

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Цифровой логарифмический преобразователь | 1979 |

|

SU881741A1 |

| Цифровое логарифмическое устройство | 1983 |

|

SU1101819A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

| Логарифмический преобразователь | 1982 |

|

SU1037248A1 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГОВЫХ СИГНАЛОВ В ИМПУЛЬСНУЮ ПОСЛЕДОВАТЕЛЬНОСТЬ, МОДУЛИРОВАННУЮ ПО ВРЕМЕНИ | 2011 |

|

RU2471287C1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ СОСТОЯНИЯ ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 2014 |

|

RU2543957C1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1612374A1 |

| Вычислительное устройство и запоминающий масштабно-суммирующий блок | 1980 |

|

SU1043670A1 |

Изобретение относится к вычис-1 лителъной технике и может быть использовано для функционального аналого-цифрового преобразования с повышенной точностью и широкими функциональными возможностями, а также для сопряжения вычислительных машш и микропроцессоров с источником аналоговой информации. Цель изобретения - расширение функциональных возможностей. Преобразователь позволяет получить наряду с логарифмическим линейное преобразование сигнала, а также обеспечивает простоту перенастройки преобразователя при необходимости нелинейного преобразования по закону логарифма с другим основанием. Изобретение предусматривает использование рекурсивного способа выполнения преобразования. Цель изобретения дости- стигается тем, что в устройство, содержащее управляющий вход 1, первую выходную шину 2 устройства, информационный вход 3, источник опорного напряжения, тактовый генератор 5, элемент И 6, двоичный счетчик 7, элемент 8 сравнения, блок 9 расширения динамического диапазона, введены два блока 10, 11 памяти, умножитель 12, два регистра 13, 14, цифроаналоговый преобразователь 15, сумматор 16, вторая выходная шина 17. 1 з.п.ф-лы, 3 ил. (Л сп Ј О 00 ГС

F (fl(0),a) - R(a)/д(0) гг

Г(Ш-И).а) - Mfl)i),a, F(fl(i),a)) fl(i+1) G(i),fl(i)

i

Для аргументов х, представленных

в двоичной системе счисления, выбедля получения рекуррентных соотношений нужно выбрать конкретные функции F, h, нумерацию , G и j функцию следования J(i). Выберем нумерацию

11(0) 1

fti+l) fl(i)

и функцию следования; J (i) i+1 для определения Ц(i) осуществим тождественное преобразование для функции logq(fl(Ј+1)) и получим:

loga(fl(i+1)) - Iog0fl(i) + logqd +

Выберем W(i) такую, чтобы loga(1-« . (i)

30

рем

ci

К . И-1 1

35

Представим аргументы X произведением

h

П(1 --(

-(.

где

40

1:-t

Г 2 ).

если х (i) если х Ј (i) j

(i)

bj, где bj - известное

n - разрядность представления

чисел.

Для вычисления логарифмической 45 Функции используют следующие рекуррентные соотношения:

() 1

jF(fl(0),a) 0

значение для каждого i, положим 4(i) с;-(i). Тогда loga(1 + 1 Ij/fi1)

+ Jffi) 10g« (1+C|) b

При такой Ч/ (i) приходим к следующем нумерации:

/fro) 1

ifl(i-M) - fl(i)1+c,-)

в двоичной системе счисления

рем

ci

К . И-1 1

Представим аргументы X произведением

h

П(1 --(

-(.

где

1:-t

Г 2 ).

если х (i) если х Ј (i) j

n - разрядность представления

чисел.

Для вычисления логарифмической Функции используют следующие рекуррентные соотношения:

() 1

jF(fl(0),a) 0

fl(i+1) -IKD d+c;) (1)

Ua(i+1),a) F(Mi)/, (2)

где с;

-.

2, если X(i) если х $Ш

Данные выражения интерпретируются аппаратурой следующим образом. Нулевым значениям аргумента и функции ставится в соответствие нулевое состояние регистра 14 и единичное состояние всех триггеров регистра 13, которые устанавливаются при запуске устройства импульсом по управляющему входу. Необходимые константы хранятся соответственно в блоках 10 и 11 памяти. Функцию следования J(i) реализуют тактовый генератор 5, двоичный счетчик 7 и элемента И 6, выражение (1) реализуется умножителем 12 и регистром 13, выражение (2) реализуется сумматором 16 и регистром 14, величины ж) и X сравниваются цифро аналоговым преобразователем 15 и эле ментом 8 сравнения.

Логарифмический аналого-цифровой преобразователь работает следующим образом.

Исходное состояние задается сигналом сброса, по которому двоичный счетчик 7 устанавливается в нулевое состояние, выходы регистра 13 переходят в состояние единица, а выходы регистра 14 - в нулевое состояние

Если опорное напряжение больше входного, на первый вход элемента 8 сравнения с блока 9 расширения динамического диапазона попадает входное напряжение. Так как на выходе регистра 13 были установлены единицы с цифроаналогового преобразователя 15 на второй вход элемента 8 сравнения попадает опорное напряжение, которое больше входного по условию и, следовательно, на втором выходе элемента 8 сравнения оказывается логический нуль, который разрешает прохождение импульсов с тактового генератора 5 через элемент И 6 на счетный вход двоичного счетчика 7 и на входы синхронизации регистров 13, 14.

В каждом такте работы устройства информация с двоичного счетчика 7 приходит на первые многоразрядные входы элементов 10, 11 памяти, содержащие константы для вычисления выражений (1,2), на вторые одноразрядные входы блоков 10 и 11 памяти приходит результат сравнения текущего значения аргумента и входной величины с второго выход элемента 8 сравнения. Выбранные из блоков 10, 11 памяти константы попадают соответственно на умножитель 12 и сумма

тор 16, которые совместно с регистрами 13 и 14 реализуют выражения (1,2). Но переднему фронту синхроимпульса с тактового генератора 5 в регистры 13, 14 записываются новые значения текущего цифрового эквивалента входного сигнала и его логарифмического представления.

Таким образом, в такте с номером К регистр 14 содержит значение

5

0

5

0

fl(K - а регистр

к

По

14

2-Х

F(ft (К),а) 21 Ъ;

)о

информация с регистра 13 попадает на цифровые входы цифроаналогового Q преобразователя, с которого на второй вход элемента 8 сравнения попадает величина i (i) , Uon, где y(i) - текущее значение аргумента.

Работа устройства прекращается 5 по достижении равенства с допуском и0п входного сигнала и содержимого регистра 13, умноженного на Uon. В этот момент на первом выходе элемента 8 сравнения появляется сигнал высокого уровня, и элемент И 6 блокирует прохождение тактирующих импульсов на двоичный счетчик 7. Тем самым по окончании работы устройства в регистре 13 формируется результат линейного преоб- входного сигнала, И Uon

результат нелинейного преобразования по закону логарифма, пропорционапьразованияциональный

пропор- а в регистре 14 ный

.

и

oq

Если входное напряжение больше опорного, с блока 9 динамического расширения диапазона на первый вход элемента 8 сравнения поступает величина Uftv m , где га - коэффициент ослабления сигнала блока 9 распире- ния динамического диапазона.

Для нелинейного преобразования по закону логарифма с другим основанием необходимо в блок 11 памяти поместить константы, не изменяя структуры устройства. Формула изобретения

1 2. Преобразователь по п. 1, отличающийся тем, что блок расширения динамического диапазона выполнен на инверторе, коммутаторе, элементе сравнения и усилителе, вход которого объединен с первым входом элемента сравнения, первым информационным входом коммутатора и является вторым входом блока, первым входом которого является второй вход элемента сравнения, выход которого соединен с первым управляющим входом коммутатора через инвертор и с вторым управляющим входом коммутатора непосредственно, второй информационный вход коммутатора соединен с вы- ходом усилителя, а выход является выходом блока.

I

8

PHin

z/

2r

#

Z/

W

9/

W

23

2k

Редактор Б.Федотов

Составитель В.Солодова

Техред-Л,Олийнык Корректор Н.Ревская

Заказ 1266

Тираж 472

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

l Л,

25

25JH

Фие.З

Подписное

| Патент США № 3678505, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Логарифмический преобразователь | 1978 |

|

SU769562A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-07—Публикация

1989-04-05—Подача