(54) ЦИФЮВОЙ ЛОГАРИФМИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логарифма | 1979 |

|

SU783798A1 |

| Логарифмический преобразователь | 1981 |

|

SU959073A1 |

| Процессор для корреляционного анализа | 1978 |

|

SU744601A1 |

| Функциональный преобразователь | 1983 |

|

SU1107131A1 |

| Цифровой генератор логарифмической функции | 1980 |

|

SU942006A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Логарифмический аналого-цифровой преобразователь | 1979 |

|

SU790294A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2513683C1 |

| Многоканальный статистический анализатор | 1977 |

|

SU732890A1 |

Г

Изобретеиие относится к цифровой вычислительной технике и может быт использовано при построении специализированных вычислителей, информационно-измерительных систем, цифровых фильтров и гибридных функциональных преобразователей.

Известно устройство содержащее сдвигающий регистр, вычитающий счетчик, регистр характеристики, генератор тактовых импульсов, два триггера, схему сравнения, три схемы И и схему ИЛИ 1.

Недостатком известного устройства является низкая точность преобразоващш нормализованных чисел так как оно предназначено в основном для получения двоичных логарифмов целых чисел.

Наиболее близким по технической сущности к предлагаемому является двоичное арифметическое устройство, которое содержит первый и второй регистры, входы которых подключены к входной щине и к выходу сумматора, а их выходы соединены с первым входом сдвигового регистра, первым входом сумматора и уходом счетчика сдвигов, выход

которого подключен к регистру параметра, выход которого соединен с первыми входами двух схем И и схемы сравнения, второй вход которой соединен с выходом регистргР хранения, первый ее вь1ход подключен к первому входу третьей схемы И, второй - ко вторым входам первых двух схем И, выход одаой из которых подключен ко второму входу сдвигового регистра, а выход второй схемы И соединен со входом запомина|ощего устройства, выход которого соединен с выходом сдвигового регистра и вторым входом сумматора, выход которого подключен к первому своему входу и к второму входу третьей схемы И, выход которой соединен с выходной щиной устройства 2.

Однако этому способу присуще ограниченное быстродействие, которое зависит от длины преобразуемых чисел п обусловлено последовательной природой получения разрядов функции.

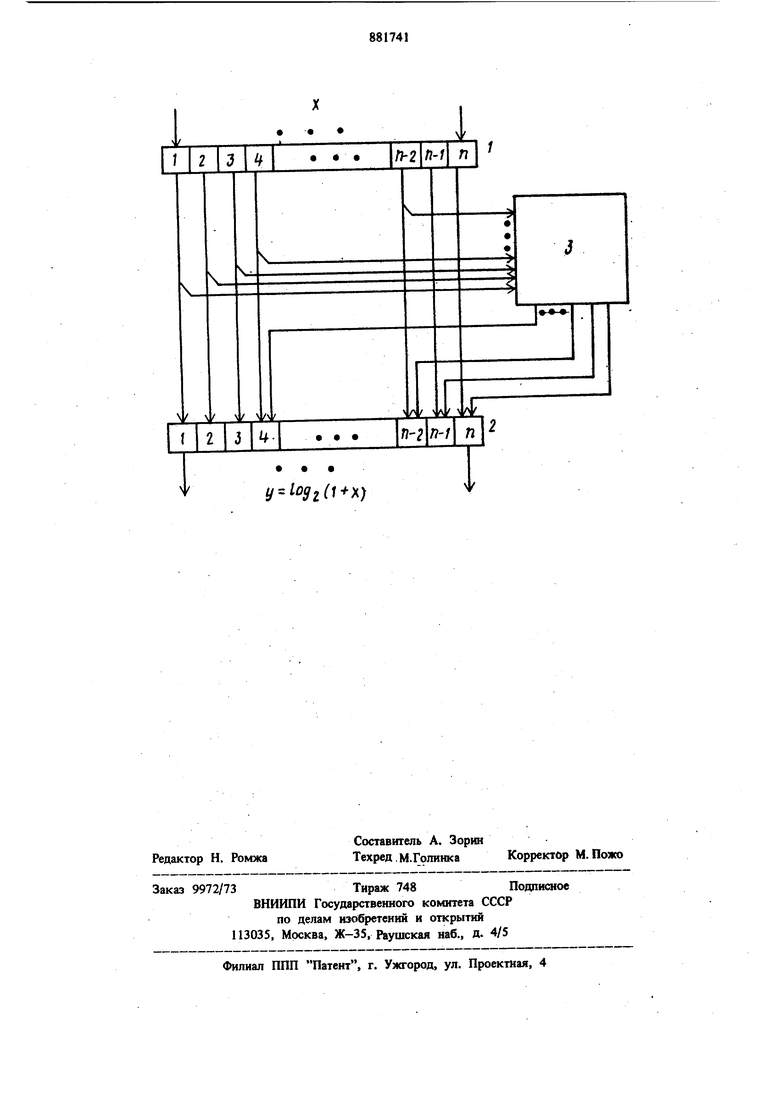

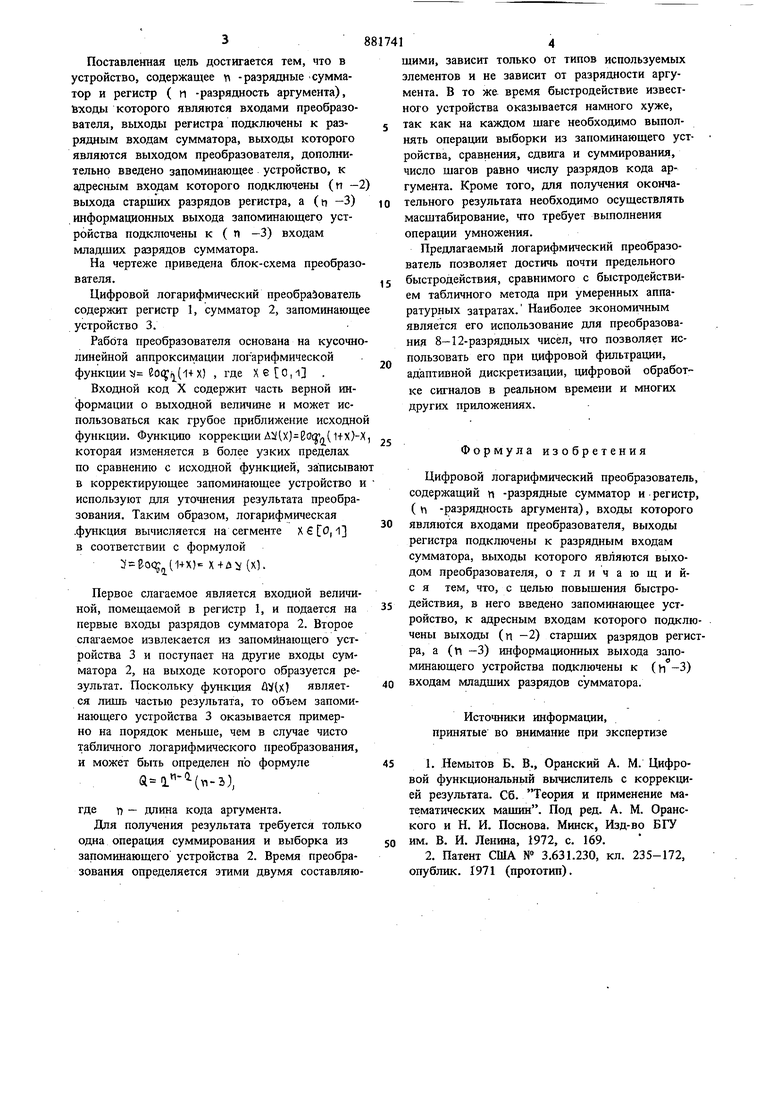

Цель изобретения - повышение быстродействия устройства для вычисления двоичных логарифмов нормализованных чисел. Поставленная цель достигается тем, что в устройство, содержащее п -разрядные сумматор и регистр ( п -разрядность аргумента), ьходы которого являются входами преобразователя, выходы регистра подключены к разрядным входам сумматора, выходы которого являются выходом преобразователя, дополнительно введено запоминающее устройство, к адресным входам которого подключены (п - выхода старших разрядов регистра, а (ц -3) информационных выхода запоминающего устройства подключены к ( п -3) входам младших разрядов сумматора. На чертеже приведена блок-схема преобразо вателя. Цифровой логарифмический преобразователь содерясит регистр 1, сумматор 2, запоминающе устройство 3. Работа преобразователя основана на кусочно линейной аппроксимации логарифмической функции ; eo(yjj(l+X) , где ,i . Входной код X содержит часть верной информации о выходной величине и может использоваться как грубое приближение исходно функции. Функцию коррекцииAiilX)EO(y,j,(IfХ)которая изменяется в более узких пределах по сравнению с исходной функцией, записываю в корректирующее запоминающее устройство и используют для уточнения результата преобразования. Таким образом, логарифмическая .функция вычисляется на сегменте ,1 в соответствии с формулой () х+л: (хь Первое слагаемое является входной величиной, помещаемой в регистр 1, и подается на первые входы разрядов сумматора 2. Второе слагаемое извлекается из запоминающего устройства 3 и поступает на другие входы сумматора 2, на выходе которого образуется результат. Поскольку функция UV(X) является лишь частью результата, то объем запоминающего устройства 3 оказывается примерно на порядок меньше, чем в случае чисто табличного логарифмического преобразования, и может быть определен по формуле ((fl-5), где Т - длина кода аргумента. Для получения результата требуется только одна операция суммирования и выборка из запоминающего устройства 2. Время преобразования определяется этими двумя составляю4ими, зависит только от типов используемых лементов и не зависит от разрядности аргумента. В то же время быстродействие известого устройства оказывается намного хуже, так как на каждом щаге необходимо выполнять операции выборки из запоминающего устройства, сравнения, сдвига и суммирования, число шагов равно числу разрядов кода аргумента. Кроме того, для получения окончательного результата необходимо осуществлять масштабирование, что требует вьшолнения операции умножения. Предлагаемый логарифмический преобразователь позволяет достичь почти предельного быстродействия, сравнимого с быстродействием табличного метода при умеренных аппаратурных затратах. Наиболее экономичным является его использование для преобразования 8-12-разрядных чисел, что позволяет использовать его цри цифровой фильтрации, адаптивной дискретизации, цифровой обработке сигналов в реальном времени и многих других приложениях. Формула изобретения Цифровой логарифмический преобразователь, содержащий п -разрядные сумматор и регистр, ( -разрядность аргумента), входы которого являются входами преобразователя, выходы регистра подключены к разрядным входам сумматора, выходы которого являются выходом преобразователя, отличающийс я тем, что, с целью повыщення быстродействия, в него введено запоминающее устройство, к адресным входам которого подключены выходы (п -2) старщих разрядов регистра, а (п -3) информационных выхода запоминающего устройства подключены к (н-З) входам младших разрядов сумматора. Источники информации, принятые во внимание при экспертизе 1.Немытов Б. В,, Оранский А. М. Цифровой функциональньш вычислитель с коррекцией результата. Сб. Теория и применение математических машин. Под ред. А. М. Оранского и Н. И. Поснова. Минск, Изд-во Б ГУ им. В. И. Ленина, 1972, с. 169. 2.Патент США № 3.631.230, кл. 235-172, опублик. 1971 (прототип).

1

Т

У - logi()()

Авторы

Даты

1981-11-15—Публикация

1979-12-17—Подача