(21)4674521/24

(22)06„04„89

(46) 30,04.91. Бкш. № 16

(71)Московский энергетический институт

(72)И.В.Огнев, О.В.Исаев и С.П.Вель- макин

(53)681.327.66 (088„8)

(56)Авторское свидетельство СССР 1159067, кл. G 11 С 17/00, 1983.

Авторское свидетельство СССР 1536443, кл. G 11 С 17/00, 1988.

(54)УСТРОЙСТВО ДЛЯ ПОДМЕНЫ ИНФОРМАЦИИ В ПОСТОЯННОЙ ПАМЯТИ

(57)Изобретение относится к вычислительной технике и может быть использовало для многократной коррек7

ции программы или исправления ошибок в постоянной памяти. Целью изобретения является повышение надежности постоянной памяти за счет выполнения повторных двойных, тройных и т.д. подмен информации в дефектных ячейках в режиме произвольной подмены. Для достижения этой цели в устройство введены Ы-1 дополнительных блоков памяти 8 резервных слов (N - кратность подмены) и преобразователь 10 кода кратности подмены, код на выходе которого называет, с какого из блоков постоянной памяти ос--- НОРКОЙ 27 или памяти подмены 2, 8 ,8,. „ .,8ц., , следует считывать информацию 1 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подмены информации в постоянной памяти | 1988 |

|

SU1536443A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для сортировки информации | 1987 |

|

SU1509871A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство сравнения чисел с допусками | 1987 |

|

SU1509870A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Запоминающее устройство | 1988 |

|

SU1608746A1 |

Од -U

СП

СО

со

00

Изобретение относится к вы испи- тельной технике и может быть использовано для коррекции программы или справления ошибок в постоянной паяти.

Целью изобретения является повыение надежности постоянной памяти путем обеспечения возможности выполнения повторных (двойных, тройных и т«д„) подмен ошибочной информации в ячейках постоянной памяти.

На чертеже представлена схема устройства для подмены информации в постоянной памяти.

Устройство содержит блок 1 памяти адресов страниц подмены, блок 2 паяти резервных слов, блок 3 памяти признаков адресов подмены, блок 4 выборки, мультиплексор 5, блок 6 сравнения, элемент И 7, дополнительные блоки 8 ,. о. , памяти резервных слов, входы 9,..., записи дополнительных блоков, преобразователь 10 кода, адресные входы первой 11 и второй 12 групп устройства, входы ре- яима работы 13 и обращения 14, инормационные выходы первой 15, втоой 161,... и N-й групп, выходы признаков подмены первой 17 второй 18 групп, информационные входы первой 19, второй 20 и третьей 21 групп, вход 22 выборки, вход 23 г записи, вход 24 выбора направления передачи адреса страниц и выходы 25 выбора направления передачи данных устройства.

На чертеже также показана схема включения устройства в систему памяти, содержащая блок 26 записи, основную постоянную память 27, коммутатор 28 с выходами 29. Блок 26 записи обеспечивает управление занесением в устройство подмены резервных слов и имеет выход 30 признака переполнения .

Работа устройства рассмотрена для случая трехкратной подмены информации по одному и тому же адресу под- мены (N 3). В этом случае число дополнительных блоков равно 2, количество выходов преобразователя 10 равно log(N-t-l) 2

Устройство для подмены информации в Постоянной памяти работает в двух режимах: записи и считывания (основной режим). В исходном состоянии вое ячейки блоков 1, 2, 3, 84, 8а памяти содержат логические нули.

Принят работы устройства рассмотрим на примере основной памяти емкостью 128К 16-разрядных слов.

Все адресное пространство основной памяти разбивается на 2048 страниц. Номер страницы -это код старших разрядов адреса А -Анб. В результате информационная емкость блока 1

памяти равна (г разрядов адреса ячеек в блоках памяти 2, 3, 8х 8 Ј н 3 разряда - соответственно признаки одиночной, двойной и тройной подмены), блока 2 памяти и допол5 нительных блоков 8 и 8% памяти 2КН6 (хранение резервных слов), блока 3 - Кх14 (11 разрядов для хранения старших разрядов адреса обращения Ag-Al6 н 1 г ряда - признаки

0 подмены). Клоки 3, 2, 8д, 8 памяти распиваются на 32 страницы (старшие разряды адреса ,0 с мультиплексора 5) по 64 слова (младшие разряды адреса А с входов 11).

5В режиме записи, задаваемом нулевым сигналом на входе 13, адрес подмены поступает на входы 11 (А0-А) и 12 () устройства и по сигналу 22 выборки чз блока 26 записи, трансо nnpvevioMv через блок 4 выборки, осуществляется чтение из блока 1 памяти. В зависимости от результата чтения бток 76 загиси реализует далее один из шести возможных алгоритмов

51 Отсутствие признаков подмены

в блоье 1 памяти по адресу А,-А „при числе задействованных страниц не более 32 (количество задействованных ст страниц в блоках 2 н 3 памяти подсчи

0 тывается блоком 26 записи). В этом случае последовательно осуществляются следуюгше операции:

а)запись единичного признака и состояния счетчика, содержащегося в

5 блоке 26 записи, в блок 1 памяти по адресу , по сигналам 23 и 24;

б)прибавление единицы в счетчик блока записи;

в)чтение из блока 1 памяти по ад- 0 Ресу по сигналу 22 выборки;

г)запись в блоки 2 и 3 памяти по адресу (Л0-А5, Bg-B|0) данных подмены блок 2 памяти), признака одиночной подмены и разрядов адреса

5 (блок 3 памяти) по сигналам 22 и 23, причем разряды адреса Bfi-B10 передаются на входы блоков 2 и 3 памяти через мультиплексор 5 (сигнал 24 равен нулю)

51

2„ Наличие признака одиночной подмены в блоке 1 памяти по адресу Аб- А jg, отсутствие признака одиночной подмены в блоке 3 памяти, при числе задействованных страниц не более 32. В этом случае выполняется только описанный выше пункт г.

Таким образом, если каждый последующий адрес подмены в разрядах А$-А fg не совпадает ни с одним из предыдущих, то для него открывается новая страница в Злоках 2 и 3 памяти

При переполнении счетчика в блоке 26 записи после считывания из блока 1 памяти по адресу () очередной подмены возможны следующие алгоритмы.

4„ Отсутствие одиночного признака подмены в блоке 1 памяти по адресу () при числе задействованных страниц более 32. В этом случае осуществляется подбор свободной ячейки в блоках 2 и 3 памяти для размещения очередного адреса.

Подбор выполняется следующим образом.

t а) переключение мультиплексора 5 по входу 24 на передачу адреса на выходы блоков 2 и 3 памяти из блока записи;

б)чтение из блока 3 памяти по адресу (A0-Ag., Bg- Bf0 );

в)если по этому адресу в блоке

3 памяти отсутствует признак очередной подмены, мультиплексор 5 переводится в режим передачи с выходов блока 1 памяти и последовательно выполняются пункты а, в, г алгоритма 1, если по адресу (Лд-А, В6-В1О) в блоке 3 памяти хранится одиночный

0

998

0

5

0

5

0

5

0

5

6

признак подмени (т.е, эта ячейка уже занята), то увеличивается на единицу содержимое счетчика в блоке 26 записи и осуществляется переход к пункту б рассматриваемого алгоритма.

Инкрементирование счетчика в блоке 26 записи продолжается до тех пор, пока не будет найдена свободная ячейка в одной из страниц. Если этого не произошло, то на выходе 30 устанавливается признак переполнения устройства.

Это свидетельствует о том, что одиночная подмена уже производилась.,

В этом случае по установленному адресу в блоках 1 и 3 памяти записываются признаки двойной подмены, а. в блоке 8j памяти - новое слово подмены.

В этом случае п установленному адресу в блоках 1 и 3 памяти записываются признаки тройной подмены, а в блоке 82 памяти - слово подмены.

Наличие признака тройной подмены в блоках 1 и 3 памяти свидетельствует о невозможности замены информации по данному адресу.

В режиме считывания устройство работает следующим образом.

Подается единичный сигнал режима по входу 13, разрешающий прохождение сигнала 14 обращения от процессора на входы выборки блока 1 памяти через блок 4 выборки и отключающий блок 26 записи от адресных входов 11 и 12 (при этом на входе 24 устройства устанавливается уровень логического нуля, разрешающий передачу данных с выходов блока 1 памяти на входы блоков 2, 3, 81 и 82 памяти). Адрес и единичный сигнал обращения к основной памяти 27 поступают соответственно на входы 11, 12 и 14. Сигнал обращения проход 1 через блок 4 выборки и выдается на вход выборки блока 1 памяти. С задержкой, определяемой временем выборки, считанные из блока 1 памяти данные

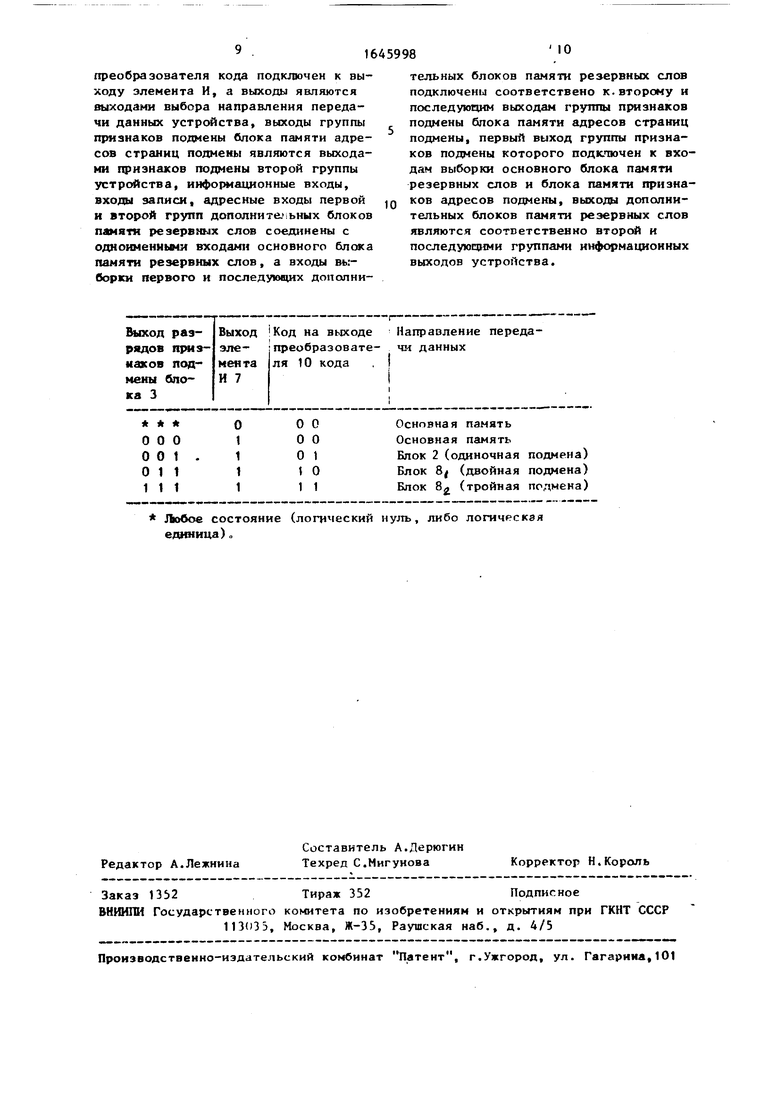

поступают соответственно: старшн разряды адреса блоков 2, 3, 8 и 8Л памяти - на мультиплексор 5, признаки подмены (выходы 18) - на входы выборки блоков 2, 3, 8 4 и 8 памяти. Выход признака одиночной подмены соединен с входами выборки блоков 2 и 3 памяти, признака двойной подмены - с входом выборки блока 8 , памяти, считанные из блока 3 памяти старшие разряды зафиксированного адреса подмены сравниваются в блоке 6 сравнения со старшими разрядами адреса обращения и, если сравнение произошло (единичный сигнал на выходе блока 6 сравнения) при одновременном наличии признаков одиночной подмены на соответствующих выходах блоков 1 и 3 памяти, на выходе элемента И 7 формируется единичный сигнал управления преобразователем 10 кода По этому сигналу двоичный код выбора направления по линиям 25 поступает на коммутатор 28 и подключает один из блоков памяти (2, 84 или 8- в зависимости от кратности подмены) для передачи на выходы 29 резервного слова через коммутатор 28

Преобразователь 10 кода работает в соответствии со следующей таблицей

Таким образом, предлагаемое устройство по сравнению с прототипом обеспечивает возможность многократной подмены информации по одному и тому же адресу подмены, вследствие чего увеличивается надежность основ - ной памяти. Формула изобретения

Устройство для подмены информации в постоянной памяти, содержащее основной блок памяти резервных слов, выходы которого являются информацион ными выходами первой группы устройства, блок памяти признаков адресов подмены, адресные входы первой группы которого соединены с одноименными входами основного блока памяти резервных слов и являются адресными входами первой группы устройства, блок памяти адресов страниц подмены, адресные входы которого являются адресными входами второй группы устрой сва, блок сравнения, входы первой группы которого подключены к- выходам адресов подмены блока памяти признаков адресов подмены, а входы второй группы - к информационным входам

.

.

- я

10

15

645998 и

первой группы блока памяти признаков адресов подмены и к одресным входам блока памяти адресов страниц подмены, элемент И, первый вход которого - соединен с первым выходом группы признаков подмены блока памяти адресов страниц подмены, второй вход подключен к перьому выходу группы признаков подмены блока памяти признаков адресов страниц подмены, третий вход подключен к выходу блока сравнения, блок выборки, входы которого с первого по третий являются соответственно входами режима работы, o6pantHT-i и кыборки устройства, а вход соединен с входом выборки блока памяти адресов страниц подмены, мультиплексор, информационные входы первой группы которого подключены к выходам адреса страницы блока памяти адресов страниц подмены, информационные входы второй группы соединены с информационными входами первой группы блока памяти адресов страниц подмены и являются информационными входами первой группы устройства, управляли и вход является входом выбора направления передачи адреса страниц устройства, а выходы подключены к адресньм входам второй группы основного блока памяти резервных сгон и блока памяти признаков адресов подмены, входы записи которых и вход записи блока памяти адресов страниц подмени являются вхо дом записи устройства, информационные входы основного блока памяти резервных слов являются информационными входами второй группы устрой20

25

30

35

, - , -

40

45

50

55

стве, информационный входы второй группы блоков пчмяти адресов страниц подмены и признаков адресов подмены являются информационными входами третьей группы устройства, отличающееся тем, что,- с целью повышения надежности постоянной памяти путем обеспечения возможности выполнения повторных подмен информации, в него введены N-1 дополнительных блоков памяти резервных слов, N - кратность подмены, и преобразователь кода, причем выходы группы признаков подмены блока памяти признаков адресов страниц подмены соединены с информационными входами преобразователя кода и являются выходами признаков подмены первой группь ус. ройгтвл, управляющий вход

у16

преобразователя кода подключен к выходу элемента И, а выходы являются выходами выбора направления передачи данных устройства, выходы группы признаков подмены блока памяти адресов страниц подмены являются выходами признаков подмены второй группы устройства, информационные входы, входы записи, адресные входы первой и второй групп дополните.,ьных блоков памяти резервных слов соединены с одноименными входами основного блока памяти резервных слов, а входы выборки первого и последующих дополни

Любое состояние (логический нуль, либо логическая единица)„

10

тельных блоков памяти резервных слов подключены соответствено к.второму и последующим выходам группы признаков подмены блока памяти адресов страниц подмены, первый выход группы признаков подмены которого подключен к входам выборки основного блока памяти резервных слов и блока памяти признаков адресов подмены, выходы дополнительных блоков памяти резервных слов являются соответственно второй и последующими группами информационных выходов устройства.

Авторы

Даты

1991-04-30—Публикация

1989-04-06—Подача