Изобретение относится к вычислительной технике и предназначено для ускоренного вычисления функции arctg x/y в специализированных вычислителях, например преобразователях координат.

Цель изобретения - повышение точности вычисления и быстродействия.

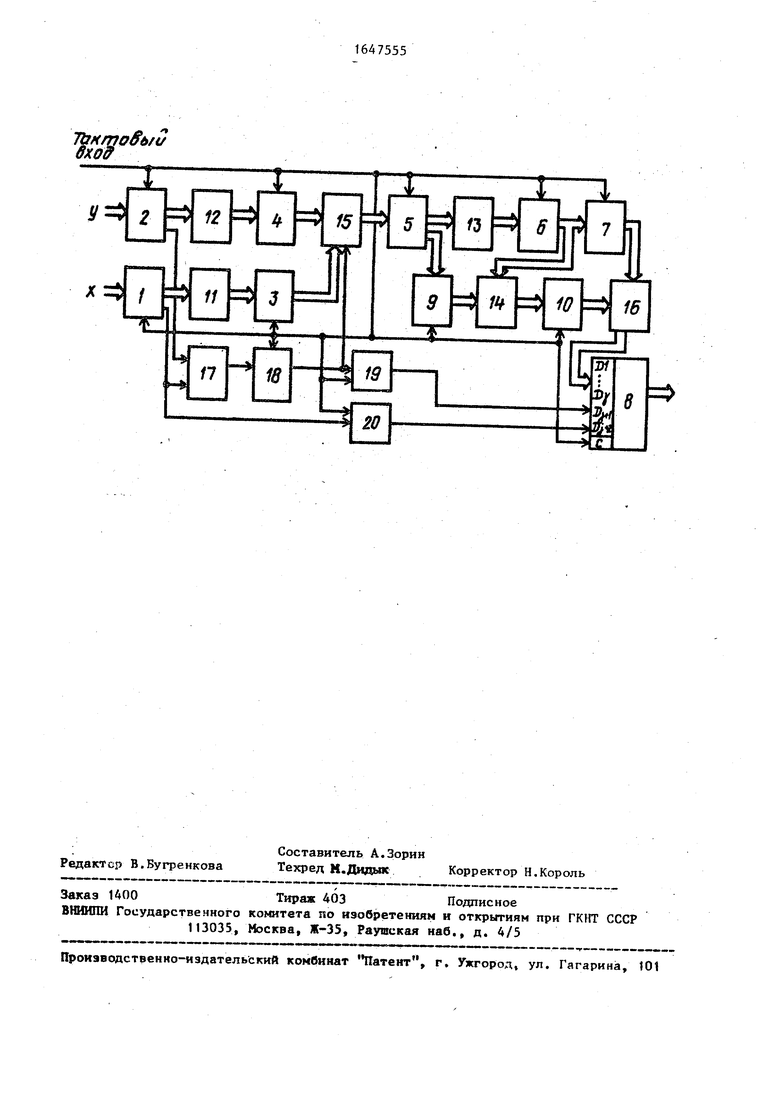

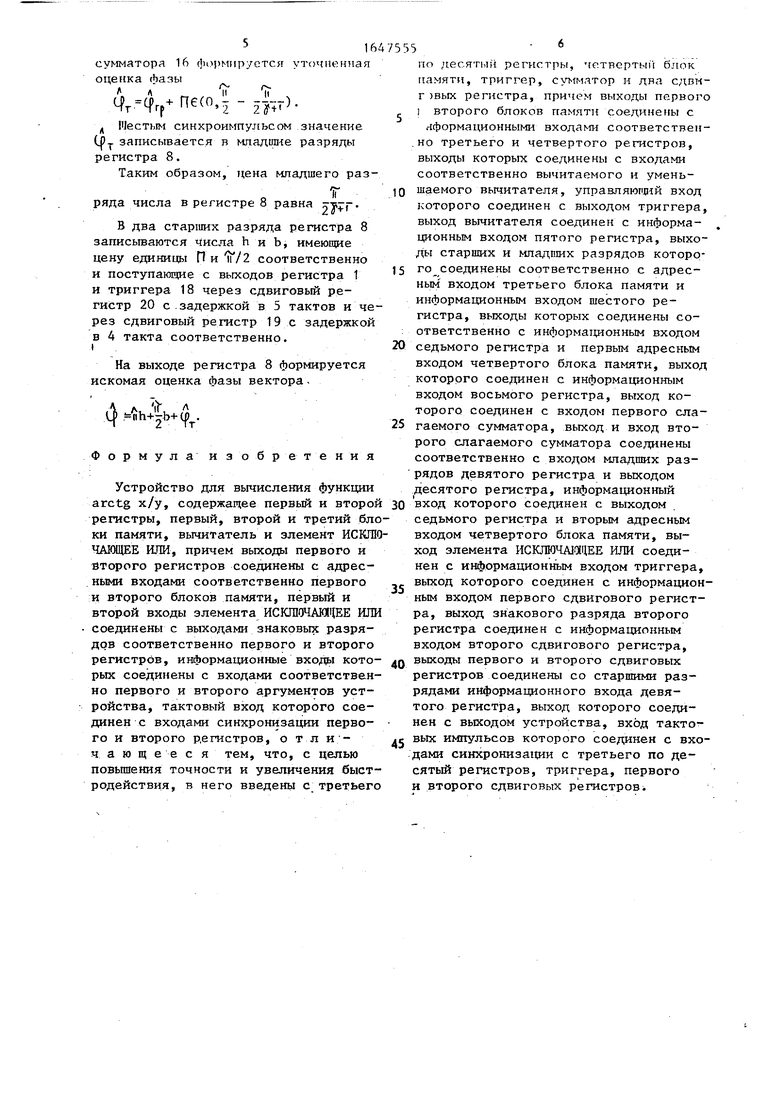

На чертеже приведена структурная схема устройства.

Устройство содержит регистры 1-10, блоки 11-14 памяти, вычитатель 15, сумматор 16, элемент 17 ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер 18 и два сдвиговых регистра 19 и 20.

Работа устройства основана на использовании следующего алгоритма нахождения оценки фазы вектора Ц для . различных частей плоскости

f

arctg(/x///y|), если ,

1Г

2+arctg(/y//|x/), еслих 0,

(/x///y/), если , 1f+-+arctg(/y///xO, еслих 0, ,

Вычисление отношения аргументов производится по формуле:

jZ Voja/xMeja/

1У.1 аЦа Н Ча/Х/

где a - некоторая константа.

Устройство работает следующим образом.

Квадратурные составляющие вектора - значения аргументов X и Y

X AsinЈf; Y Acostf, с соответствукщих входов устройства поступают на входы регистров 1

4 :л ел ел

и 2 соответственно. Первым синхроимпульсом, поступающем на тактовый вход устройства в регистры 1 и 2, записываются значения усеченных аргументов X и

,д, ,,

гдеД(5Ј (0,1) и Д,се(0,1) - погрешности, вызванные конечной разрядностью регистров 1 и 2. С выходов ре- гистров 1 и 2 абсолютные значения усеченных аргументов /х( и /Y/ поступают на входы блоков 11 и 12 памяти, а знаки h и k аргументов X и Y (О - для положительных чисел, 1 - для отрицательных чисел) со знаковых разрядов регистров 1 и 2 - на входы схемы 17 ИСКЛЮЧАЮЩЕЕ ИЛИ.

Количество ft разрядов адресных входов блоков 11 и 12 связано с моду- лем А вектора соотношением:

ft

1о§2А.

Блоки 11 и 12 представляют собой логарифмические преобразователи, выходные данные которых имеют соответственно вид:

c loge/X /-A2-g;

d log2/Y /-A2-c,

где U2se(0,1) и Д2се(0,1) - погрешности выходных данных блоков 11 и 12 вызванные конечной разрядностью выходов Р,

2)С

где V - количество разрядов на выход блоков памяти.

Вторым синхроимпульсом, поступающим на тактовый вход устройства, в регистры 3,4 и триггер 18 записываются данные с выходов блоков 11 и 12, которые подаются на вычитатель 15. Этим же синхроимпульсом в регистры 1 и 2 записываются новые зна шния аргументов X и Y.

Вычитатель формирует ОГ+1)-разрядную разность Ј выходных данных

Ј (-1)e(c-d),

изменяя знаки операндов end под действием управляющего сигнала b.

Третьим синхроимпульсом число Ј записывается в регистр 5. Число Ј, представленное Р старшими разрядами числа Ј, с соответствующих разрядов выхода регистра 5 поступает на адресный вход блока 13 памяти.

e.-2f лзгде g y+1-/3;

g 5

0

5

0

А 6(0,1) - погрешность, вызванная конечной разрядностью адресного входа /5 блока 13.

L, а а

ЧислоЈ3 , представленное g младшими разрядами числа Ј с соответствующих разрядов выхода регистра 5 поступает на вход регистра 9.

На выходе блока 13 формируется грубая оценка (0гр фазы по алгоритму:

q rp arctg ,е(о,1 - -|-т), 7

где о, 6(0,-0+-) - погрешность, вызванная конечной , разрядностью выхода блока 13;

W

41

7+Т Чена единицы младшего разряда колад гр .

Четвертым синхроимпульсом грубая оценка фазы записывается в регистр 6, а число в регистр 9. С выходов регистров 6 и 9 эти числа по- ступают на адресные входы блока 14 памяти, причем Hag разрядов адресного входа подается число Г, а на остальные - усеченное значение ср„ грубой оценки фазы Ср г. со старших разрядов выхода регистра 6:

4ч4Д,

где о G 0 о pff) погрешность, вызванная пренебрежением в Ср и. -р младшими разрядами . На выходе блока 14 формируется

поправка П к оценке фазы(гр:

П |sin2lfylna-Ј3,

Л и

где 0 € (0,) - погрешность, вызванная конечной разрядностью выходных данных блока 14,

0

5

и

цена единицы младшего разряда поправки, равная цене единицы младшего разряда грубой оценки фазы ц Гр .

Пятым синхроимпульсом значения грубой оценки фазы Л и поправки П записываются соответственно в регистры 7 и Ц) и подаются на первый и второй входы сумматора 16. iia выходе

сумматора 16 формируется уточненная оценка Лазы

АЛ Л Т с}гр+пе(о4-г;-т).

д Шестым синхроимпульсом значение СРТ записывается в младшие разряды регистра 8.

Таким образом, цена младшего разТряда числа в регистре 8 равна два старших разряда регистра 8 записываются числа h и Ь, имеющие цену единицы П и 1Г/2 соответственно и поступающие с выходов регистра 1 и триггера 18 через сдвиговый регистр 20 с задержкой в 5 тактов и через сдвиговый регистр 19 с задержкой в 4 такта соответственно.

На выходе регистра 8 формируется искомая оценка фазы вектора 4

h+|b+tpT.

Формула изобретения

Устройство для вычисления функции arctg x/y, содержащее первый и второй регистры, первый, второй и третий блоки памяти, вычитатель и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выходы первого и второго регистров соединены с адресными входами соответственно первого и второго блоков памяти, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с выходами знаковых разрядов соответственно первого и второго регистров, информационные входы кото- рых соединены с входами соответственно первого и второго аргументов устройства, тактовый вход которого соединен с входами синхронизации перво- ГО И ВТОРОГО Р.еГИСТрОВ, О Т Л И -

чающееся тем, что, с целью повышения точности и увеличения быстродействия, в него введены с третьего

5

5

0

5

5

0 Q с

по десятый регистры, четвертый блок памяти, триггер, сумматор и два сдвм- г )вых регистра, причем выходы первого 1 второго блоков памяти соединены с

лформационными входами соответственно третьего и четвертого регистров, выходы которых соединены с входами соответственно вычитаемого и уменьшаемого вычитателя, управляющий вход которого соединен с выходом триггера, выход вычитателя соединен с информационным входом пятого регистра, выходы старших и младших разрядов которого соединены соответственно с адресным входом третьего блока памяти и информационным входом шестого регистра, выходы которых соединены соответственно с информационным входом седьмого регистра и первым адресным входом четвертого блока памяти, выход которого соединен с информационным входом восьмого регистра, выход которого соединен с входом первого слагаемого сумматора, выход и вход второго слагаемого сумматора соединены соответственно с входом младших разрядов девятого регистра и выходом десятого регистра, информационный вход которого соединен с выходом седьмого регистра и вторым адресным входом четвертого блока памяти, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом триггера, выход которого соединен с информационным входом первого сдвигового регистра, выход знакового разряда второго регистра соединен с информационным входом второго сдвигового регистра, выходы первого и второго сдвиговых регистров соединены со старшими разрядами информационного входа девятого регистра, выход которого соединен с выходом устройства, вход тактовых импульсов которого соединен с входами синхронизации с третьего по десятый регистров, триггера, первого и второго сдвиговых регистров.

faxmofib/v ffxoff

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций | 1989 |

|

SU1705822A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ arctg(y/x) | 2015 |

|

RU2595486C1 |

| Устройство для вычисления функций | 1986 |

|

SU1374219A1 |

| Устройство для калмановской фильтрации | 1987 |

|

SU1564711A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Устройство вычисления функции арктангенс отношения | 1988 |

|

SU1585793A1 |

| Процессор для корреляционного анализа | 1978 |

|

SU744601A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 1988 |

|

SU1755650A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных ЦВМ и вычислителях для определения аргумен-г та комплексного числа и преобразования координат в реальном масштабе времени. Целью изобретения является повышение точности и быстродействия вычисления таблично-алгоритмическим методом. Устройство содержит десять регистров, четыре блока памяти, вычислитель, сумматор, схему ИСКЛЮЧАЮЩЕЕ ИЛИ, триггер и два сдвиговых регистра. 1 ил.

| Устройство для определения аргумента вектора | 1986 |

|

SU1319024A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство ЧССР № 227756, кл | |||

| Г, 06 F 7/5i52, 1982. | |||

Авторы

Даты

1991-05-07—Публикация

1988-12-21—Подача