Изобретение относится к вычислительной технике и предназначено для контроля циклических последовательностей импульсов.

Целью изобретения является расширение функциональных возможностей за счет блокировки контролируемых последовательностей при сбоях.

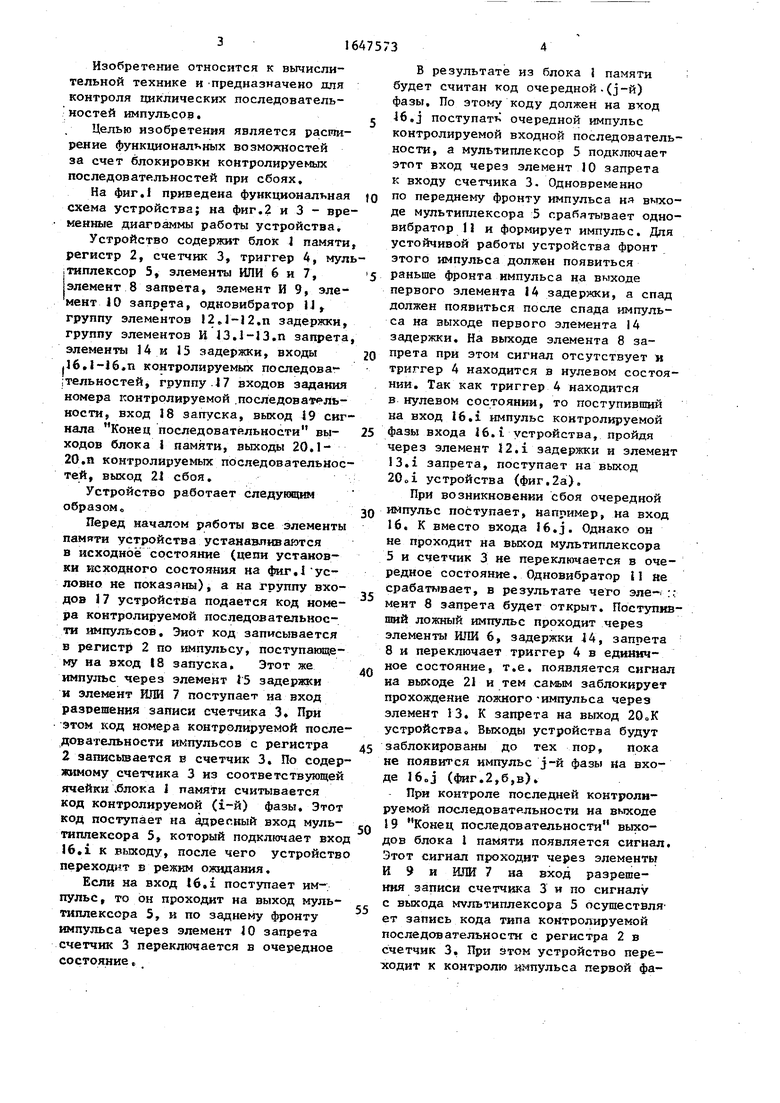

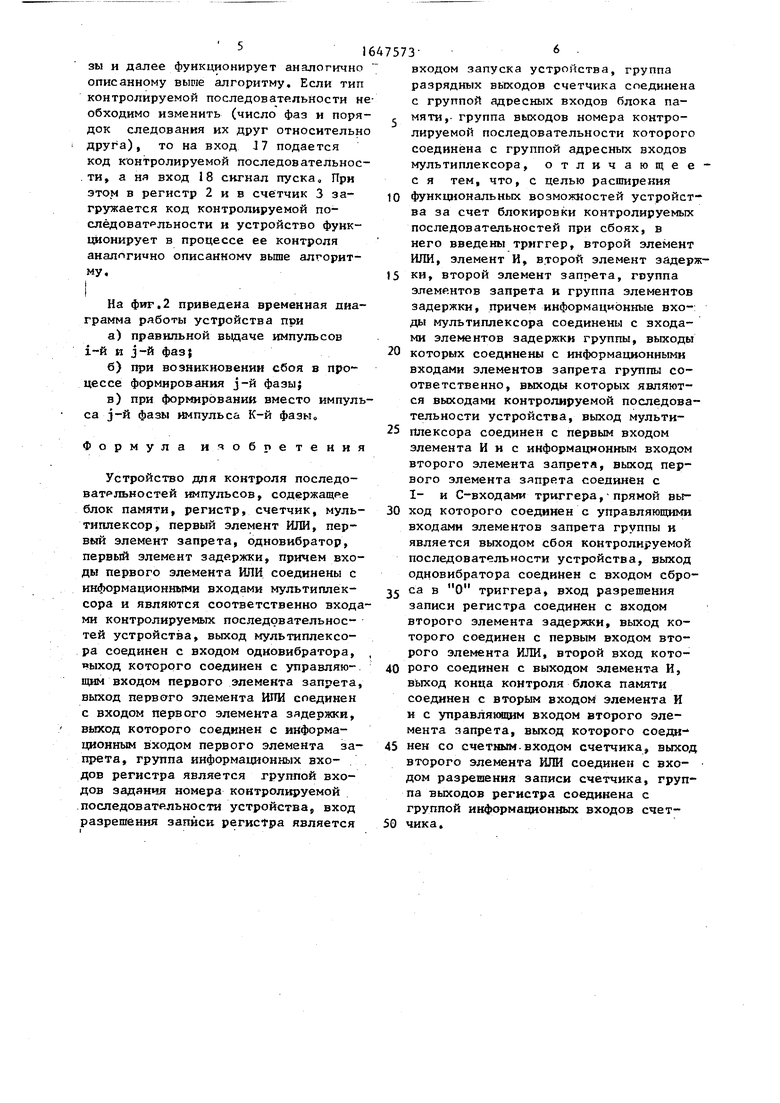

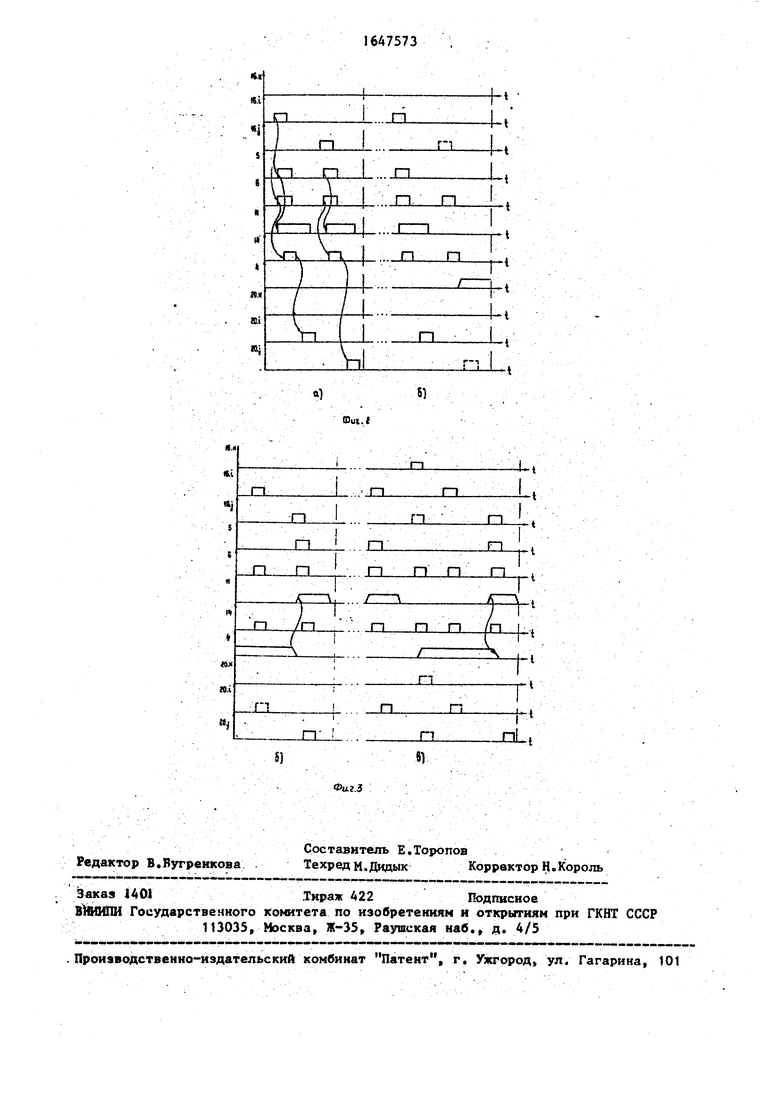

На фиг.1 приведена функциональная схема устройства; на фиг.2 и 3 - временные диаграммы работы устройства.

Устройство содержит блок I памяти регистр 2, счетчик 3, триггер 4, муль ,типлексор 5, элементы ИЛИ 6 и 7, элемент 8 запрета, элемент И 9, элемент 10 запрета, одновибратор 11 группу элементов 12,1-12.п задержки, группу элементов И 13.1-13.п запрета элементы 14 и 15 задержки, входы |1б.1-16.п контролируемых последовательностей, группу.47 входов задания номера контролируемой .последоват ль- ности, вход 18 запуска, выход 19 сигнала Конец последовательности выходов блока 1 памяти, выходы 20.1- 20.п контролируемых последовательностей, выход 24 сбоя.

Устройство работает следующим образом.

Перед началом работы все элементы памяти устройства устанавливаются в исходное состояние (цепи установки исходного состояния на фиг.1 условно не показаны), а на группу входов 17 устройства подается код номера контролируемой последовательности импульсов. Эиот код записывается в регистр 2 по импульсу, поступающему на вход 18 запуска. Этот же импульс через элемент 15 задержки и элемент ИЛИ 7 поступает на вход разрешения записи счетчика 3 При этом код номера контролируемой последовательности импульсов с регистра 2 записывается в счетчик 3. По содержимому счетчика 3 из соответствующей ячейки .блока i памяти считывается код контролируемой (i-й) фазы. Этот код поступает на адресный вход мультиплексора 5, который подключает вхо 16.1 к выходу, после чего устройств переходит в режим ожидания.

Если на вход 16.Ј поступает импульс, то он проходит на выход мультиплексора 5, и по заднему фронту импульса через элемент 10 запрета счетчик 3 переключается в очередное состояние„

0

5

0

5

0

5

0

5

В результате из блока I памяти будет считан код очередной .(j-й) фазы. По этому коду должен на вход 46.j поступать очередной импульс контролируемой входной последовательности, а мультиплексор 5 подключает этот вход через элемент 10 запрета к входу счетчика 3. Одновременно по переднему фронту импульса ня вмхо- де мультиплексора 5 срабатывает одно- вибратор Ц и формирует импульс. Для устойчивой работы устройства фронт этого импульса должен появиться раньше фронта импульса на выходе первого элемента 14 задержки, а спад должен появиться после спада импульса на выходе первого элемента I4 задержки. На выходе элемента 8 запрета при этом сигнал отсутствует м триггер 4 находится в нулевом состоянии. Так как триггер 4 находится в нулевом состоянии, то поступивший на вход 16.i импульс контролируемой фазы входа 46.i устройства, пройдя через элемент 12,i задержки и элемент 13.1 запрета, поступает на выход 20 о i устройства (фиг,2а).

При возникновении сбоя очередной импульс поступает, например, на вход 16. К вместо входа 16.J. Однако он не проходит на выход мультиплексора 5 и счетчик 3 не переключается в очередное состояние. Одновибратор i1 не срабатывает, в результате чего эле- :: мент 8 запрета будет открыт. Поступивший ложный импульс проходит через элементы ИЛИ 6, задержки 44, запрета 8 и переключает триггер 4 в единичное состояние, т.е. появляется сигнал на выходе 21 и тем самым заблокирует прохождение ложного-импульса через элемент 13. К запрета на выход 20„К устройства. Выходы устройства будут заблокированы до тех пор, пока не появится импульс j-й фазы на входе 160j (фиг.2,б,в)

При контроле последней контролируемой последовательности на выходе 19 Конец последовательности выходов блока i памяти появляется сигнал. Этот сигнал проходит через элементы И 9 и ИЛИ 7 на вход разрешения записи счетчика 3 и по сигналу с выхода мультиплексора 5 осуществляет запись кода типа контролируемой последовательности с регистра 2 в счетчик 3. При этом устройство переходит к контролю вмпульса первой фазы и далее функционирует аналогично описанному выше алгоритму. Если тип контролируемой последовательности необходимо изменить (число фаз и порядок следования их друг относительно друга), то на вход J7 подается код контролируемой последовательности, а ня вход 18 сигнал пуска. При этом в регистр 2 и в счетчик 3 загружается код контролируемой по- слёдоватрльности и устройство функционирует в процессе ее контроля аналогично описанному выше ап орит- му.

I

На фиг.2 приведена временная диаграмма работы устройства при

а)правильной выдаче импульсов i-й и j-й фаз;

б)при возникновении сбоя в процессе формирования j-й фазы;

в)при формировании вместо импульса j-й фазы импульса К-й фазы

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее блок памяти, регистр, счетчик, мультиплексор, первый элемент ИЛИ, первый элемент запрета, одновибратор, первый элемент задержки, причем входы первого элемента ИЛИ соединены с информационными входами мультиплексора и являются соответственно входами контролируемых последовательностей устройства, выход мультиплексора соединен с входом одновибратора, иыход которого соединен с управляющим входом первого элемента запрета, выход первого элемента ИЛИ соединен с входом первого элемента задержки, выход которого соединен с информационным входом первого элемента запрета, группа информационных входов регистра является группой входов задания номера контролируемой последовательности устройства, вход разрешения записи регистра является

входом запуска устройства, группа разрядных выходов счетчика соединена с группой адресных входов блока па- мяти, группа выходов номера контролируемой последовательности которого соединена с группой адресных входов мультиплексора, отличающее- с я тем, что, с целью расширения

Функциональных возможностей устройства за счет блокировки контролируемых последовательностей при сбоях, в него введены триггер, второй элемент ИЛИ, элемент И, второй элемент эадерж-

ки, второй элемент запрета, гвуппа элементов запрета и группа элементов задержки, причем информационные входы мультиплексора соединены с входами элементов задержки группы, выходы

которых соединены с информационными входами элементов запрета группы соответственно, выходы которых являются выходами контролируемой последовательности устройства, выход мультиплексора соединен с первым входом элемента И и с информационным входом второго элемента запрета, выход первого элемента запрета соединен с I- и С-входами триггера,-прямой выход которого соединен с управляющими входами элементов запрета группы и является выходом сбоя контролируемой последовательности устройства, выход одновибратора соединен с входом сброса в О триггера, вход разрешения записи регистра соединен с входом второго элемента задержки, выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом элемента И, выход конца контроля блока памяти соединен с вторым входом элемента И и с управляющим входом второго элемента запрета, выход которого соедн-1

нен со счетным.входом счетчика, выход второго элемента ИЛИ соединен с входом разрешения записи счетчика, группа выходов регистра соединена с группой информационных входов счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля многоканальных импульсных последовательностей | 1987 |

|

SU1478216A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1444777A1 |

| Устройство для программного управления | 1990 |

|

SU1784939A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1737453A1 |

| Устройство для контроля сигналов | 1989 |

|

SU1667078A1 |

| Устройство для моделирования гибких производных систем | 1988 |

|

SU1631551A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1298721A1 |

| Устройство для контроля динамических блоков памяти | 1985 |

|

SU1282221A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1805467A1 |

Изобретение относится к вычисли тельной технике и предназначено для г И./ № контроля циклических последовательностей импульсов. Отличительной особенностью устройства является то, что оно позволяет блокировать контролируемые последовательности при сбоях до появления правильной последовательности. Целью изобретения является расширение функциональных возможностей за счет блокировки контролируемых последовательностей при сбоях„ Поставленная цель достигается за счет введения триггера 4, элемента ИЛИ 7, элемента И 9, элемента 10 запрета, группы 12 элементов задержки, группы 13 элементов запрета, элемента 15 задержки. 3 ил. M.L (Л 20 CD Ј 1 СЛ СЈ Фиг. 1

)

5)

8)

81

| Устройство для контроля последовательности чередования импульсных сигналов | 1985 |

|

SU1256184A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательностей импульсов | 1987 |

|

SU1444777A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-05-07—Публикация

1989-05-25—Подача