г

Nilib 4 д

-Nj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1647573A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1651289A1 |

| Устройство для контроля последовательностей импульсов | 1990 |

|

SU1725373A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1985 |

|

SU1298721A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1723661A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для обслуживания запросов | 1990 |

|

SU1805467A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для контроля последовательностей импульсов | 1989 |

|

SU1619277A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1277105A1 |

Изобретение относится к области импульсной техники и предназначено для проверки многоканальных иМпульс- ных последовательностей. Отличительной особенностью устройства является то, что оно позволяет увеличить достоверность контроля за счет нарушения очередности последовательности конт- , ролиррвать последовательности импульсов разных типов. Целью изобретения является увеличение достоверности контроля. Поставленная цель достигается введением одновибратора 5, элемента 1 задержки, регистра 3, блока 1 постоянной памяти. 2 ил. S (Л

м 7

/-

Изобретение относится к импульсной технике и предназначено для проверки многоканальных импульсных последовательностей в системах контроля нлф ровых устройств аппаратуры управления и связи,

. Цель изобретения - увеличение достоверности контроля.

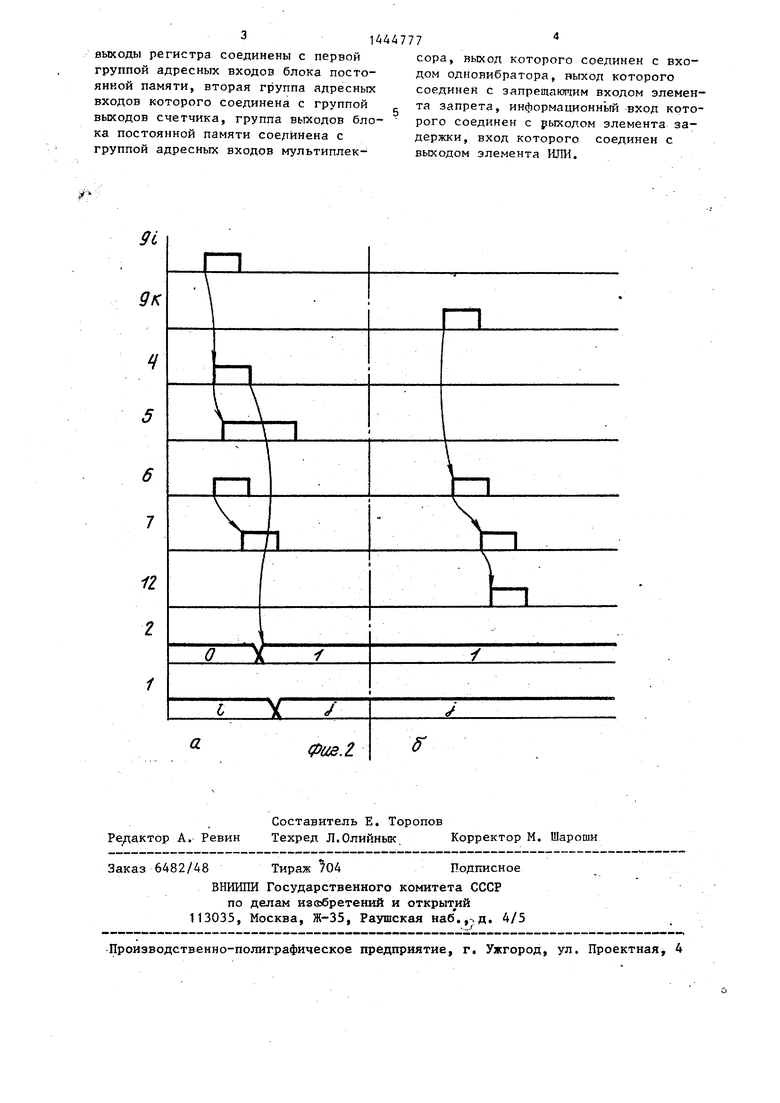

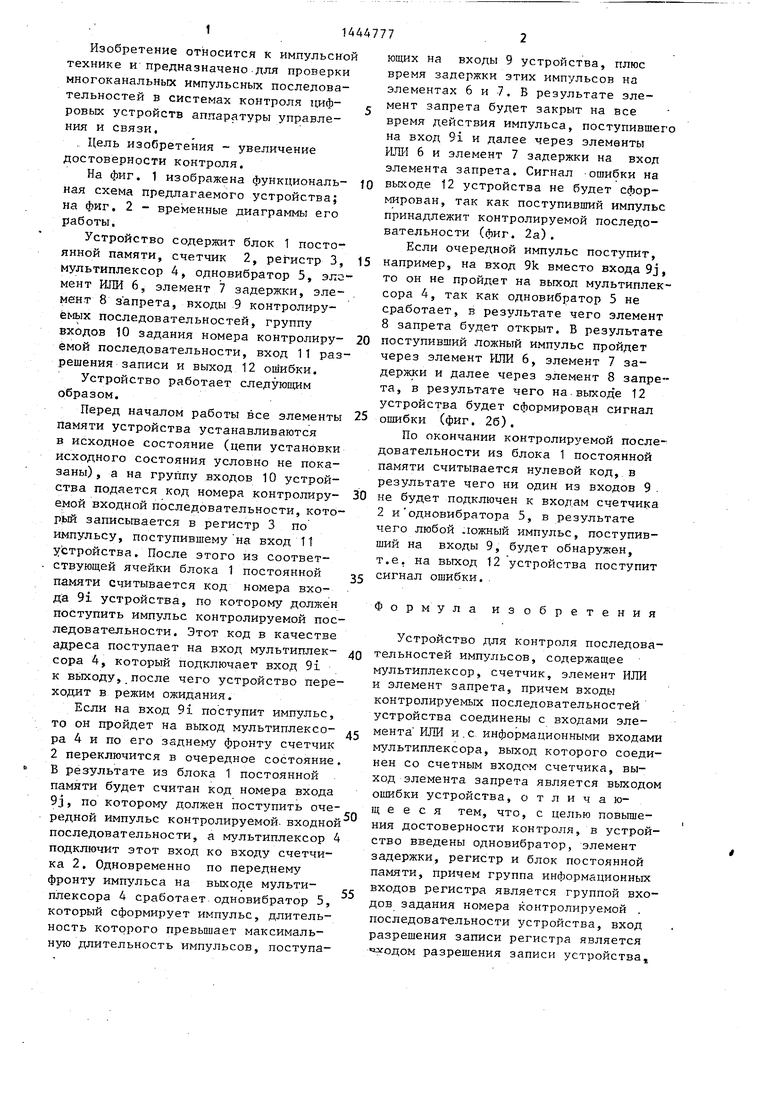

На фиг. 1 изображена функдиональ- ная схема предлагаемого устройства; на фиг. 2 - временные диаграммы его работы.

Устройство содержит блок 1 постоянной памяти, счетчик 2, регистр 3, мультиплексор 4, однрвибратор 5, элемент ИЛИ 6, элемент 7 задержки, эле- мент 8 запрета, входы 9 контролиру- ё№1Х последовательностей, группу входов 10 задания номера контролиру- емой последовательности, вход 11 разрешения записи и выход 12 ошибки,

Устройство работает следующим образом.

Перед началом работы все элементы памяти устройства устанавливаются в исходное состояние (цепи установки исходного состояния условно не показаны) , а на группу входов 10 устройства подается код номера контролиру- емой входной последовательности, кото- рьй записывается в регистр 3 по импульсу, поступившему на вход 11 уЬтройства, После этого из соответствующей ячейки блока 1 постоянной памяти считывается код номера вхо- д1а 91 устройства, по которому должен поступить импульс контролируемой последовательности. Этот код в качестве адреса поступает на вход мультиплек- сора 4, который подключает вход 91 к вь1ходу, после чего устройство переходит в режим ожидания.

Если на вход 91 поступит импульс, то он пройдет на выход мультиплексо- ра 4 и по его заднему фронту счетчик 2 переключится в очередное состояние Б результате из блока 1 постоянной памяти будет считан код номера входа 9J, по которому должен поступить очередной импульс контролируемой, входно последовательности, а мультиплексор подключит этот вход ко входу счетчика 2. Одновременно по переднему фронту импульса на выходе мультиплексора 4 сработает одновибратор 5, который сформирует импульс, длительность которого превышает максимальную длительность импульсов, поступа

с

o

5 0

5 0 5 0

с

0

5

ющих на входы 9 устройства, плюс время задержки этих импульсов на элементах 6 и 7. Б результате элемент запрета будет закрыт на все время действия импульса, поступившего на вход 91 и далее через элементы ИЛИ 6 и элемент 7 задержки на вход элемента запрета. Сигнал -ошибки на вьгходе 12 устройства не будет сформирован, так как поступивший импульс принадлежит контролируемой последовательности (фиг. 2а).

Если очередной импульс поступит, например, на вход 9k вместо входа 9j, то он не пройдет на выход мультиплексора 4, так как одновибратор 5 не сработает, в результате чего элемент 8 запрета будет открыт. В результате поступивший ложный импульс пройдет через элемент ИЛИ 6, элемент 7 задержки и далее через элемент 8 запрета, в результате чего на выход е 12 устройства будет сформирован сигнал ошибки (фиг. 26),

По окончании контролируемой последовательности из блока 1 постоянной памяти считывается нулевой код, в результате чего ни один из входов 9 . не будет подключен к входам счетчика 2 и одновибратора 5, в результате чего любой ложный импульс, поступивший на входы 9, будет обнаружен, т.е. на выход 12 устройства поступит сигнал ошибки,.

Формула изобретения

Устройство для контроля последовательностей импульсов, содержащее мультиплексор, счетчик, элемент ИЛИ и элемент запрета, причем входы контролируемых последовательностей устройства соединены с входами элемента ИЛИ и.с, информационными входами мультиплексора, выход которого соединен со счетным входом счетчика, выход элемента запрета является выходом ошибки устройства, отличающееся тем,, что, с целью повьш1е- ния достоверности контроля, в устройство введены одновибратор, элемент задержки, регистр и блок постоянной памяти, причем группа информационных входов регистра является группой входов задания номера контролируемой . последовательности устройства, вход разрешения записи регистра является одом разрешения записи устройства.

выходы регистра соединены с первой группой адресных входов блока постоянной памяти, вторая группа адресных входов которого соединена с группой выходов счетчика, группа выходов блока постоянной памяти соединена с группой адресных входов мультиплек12

а

Фиа.г

сора, выход которого соединен с входом одновибратора, выход которого соединен с запрещаюпщм входом элемента запрета, информационный вход которого соединен с рыходом элемента задержки, вход которого соединен с выходом элемента ИЛИ.

| Устройство контроля импульсных сигналов | 1980 |

|

SU930632A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля последовательности чередования импульсных сигналов | 1985 |

|

SU1256184A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-12-15—Публикация

1987-07-13—Подача