I Ч I

п

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Микропрограммное устройство управления с динамической памятью | 1985 |

|

SU1260954A1 |

| Микропрограммное устройство управления модуля распределенной параллельной вычислительной системы | 1985 |

|

SU1252775A1 |

| Устройство для контроля схем сравнения | 1984 |

|

SU1218386A1 |

| Устройство для тестового диагностирования | 1984 |

|

SU1213481A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1495789A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Микропрограммное устройство управления | 1989 |

|

SU1633402A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

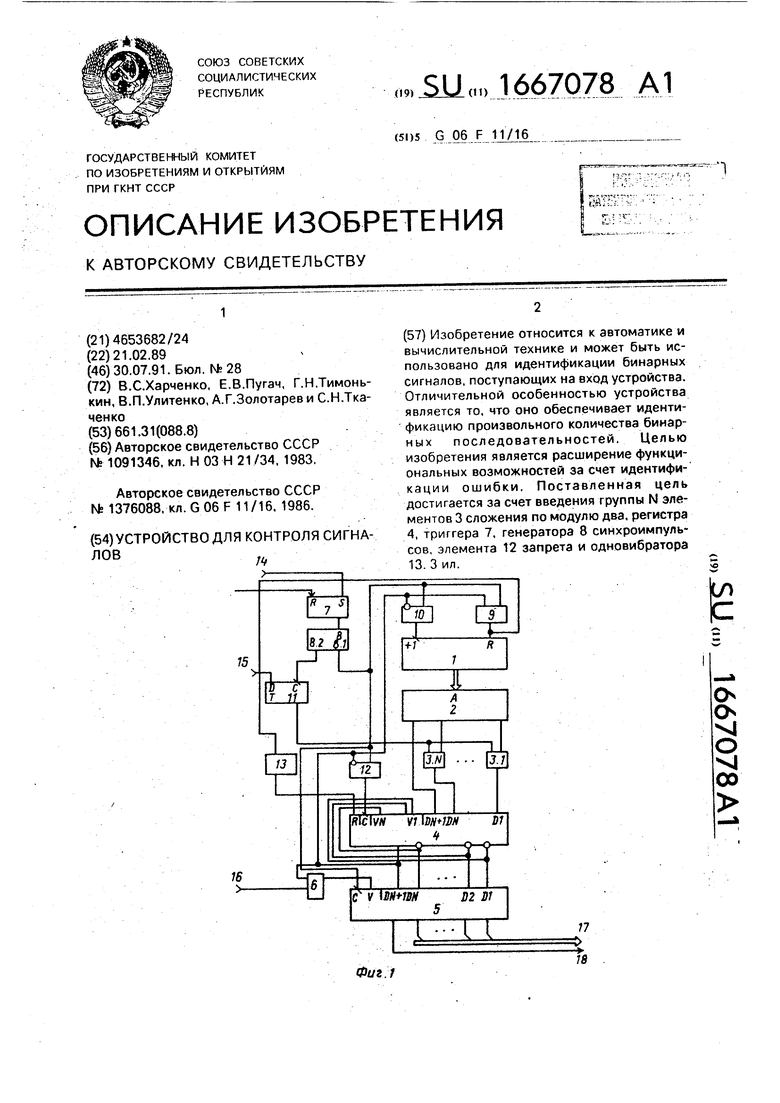

Изобретение относится к автоматике и вычислительной технике и может быть использовано для идентификации бинарных сигналов, поступающих на вход устройства. Отличительной особенностью устройства является то, что оно обеспечивает идентификацию произвольного количества бинарных последовательностей. Целью изобретения является расширение функциональных возможностей за счет идентификации ошибки. Поставленная цель достигается за счет введения группы N элементов сложения 3 по модулю два, регистра 4, триггера 7, генератора 8 синхроимпульсов, элемента 12 запрета, одновибратора 13. 3 ил.

Фиг 1

18

Изобретение относится к автоматике и вычислительной технике и может бдыть использовано для идентификации бинарных сигналов, поступающих на вход устройства от различных объектов управления, а также в средствах контроля диагностирования и отладки систем.

Целью изобретения является расширение функциональных возможностей за счет идентификации ошибки.

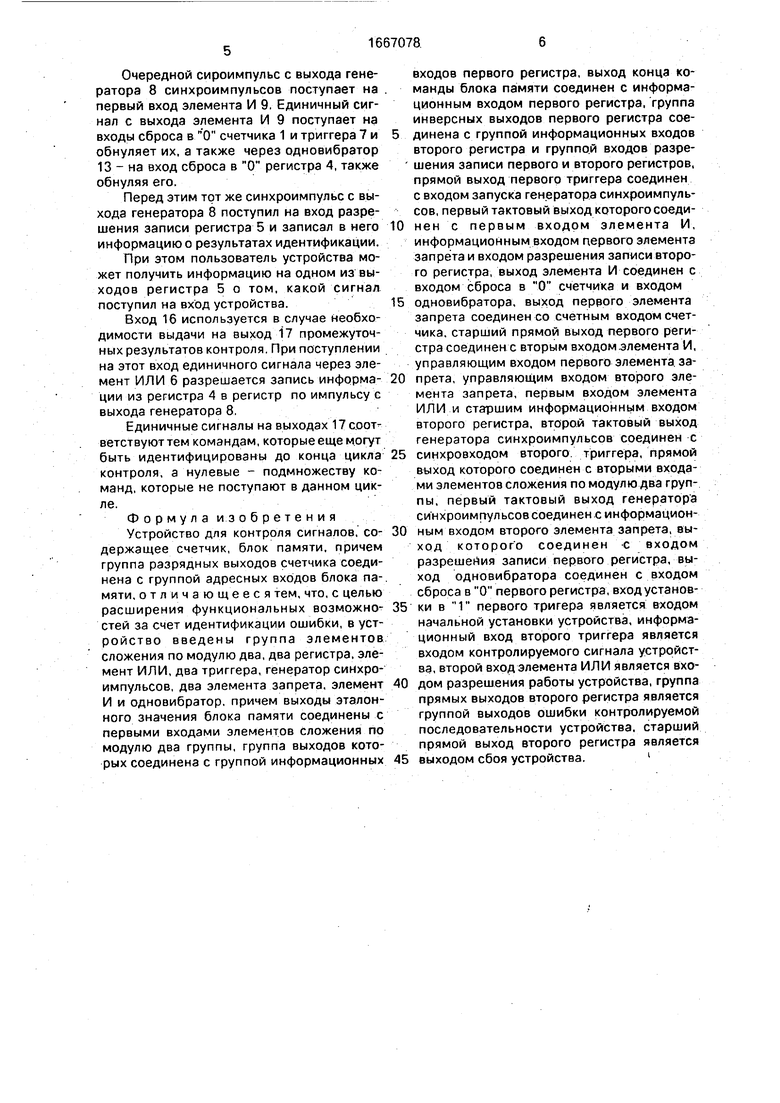

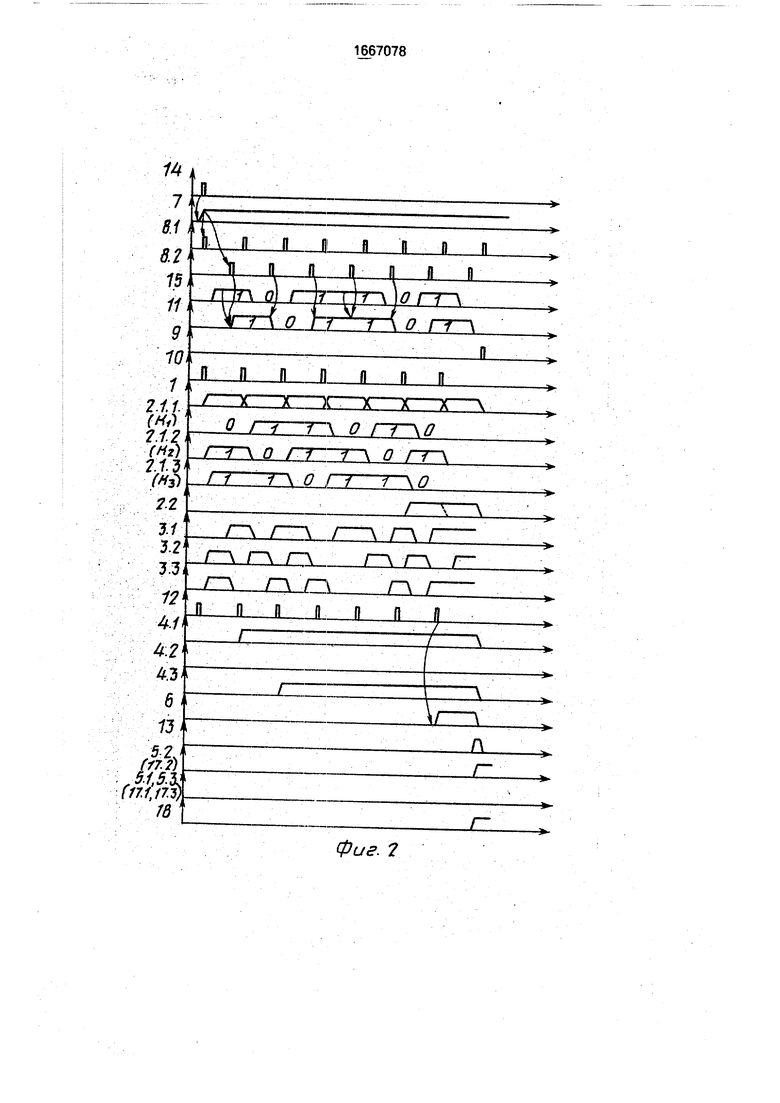

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг.2 - временная диаграмма функционирования устройства; на фиг.З - пример прошивки блока памяти.

Устройство содержит счетчик 1, блок 2 памяти, группу 3 элементов сложения по модулю два, регистры 4 и 5, элемент ИЛИ 6, триггер 7, генератор 8 синхроимпульсов, элемент И 9, элемент 10 запрета, триггер 11, элемент 12 запрета, одновибратор 13, вход 14 начальной установки, вход i контролируемой последовательности, вход 16 разрешения работы и выходы 17 и 18.

Принцип действия устройства заключается в следующем.

В блоке 2 памяти записаны все возможные коды бинарных последовательностей, характеризующих состояние объекта управления, причем один код характеризует исправное состояние объекта управления, а все остальные- неисправное. Неисправные состояния характеризуются различными бинарными последовательностями. В общем случае их может быть N. В каждой микрокоманде работы устройства записаны коды сигналов, характеризующие различные состояния объекта управления, в одни и те же моменты времени (Si.i, S 1.2SLN).

Таким образом, сигналами, поступающими на вход устройства, осуществляется процедура идентификации сразу по всем возможным состояниям.

В начальный момент времени счетчик 1. регистры 4 и 5, триггеры 7 и 11 находятся в нулевом состоянии. При подаче единичного сигнала на вход 14 устройства триггер 7 переводится в единичное состояние. Единичный сигнал с прямого выхода триггера 7 поступает на вход генератора 8 синхроимпульсов и включает его.

Нулевой уровень с прямого старшего выхода регистра 4 поступает на управляющие входы элементов 10 и 12 и подготавливает их к срабатыванию.

Первый синхроимпульс с выхода генератора 8 синхроимпульсов поступает на вход синхронизации триггера 11 и осуществляет запись в него сигнала, поступающего на вход 15 устройства.

. Так как в счетчик 1 записан нулевой код, то на выходе блока 2 присутствует информация о первой микрокоманде работы устройства. Информация с группы выходов блока 2 поступает на первые входы группы 3 элементов сложения по модулю два.

Сигнал, пришедший на вход устройства, с выхода триггера 11 поступает на вторые входы группы 3 элементов сложения по мо0 дулю два. При этом эта группа осуществляет сравнение первых бинарных сигналов всех эталонных последовательностей, хранящихся в блоке 2.

На выходах тех элементов 3, где про5 изошло несравнение, появляются сигналы единичного уровня, которые поступают на соответствующие информационные входы регистра 4.

0 По заднему фронту первого синхроимпульса, поступающего с выхода генератора 8 синхроимпульсов на вход элемента 12. осуществляется перевод его в единичное состояние. По заднему фронту синхроим5 пульса, поступающего с выхода элемента 12 на вход разрешения записи регистра 4, осуществляется запись в регистр 4 информации о результате сравнения. Это возможно благодаря присутствию на группе управля0 ющих входов регистра 4 сигналов с группы инверсных выходов этого же регистра.

После этого из процедуры идентификации исключаются те бинарные последовательности, где на первом же сигнале

5 произошло несравнение. Это возможно благодаря тому, что инверсные выходы соответствующих триггеров, входящих в состав регистра 4, подключены к соответствующим управляющим входам

0 этого же регистра.

Первый синхроимп/льс с выхода генератора 8 синхроимпульсов поступает через элемент 10 на счетный вход счетчика 1 и переадресует его. Информация об адресе

5 следующей микрокоманды с группы выходов счетчика 1 поступает на группу адресных входов блока 2 и переадресует его.

Дальнейшая работа устройства осуществляется по описанному выше алгоритму.

0

Останов устройства происходит следующим образом.

В последней микрокоманде работы устройства на выходе блока 2 присутствует сиг5 нал единичного уровня. Этот сигнал запоминается в старшем разряде регистра 4. Сигнал единичного уровня с прямого старшего выхода регистра 4 поступает через элемент ИЛИ 6 на управляющий вход регистра 5 и на второй вход первого элемента И, подготавливая его к срабатыванию.

Очередной сироимпульс с выхода генератора 8 синхроимпульсов поступает на первый вход элемента И 9. Единичный сигнал с выхода элемента И 9 поступает на входы сброса в О счетчика 1 и триггера 7 и обнуляет их, а также через одновибратор 13 - на вход сброса в О регистра 4, также обнуляя его.

Перед этим тот же синхроимпульс с выхода генератора 8 поступил на вход разрешения записи регистра 5 и записал в него информацию о результатах идентификации.

При этом пользователь устройства может получить информацию на одном из выходов регистра 5 о том, какой сигнал поступил на вход устройства.

Вход 16 используется в случае необходимости выдачи на выход 17 промежуточных результатов контроля. При поступлении на этот вход единичного сигнала через элемент ИЛИ 6 разрешается запись информации из регистра 4 в регистр по импульсу с выхода генератора 8.

Единичные сигналы на выходах 17 соответствуют тем командам, которые еще могут быть идентифицированы до конца цикла контроля, а нулевые - подмножеству команд, которые не поступают в данном цикле.

Формула изобретения

Устройство для контроля сигналов, содержащее счетчик, блок памяти, причем группа разрядных выходов счетчика соединена с группой адресных входов блока памяти, отличающееся тем, что, с целью расширения функциональных возможностей за счет идентификации ошибки, в устройство введены группа элементов сложения по модулю два, два регистра, элемент ИЛИ, два триггера, генератор синхроимпульсов, два элемента запрета, элемент И и одновибратор, причем выходы эталонного значения блока памяти соединены с первыми входами элементов сложения по модулю два группы, группа выходов которых соединена с группой информационных

входов первого регистра, выход конца команды блока памяти соединен с информационным входом первого регистра, группа инверсных выходов первого регистра соединена с группой информационных входов второго регистра и группой входов разрешения записи первого и второго регистров, прямой выход первого триггера соединен с входом запуска генератора синхроимпульсов, первый тактовый выход которого соединен с первым входом элемента И, информационным входом первого элемента запрета и входом разрешения записи второго регистра, выход элемента И соединен с входом сброса в О счетчика и входом

одновибратора, выход первого элемента запрета соединен со счетным входом счетчика, старший прямой выход первого регистра соединен с вторым входом элемента И, управляющим входом первого элемента запрета, управляющим входом второго элемента запрета, первым входом элемента ИЛИ и старшим информационным входом второго регистра, второй тактовый выход генератора синхроимпульсов соединен с

синхровходом второго триггера, прямой выход которого соединен с вторыми входами элементов сложения по модулю два группы, первый тактовый выход генератора синхроимпульсовсоединен с информационным входом второго элемента запрета, выход которого соединен с входом разрешения записи первого регистра, выход одновибратора соединен с входом сброса в О первого регистра, вход установки в 1 первого тригера является входом начальной установки устройства, информационный вход второго триггера является входом контролируемого сигнала устройства, второй вход элемента ИЛИ является входом разрешения работы устройства, группа прямых выходов второго регистра является группой выходов ошибки контролируемой последовательности устройства, старший прямой выход второго регистра является

выходом сбоя устройства.

фиг.

Фиг. 3

| Устройство для контроля последовательности импульсов | 1983 |

|

SU1091346A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для контроля двух последовательностей импульсов | 1986 |

|

SU1376088A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-02-21—Подача