Изобретение относится к цифровой технике и может быть использовано для быстрого пересчета импульсов.

Целью изобретения является повышение быстродействия.

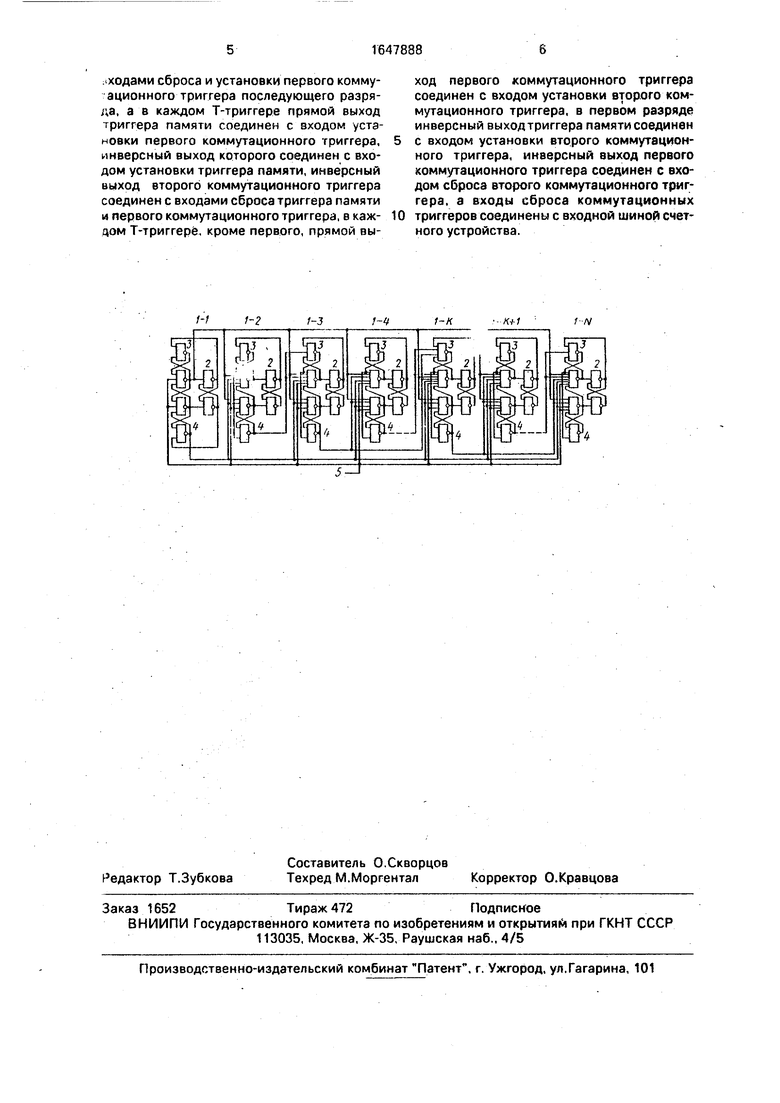

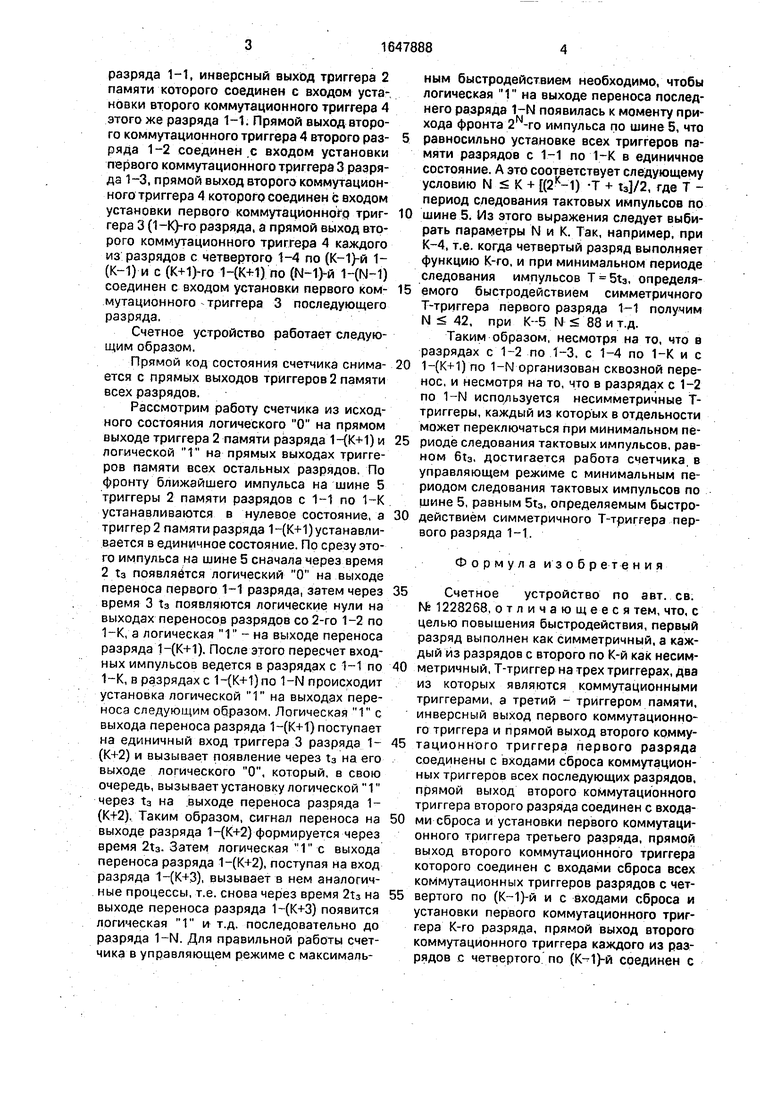

На чертеже приведена функциональная схема предлагаемого счетного устройства.

Счетное устройство содержит разряды 1-1 - 1-N, каждый из которых содержит триггер 2 памяти, первый 3 и второй 4 коммутационные триггеры, входную шину 5, каждый из триггеров разряда выполнен на паре логических элементов И-НЕ. В каждом из разрядов 1-1 - 1-N прямой выход триггера 2 памяти соединен с входом установки первого коммутационного триггера 3, инверсный выход которого соединен с входом установки триггера 2 памяти, инверсный выход второго коммутационного триггера 4 соединен с входами сброса триггера 2 памяти и первого коммутационного триггера 3. В каждом из разрядов 1-2 - 1-N прямой выход первого коммутационного триггера 3 со- едикен с входом установки второго коммутационного триггера 4, прямой выход второго коммутационного триггера 4 первого разряда 1-1 соединен с входами сброса

коммутационных триггеров 3 и 4 всех последующих разрядов 1-2 - 1-N. Прямой выход второго коммутационного триггера 4 второго разряда 1-2 соединен с входом сброса первого коммутационного триггера 3 третьего разряда 1-3, прямой выход второго коммутационного триггера 4 которого соединен с входами сброса коммутационных триггеров 3 и 4 разрядов с 1-4 по 1-(К-1) и с входом сброса первого коммутационного триггера 3(1-К)-го разряда. Прямой выход второго коммутационного триггера 4 каждого из разрядов с 1-4 по 1-(К-1)и с 1-{К+1) по 1-(N-1) соединен с входом сброса первого коммутационного триггера 3 последующего разряда. Прямой выход второго коммутационного триггера 4(1-К)-го разряда соединен с входами сброса коммутационных триггеров 3 и 4 всех последующих разрядов 1-(К+1)- 1-N. С входами сброса всех коммутационных триггеров 3 и 4 разрядов 1-1 - 1-N соединена входная шина 5. Инверсный выход первого коммутационного триггера 3 разряда 1-1 соединен с входами сброса коммутационных триггеров 3 и 4 всех последующих разрядов 1 -2 - 1-N и с входом сброса второго коммутационного триггера 4

Ё

ON

4 00 00 00

ГО

разряда 1-1, инверсный выход триггера 2 памяти которого соединен с входом установки второго коммутационного триггера 4 этого же разряда 1-1. Прямой выход второго коммутационного триггера 4 второго разряда 1-2 соединен с входом установки первого коммутационного триггера 3 разряда 1-3, прямой выход второго коммутационного триггера 4 которого соединен с входом установки первого коммутационного триггера 3 (1-К)-го разряда, а прямой выход второго коммутационного триггера 4 каждого из разрядов с четвертого 1-4 по (К-1)-й 1- (К-1) и с (К+1)-го 1-(К-И) по ( 1-(N-1) соединен с входом установки первого коммутационного триггера 3 последующего разряда.

Счетное устройство работает следующим образом.

Прямой код состояния счетчика снимается с прямых выходов триггеров 2 памяти всех разрядов.

Рассмотрим работу счетчика из исходного состояния логического О на прямом выходе триггера 2 памяти разряда 1-(К+1) и логической 1 на прямых выходах триггеров памяти всех остальных разрядов. По фронту ближайшего импульса на шине 5 триггеры 2 памяти разрядов с 1-1 по 1-К устанавливаются в нулевое состояние, а триггер 2 памяти разряда 1-(К+1) устанавливается в единичное состояние. По срезу этого импульса на шине 5 сначала через время 2 ta появляется логический О на выходе переноса первого 1-1 разряда, затем через время 3 ts появляются логические нули на выходах переносов разрядов со 2-го 1-2 по 1-К, а логическая 1 - на выходе переноса разряда 1-(К+1). После этого пересчет входных импульсов ведется в разрядах с 1-1 по 1-К, в разрядах с 1(К-И)по 1-N происходит установка логической 1 на выходах переноса следующим образом. Логическая 1 с выхода переноса разряда 1-(К+1) поступает на единичный вход триггера 3 разряда 1- (К+2) и вызывает появление через ta на его выходе логического О, который, в свою очередь, вызывает установку логической 1 через t3 на выходе переноса разряда 1- (К+2). Таким образом, сигнал переноса на выходе разряда 1-(К+2) формируется через время 2t3. Затем логическая 1 с выхода переноса разряда 1-(К+2), поступая на вход разряда 1-(К+3), вызывает в нем аналогичные процессы, т.е. снова через время 2t3 на выходе переноса разряда 1-(К+3) появится логическая 1 и т.д. последовательно до разряда 1-N. Для правильной работы счетчика в управляющем режиме с максимальным быстродействием необходимо, чтобы логическая 1 на выходе переноса последнего разряда 1-N появилась к моменту прихода фронта 2-го импульса по шине 5, что

равносильно установке всех триггеров памяти разрядов с 1-1 по 1-К в единичное состояние. А это соответствует следующему условию N К + (2к-1) -Т + , где Т - период следования тактовых импульсов по

шине 5. Из этого выражения следует выбирать параметры N и К. Так, например, при К-4, т.е. когда четвертый разряд выполняет функцию К-го, и при минимальном периоде следования импульсов Т 5t3, определяемого быстродействием симметричного Т-триггера первого разряда 1-1 получим N 42, при К-5 N 88 и т.д.

Таким образом, несмотря на то, что в разрядах с 1-2 по 1-3. с 1-4 по 1-К и с

1-(К+1) по 1-N организован сквозной перенос, и несмотря на то, что в разрядах с 1-2 по 1-N используется несимметричные Т- триггеры, каждый из которых в отдельности может переключаться при минимальном периоде следования тактовых импульсов, равном 6t3, достигается работа счетчика в управляющем режиме с минимальным периодом следования тактовых импульсов по шине 5, равным 5t3, определяемым быстродействием симметричного Т-триггера первого разряда 1-1.

Формула изобретения

Счетное устройство по авт. св. N° 1228268, отличающееся тем, что, с целью повышения быстродействия, первый разряд выполнен как симметричный, а каждый из разрядов с второго по К-й как несимметричный, Т-триггер на трех триггерах, два из которых являются коммутационными триггерами, а третий - триггером памяти, инверсный выход первого коммутационного триггера и прямой выход второго коммутационного триггера первого разряда соединены с входами сброса коммутационных триггеров всех последующих разрядов, прямой выход второго коммутационного триггера второго разряда соединен с входами сброса и установки первого коммутационного триггера третьего разряда, прямой выход второго коммутационного триггера которого соединен с входами сброса всех коммутационных триггеров разрядов с четвертого по (К-1)-й и с входами сброса и установки первого коммутационного триггера К-го разряда, прямой выход второго коммутационного триггера каждого из разрядов с четвертого по (К-1)-й соединен с

ходами сброса и установки первого комму- ационного триггера последующего разряда, а в каждом Т-триггере прямой выход триггера памяти соединен с входом установки первого коммутационного триггера, инверсный выход которого соединен с входом установки триггера памяти, инверсный выход второго коммутационного триггера соединен с входами сброса триггера памяти и первого коммутационного триггера, в каждом Т-триггере, кроме первого, прямой вы0

ход первого коммутационного триггера соединен с входом установки второго коммутационного триггера, в первом разряде инверсный выход триггера памяти соединен с входом установки второго коммутационного триггера, инверсный выход первого коммутационного триггера соединен с входом сброса второго коммутационного триггера, а входы сброса коммутационных триггеров соединены с входной шиной счетного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивное счетное устройство | 1989 |

|

SU1713100A1 |

| Реверсивный счетчик | 1981 |

|

SU1003356A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

| УПРАВЛЯЕМЫЙ ГЕНЕРАТОР С ПРЕДУСТАНОВКОЙ ЧАСТОТЫ | 1997 |

|

RU2121749C1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2020 |

|

RU2726497C1 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2018 |

|

RU2685985C1 |

| Устройство для построения программируемых логических автоматов | 2023 |

|

RU2814507C1 |

| Счетное устройство | 1987 |

|

SU1448407A2 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2006 |

|

RU2319192C2 |

Изобретение относится к цифровой технике и может быть использовано для быстрого пересчета импульсов Цель изобретения - повышение быстродействия. Цель достигается введением новых функциональных связей между схемными элементами. Устройство содержит разряды 1-1 - 1-N,каждый из которых содержит юиггер2 памяти и два коммутационных триггера 3 и 4, выполненные в базисе И-НЕ (ИЛИ-НЕ), входную шину 5 В описании изобретения приводится вариант реализации структуры в базисе элементов И-НЕ, 1 ил

/-/1-21-3

J

Ц1-К

К+1

1 N

| Счетное устройство | 1983 |

|

SU1228268A1 |

Авторы

Даты

1991-05-07—Публикация

1989-03-31—Подача