С

13

31

Выход Риг 1

Ю

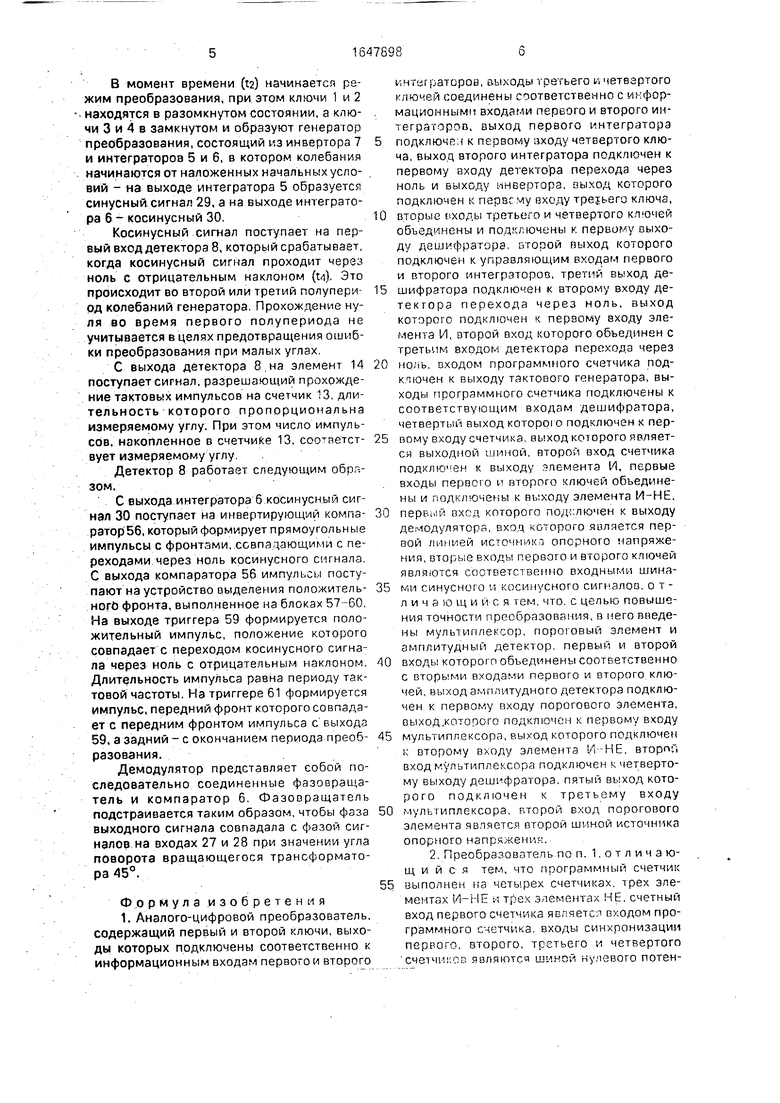

Изобретение относится к радиотехнике, в частности к аналого-цифровым преобразователям, применяемым для преобразования сигналов, поступающих от вращающегося трансформатора или реша- ющего устройства, в цифровые угловые величины, и может быть использовано в автоматических радиокомпасах, радиопеленгаторах, гирокомпасах и других устройствах.

Целью изобретения является повышение точности преобразования.

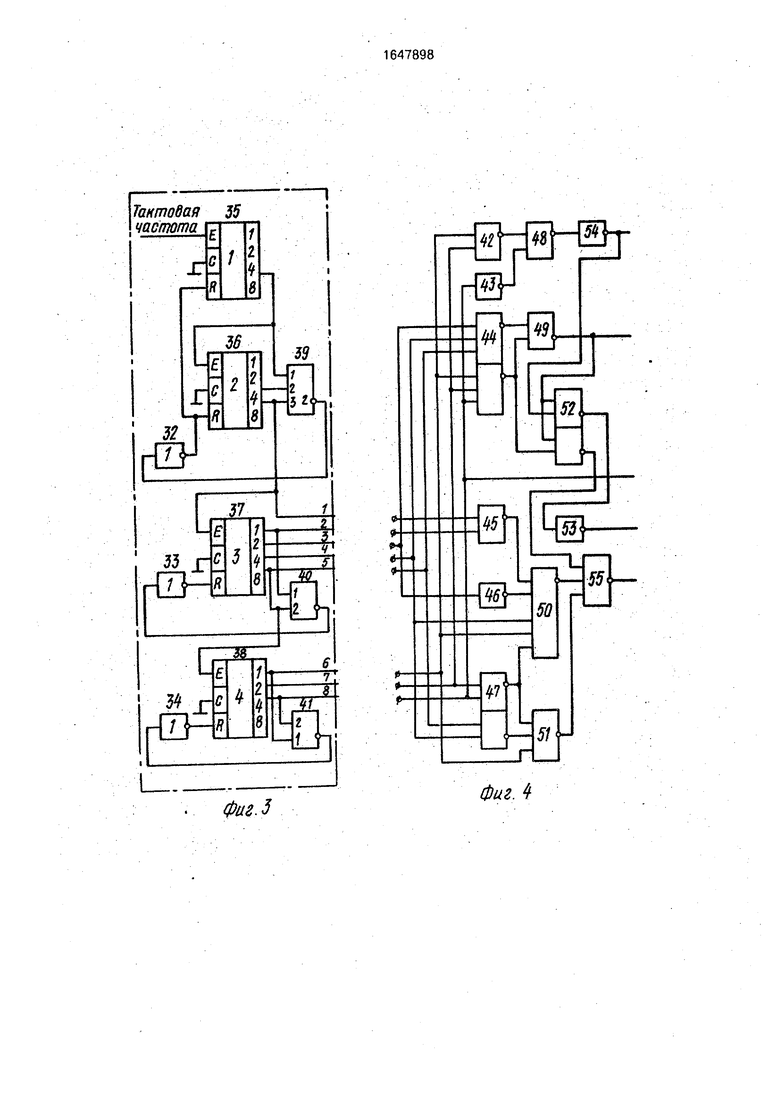

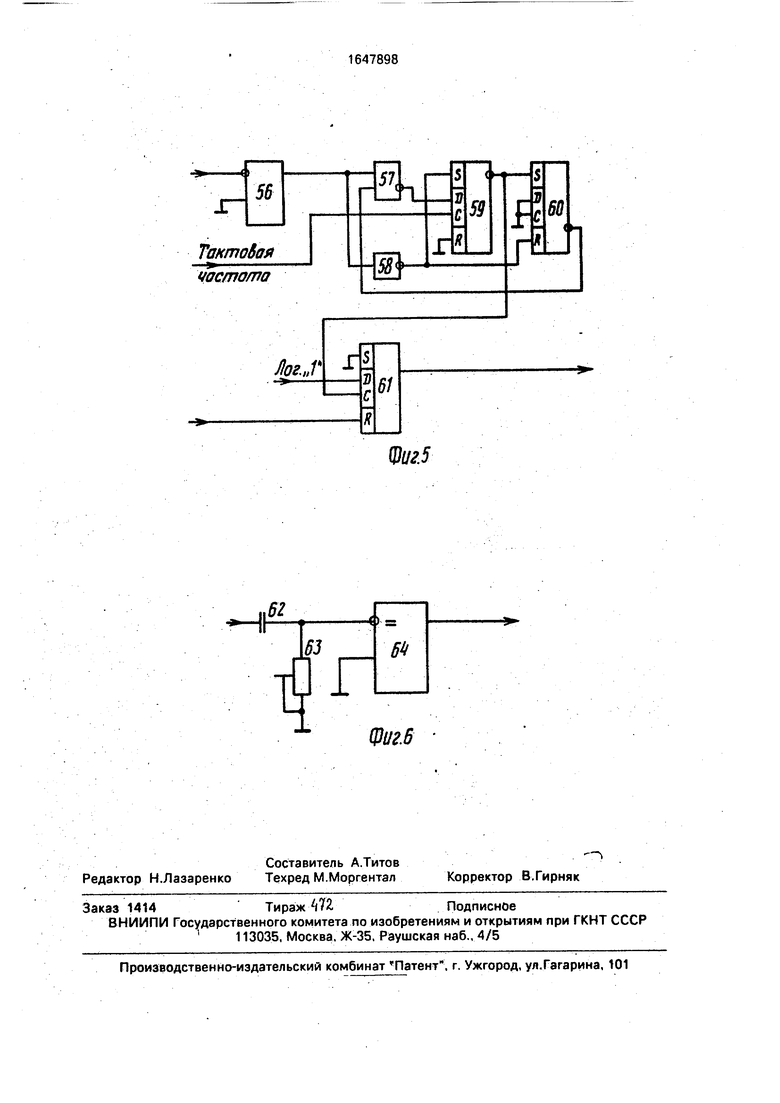

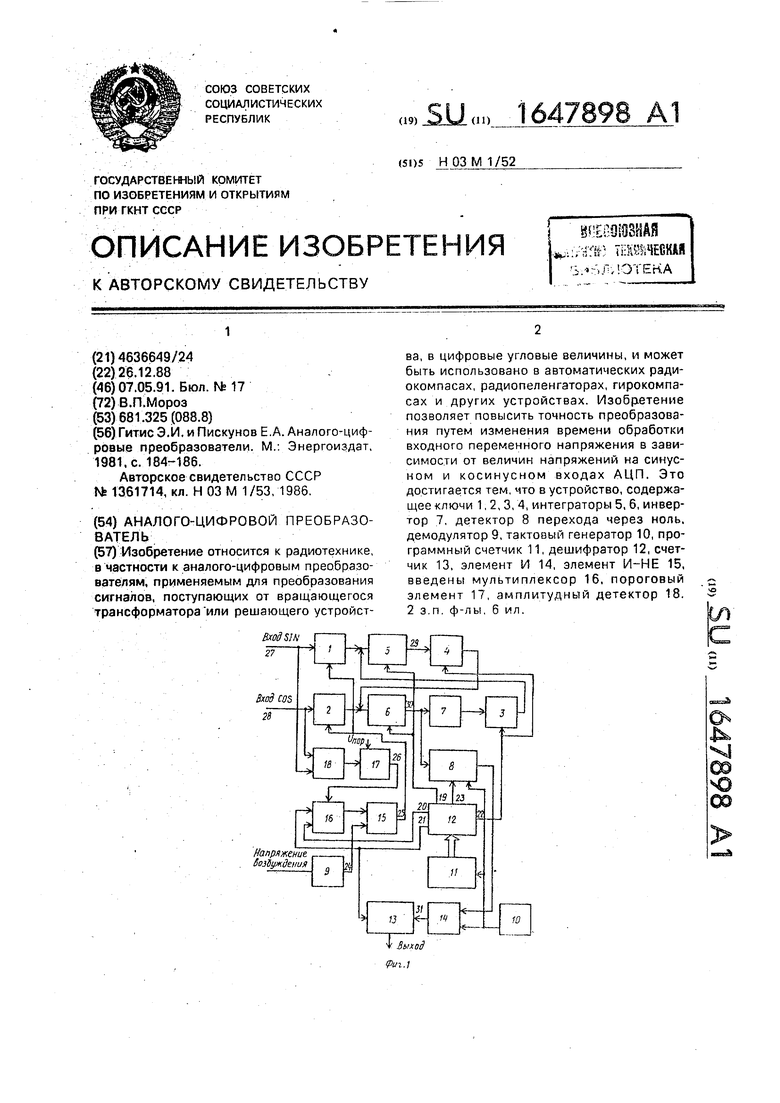

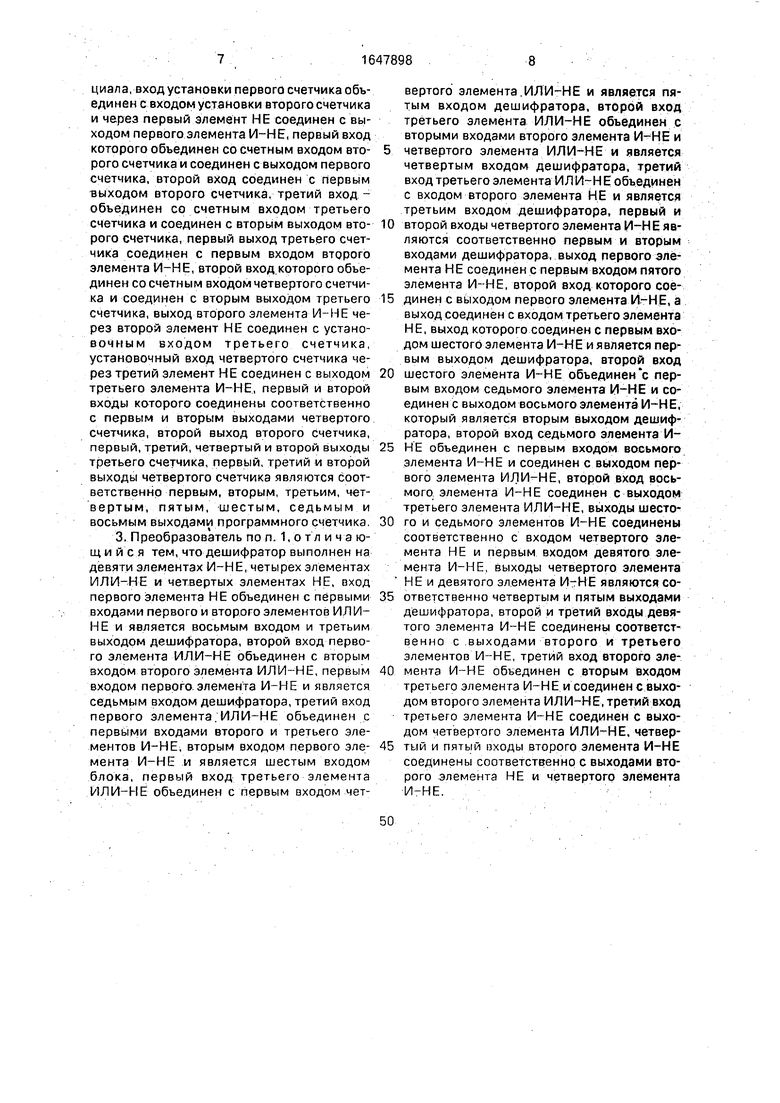

На фиг. 1 приведена функциональная схема АЦП; на фиг. 2 - диаграмма работы АЦП; на фиг, 3 -функциональная схема про- граммного счетчика; на фиг. 4 - функциональная схема дешифратора; на фиг 5 - функциональная схема детектора перехода через ноль; на фиг. 6 - принципиальная электрическая схема демодулятора.

Устройство содержит ключи 1-4, интеграторы 5 и 6, инвертор 7, детектор 8 перехода через ноль, демодулятор 9, тактовый генератор 10, программный счетчик 11, дешифратор 12, счетчик 13, элемент И 14, эле- мент И-НЕ 15, мультиплексор 16, пороговый элемент 17, амплитудный детектор 18.

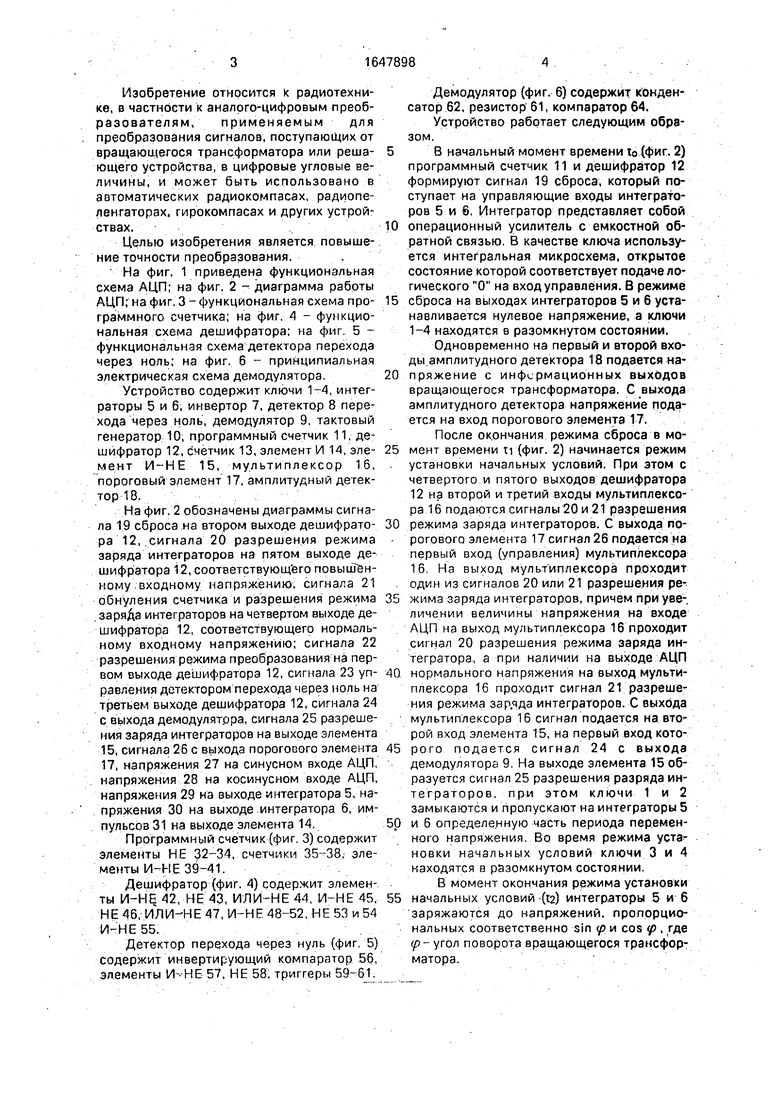

На фиг. 2 обозначены диаграммы сигнала 19 сброса на втором выходе дешифрато- ра 12, сигнала 20 разрешения режима заряда интеграторов на пятом выходе дешифратора 12, соответствующ его повышенному входному напряжению, сигнала 21 обнуления счетчика и разрешения режима заряда интеграторов на четвертом выходе дешифратора 12, соответствующего нормальному входному напряжению; сигнала 22 разрешения режима преобразования на первом выходе дешифратора 12, сигнала 23 уп- равления детектором перехода через ноль на третьем выходе дешифратора 12, сигнала 24 с выхода демодулятора, сигнала 25 разрешения заряда интеграторов на выходе элемента 15, сигнала 26 с выхода порогового элемента 17, напряжения 27 на синусном входе АЦП, напряжения 28 на косинусном входе АЦП, напряжения 29 на выходе интегратора 5, напряжения 30 на выходе интегратора 6, импульсов 31 на выходе элемента 14.

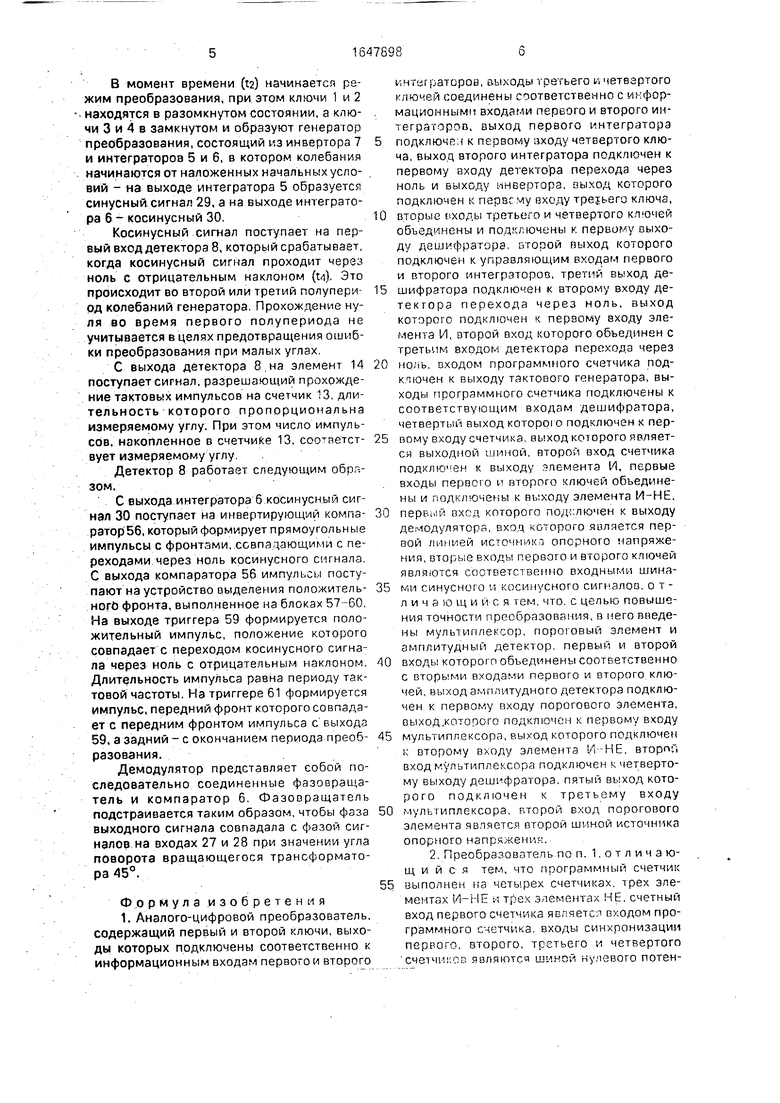

Программный счетчик (фиг. 3) содержит элементы НЕ 32-34, счетчики 35-38, элементы И-НЕ 39-41.

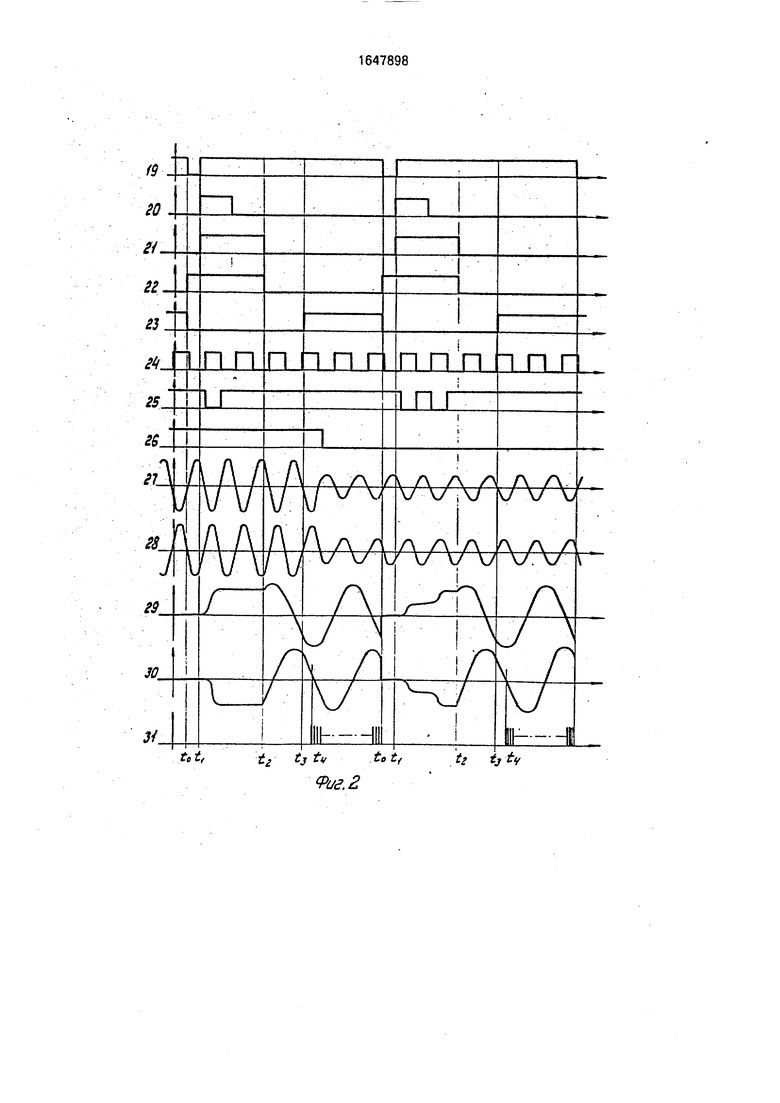

Дешифратор (фиг. 4) содержит элементы И-НЕ 42, НЕ 43, ИЛИ-НЕ 4-1, И-НЕ 45, НЕ 46, 47, И-НЕ 48-52, НЕ 53 и 54 И-НЕ 55.

Детектор перехода через нуль (фиг, 5) содержит инвертирующий компаратор 56, элементы И--НЕ 57, НЕ 58, триггеры 59-61.

Демодулятор (фиг. 6) содержит конденсатор 62, резистор 61, компаратор 64.

Устройство работает следующим образом.

В начальный момент времени to (фиг. 2) программный счетчик 11 и дешифратор 12 формируют сигнал 19 сброса, который поступает на управляющие входы интеграторов 5 и S, Интегратор представляет собой операционный усилитель с емкостной обратной связью. В качестве ключа используется интегральная микросхема, открытое состояние которой соответствует подаче логического О на вход управления. В режиме сброса на выходах интеграторов 5 и 6 устанавливается нулевое напряжение, а ключи 1-4 находятся в разомкнутом состоянии.

Одновременно на первый и второй входы амплитудного детектора 18 подается напряжение с информационных выходов вращающегося трансформатора. С выхода амплитудного детектора напряжение подается на вход порогового элемента 17.

После окончания режима сброса в момент времени ti (фиг. 2) начинается режим установки начальных условий. При этом с четвертого и пятого выходов дешифратора 12 на второй и третий входы мультиплексора 16 подаются сигналы 20 и 21 разрешения режима заряда интеграторов. С выхода порогового элемен га 17 сигнал 26 подается на первый вход (управления) мультиплексора 16 На выход мультиплексора проходит один из сигналов 20 или 21 разрешения режима заряда интеграторов, причем приуве-. личении величины напряжения на входе АЦП на выход мультиплексора 16 проходит CHI нал 20 разрешения режима заряда интегратора, а при наличии на выходе АЦП нормального напряжения на выход мультиплексора 16 проходит сигнал 21 разрешения режима зар.яда интеграторов. С выхода мультиплексора 16 сигнал подается на второй вход элемента 15, на первый вход которого подается сигнал 24 с выхода демодулятора 9, На выходе элемента 15 образуется сигнал 25 разрешения разряда интеграторов, при этом ключи 1 и 2 замыкаются и пропускают на интеграторы 5 и 6 определенную часть периода переменного напряжения. Во время режима установки начальных условий ключи 3 и 4 находятся в разомкнутом состоянии.

В момент окончания режима установки начальных условий (t2) интеграторы 5 и 6 заряжаются до напряжений, пропорциональных соответственно sin f и cos p , где угол поворота вращающегося трансформатора.

В момент времени (ta) начинается реим преобразования, при этом ключи 1 и 2 аходятся в разомкнутом состоянии, а клюи 3 и 4 в замкнутом и образуют генератор преобразования, состоящий из инвертора 7 и интеграторов 5 и 6, в котором колебания начинаются от наложенных начальных условий - на выходе интегратора 5 образуется синусный сигнал 29, а на выходе интегратора 6 - косинусный 30.

Косинусный сигнал поступает на первый вход детектора 8, который срабатывает, когда косинусный сигнал проходит через ноль с отрицательным наклоном (). Это происходит во второй или третий полуперид колебаний генератора. Прохождение нуя во время первого полупериода не учитывается в целях предотвращения ошибки преобразования при малых углах.

С выхода детектора 8 на элемент 14 поступает сигнал, разрешающий прохождение тактовых импульсов на счетчик 13, длиельность которого пропорциональна змеряемому углу. При этом число импульсов, накопленное в счетчике 13, соотаетст- вует измеряемому углу.

Детектор 8 работает следующим образом.

С выхода интегратора б косинусный сигнал 30 поступает на инвертирующий компаратор 56, который формирует прямоугольные импульсы с фронтами, совпадающими с переходами через ноль косинусного сигнала. С выхода компаратора 56 импульсы поступают на устройство выделения положительного фронта, выполненное на блоках 57-60. На выходе триггера 59 формируется положительный импульс, положение которого совпадает с переходом косинусного сигнала через ноль с отрицательным наклоном. Длительность импульса равна периоду тактовой частоты. На триггере 61 формируется импульс, передний фронт которого совпадает с передним фронтом импульса с выхода 59, а задний - с окончанием периода преобразования.

Демодулятор представляет собой последовательно соединенные фазовращатель и компаратор 6. Фазовращатель подстраивается таким образом, чтобы фаза выходного сигнала совпадала с фазой сигналов на входах 27 и 28 при значении угла поворота вращающегося трансформатора 45°.

Формула изобретения 1. Аналого-цифровой преобразователь, содержащий первый и второй ключи, выходы которых подключены соответственно к информационным входам первого и второго

интеграторов, выходы третьего и четвертого ключей соединены соответственно с информационными входами первого и второго интеграторов, выход первого интегратора

подключен к первому аходу четвертого ключа, выход второго интегратора подключен к первому входу детектора перехода через ноль и выходу инвертора, выход которого подключен к первому входу Tpejbero ключа,

0 вторые пходы третьего и четвертого ключей объединены и подключены к. первому выходу дешифратора. г горой выход которого подключен к управляющим входам первого и второго интеграторов, третий выход де5 шифратора подключен к второму входу детектора перехода через ноль, выход которого подключен к первому входу элемента И, второй вход которого объединен с третьим входом детектора перехода через

0 ноль, сходом программного счетчика под- кточен к выходу тактового генератора, выходы программного счетчика подключены к соответствующим входам дешифратора, четвертый выход которою подключен к пер5 вому входу счетчика, выход которого является выходной шиной, второй вход счетчика подключен к выходу элемента И, первые входы первою и второго ключей объединены и подключены к выходу элемента И-НЕ.

0 первой вход которого подключен к выходу демодулятора, вхоц которого является первой линией источник оперного напряжения, вторые входы первого и второго ключей являются соответственно входными шинз5 ми синусного и косинусного сигналов, отличающийся тем, что. с целью повышения точности преобразования, в пего введены мультиплексор, пороювый элемент и амплитудный детектор, первый и второй

0 входы которого объединены соответственно с вторыми вводами первого и второго ключей, выход амплитудного детектора подключен к первому входу порогового элемента, оыхоД.которого подключен к первому входу

5 мультиплексора, выход которого подключен к второму входу элемента t/l-НЕ, вторлГ; вход мультиплексора подключен ч четвертому выходу дешифратора, пятый выход которого подключен к третьему входу

0 мулыиплексора, второй вход порогового элемента является второй шиной источника опорного напряжения.

2. Преобразоватепь по п. 1, о т л и ч а ю- щ и и с я тем, что программный счетчик

5 выполнен на четырех счетчиках, трех элементах И-НЕ vi трех .элементах НЕ, счетный вход первого счетчика является входом программного счетчика, входы синхронизации псрвого, второго, третьего и четвертого счетчиков являются шиной кулевого потенциала, вход установки первого счетчика объединен с входом установки второго счетчика и через первый элемент НЕ соединен с выходом первого элемента И-НЕ, первый вход которого объединен со счетным входом второго счетчика и соединен с выходом первого счетчика, второй вход соединен с первым выходом второго счетчика, третий вход - объединен со счетным входом третьего счетчика и соединен с вторым выходом второго счетчика, первый выход третьего счетчика соединен с первым входом второго элемента И-НЕ, второй вход которого объединен со счетным входом четвертого счетчика и соединен с вторым выходом третьего счетчика, выход второго элемента И-НЕ через второй элемент НЕ соединен с установочным входом третьего счетчика, установочный вход четвертого счетчика через третий элемент НЕ соединен с выходом третьего элемента И-НЕ, первый и второй входы которого соединены соответственно с первым и вторым выходами четвертого счетчика, второй выход второго счетчика, первый, третий, четвертый и второй выходы третьего счетчика, первый, третий и второй выходы четвертого счетчика являются соответственно первым, вторым, третьим, четвертым, пятым, шестым, седьмым и восьмым выходами программного счетчика. 3, Преобразователь по п. 1, о т л и ч a tool и и с я тем, что дешифратор выполнен на девяти элементах И-НЕ, четырех элементах ИЛ И-НЕ и четвертых элементах НЕ, вход первого элемента НЕ объединен с первыми входами первого и второго элементов ИЛИ- НЕ и является восьмым входом и третьим выходом дешифратора, второй вход первого элемента ИЛИ-НЕ объединен с вторым входом второго элемента ИЛИ-НЕ, первым входом первого элемента И-НЕ и является седьмым входом дешифратора, третий вход первого элемента. ИЛИ-НЕ объединен с первыми входами второго и третьего элементов И-НЕ, вторым входом первого элемента И-НЕ и является шестым входом блока, первый вход третьего элемента ИЛИ-НЕ объединен с первым входом четвертого элемента.ИЛИ-НЕ и является пятым входом дешифратора, второй вход третьего элемента ИЛИ-НЕ объединен с вторыми входами второго элемента И-НЕ и

четвертого элемента ИЛИ-НЕ и является четвертым входом дешифратора, третий вход третьего элемента ИЛ И-Н Е объединен с входом второго элемента НЕ и является третьим входом дешифратора, первый и

второй входы четвертого элемента И-НЕ являются соответственно первым и вторым входами дешифратора, выход первого элемента НЕ соединен с первым входом пятого элемента И-НЕ, второй вход которого соединен с выходом первого элемента И-НЕ, а выход соединен с входом третьего элемента НЕ, выход которого соединен с первым входом шестого элемента И-НЕ и является первым выходом дешифратора, второй вход

шестого элемента И-НЕ объединен с первым входом седьмого элемента И-НЕ и соединен с выходом восьмого элемента И-НЕ, который является вторым выходом дешифратора, второй вход седьмого элемента ИНЕ объединен с первым входом восьмого элемента И-НЕ и соединен с выходом первого элемента ИЛИ-НЕ, второй вход восьмого элемента И-НЕ соединен с выходом третьего элемента ИЛИ-НЕ, выходы шестого и седьмого элементов И-НЕ соединены соответственно с входом четвертого элемента НЕ и первым входом девятого элемента И-НЕ, выходы четвертого элемента НЕ и девятого элемента И-НЕ являются соответственно четвертым и пятым выходами дешифратора, второй и третий входы девятого элемента И-НЕ соединены соответственно с выходами второго и третьего элементов И-НЕ, третий вход второго элемента И-НЕ объединен с вторым входом третьего элемента И-НЕ и соединен с выходом второго элемента ИЛИ-НЕ, третий вход третьего элемента И-НЕ соединен с выходом четвертого элемента ИЛИ-НЕ, четвертый и пятый входы второго элемента И-НЕ соединены соответственно с выходами второго элемента НЕ и четвертого элемента И-НЕ.

f9

J/

tz tj tf

Фиг. 2

р«Ь 4вНШт

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1986 |

|

SU1361714A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Многоканальное измерительное устройство | 1988 |

|

SU1617430A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В ИНТЕРВАЛЫ ВРЕМЕНИ | 2014 |

|

RU2552605C1 |

| Устройство цифровой релейной защиты | 1983 |

|

SU1252860A1 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Устройство для кодирования сигналов звукового вещания | 1990 |

|

SU1774500A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

Изобретение относится к радиотехнике, в частности к аналого-цифровым преобразователям, применяемым для преобразования сигналов, поступающих от вращающегося трансформатора или решающего устройства, в цифровые угловые величины, и может быть использовано в автоматических радиокомпасах, радиопеленгаторах, гирокомпасах и других устройствах. Изобретение позволяет повысить точность преобразования путем изменения времени обработки входного переменного напряжения в зависимости от величин напряжений на синусном и косинусном входах АЦП. Это достигается тем, что в устройство, содержащее -ключи 1,2,3, 4, интеграторы 5, 6, инвертор 7, детектор 8 перехода через ноль, демодулятор 9, тактовый генератор 10, программный счетчик 11, дешифратор 12, счетчик 13, элемент И 14, элемент И-НЕ 15, введены мультиплексор 16, пороговый элемент 17, амплитудный детектор 18. 2 з п, ф-лы, б ил. (Л Чзетэ

Фиг.З

з

®

SO

55

Г

ЯН

Фиг 4

Тактоба

час/по/яа

Щиг.5

Фиг.б

| Гитис Э.И, и Пискунов Е.А | |||

| Аналого-цифровые преобразователи | |||

| М.: Энергоиздат, 1981, с | |||

| Переносная печь-плита | 1920 |

|

SU184A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1361714A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-07—Публикация

1988-12-26—Подача