Изобретение относится к цифровой ехнике и может использоваться для онтроля блоков ЦВМ, содержап;их микророцессорные БИС.

Цель изобретения - повышение досоверности контроля.

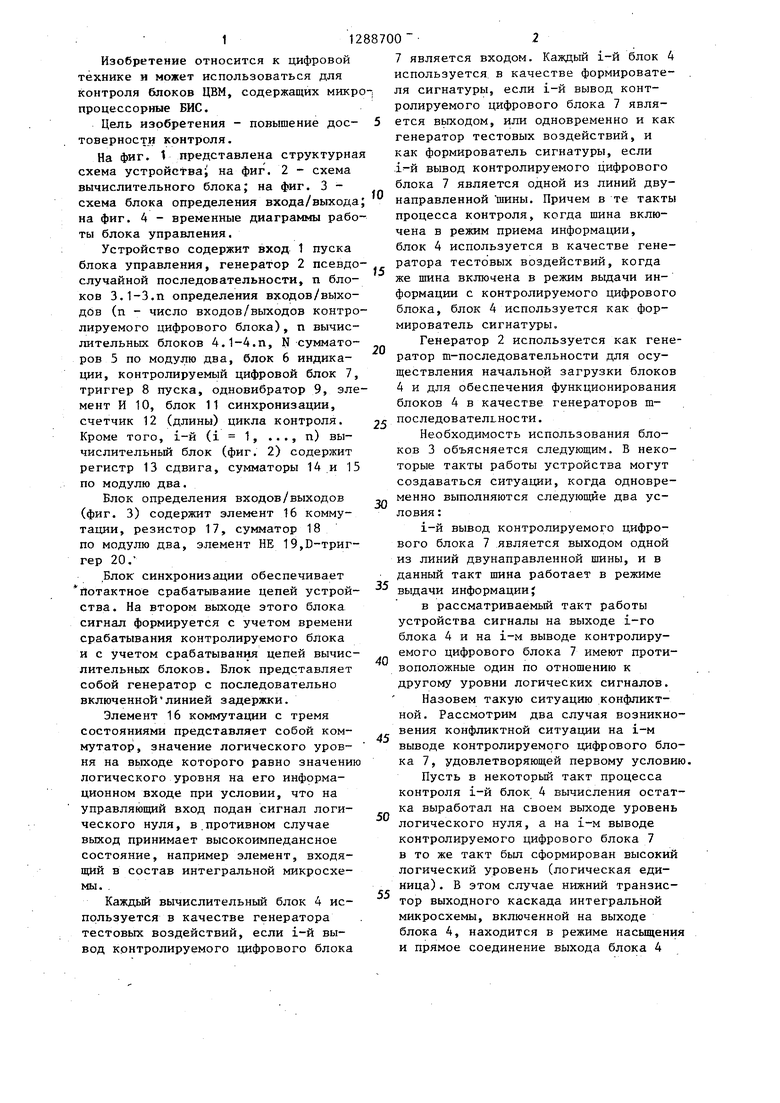

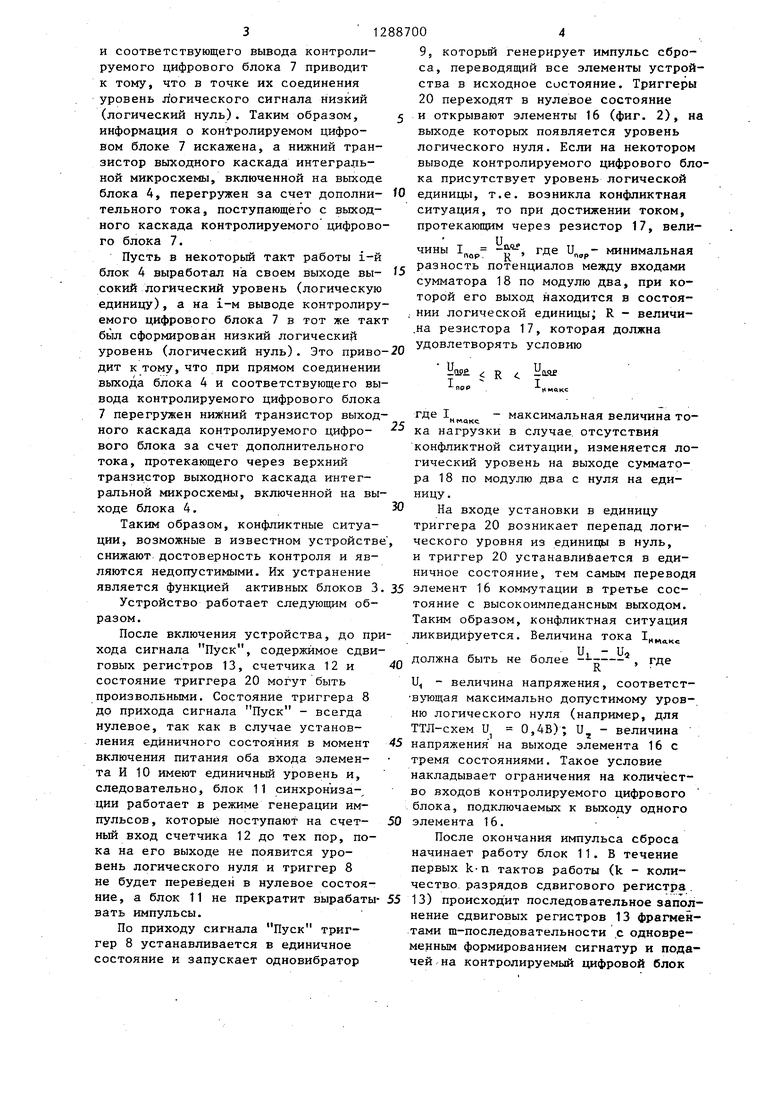

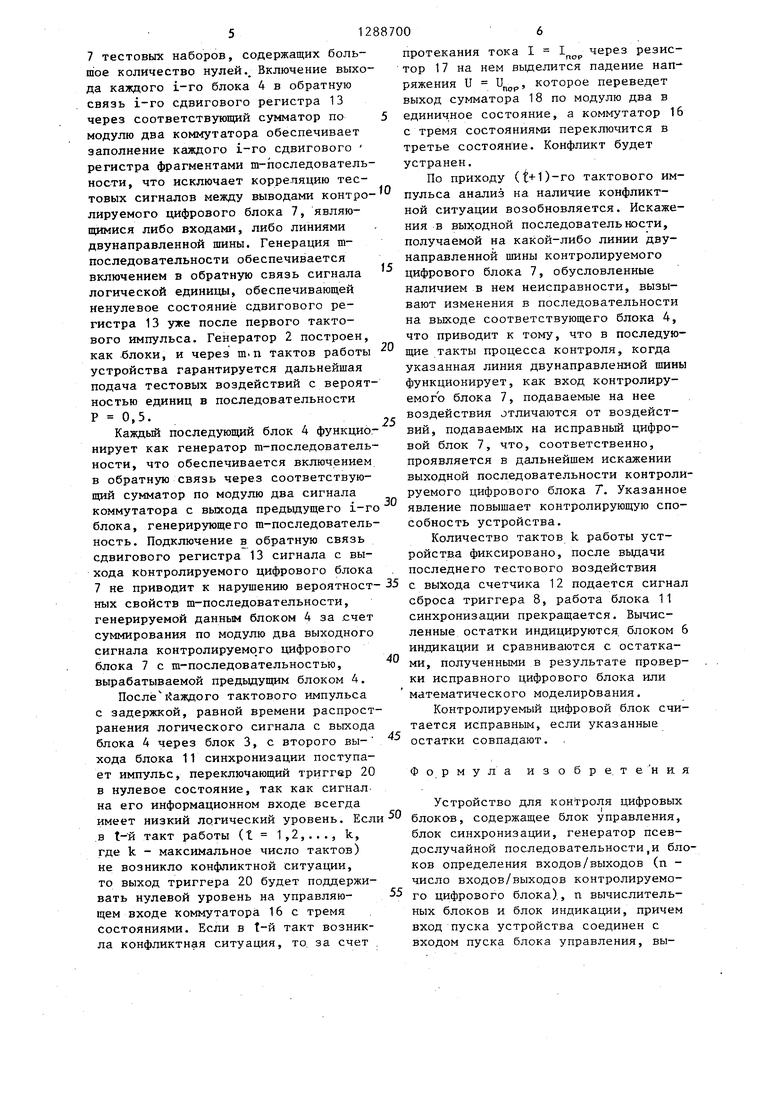

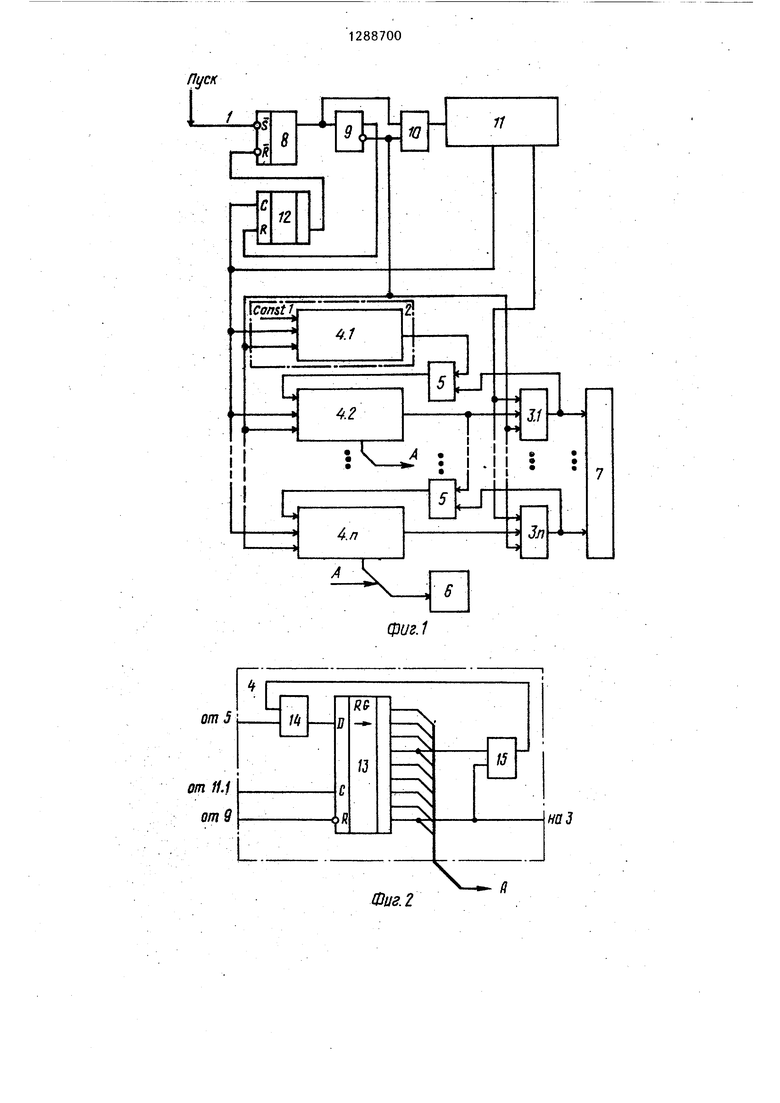

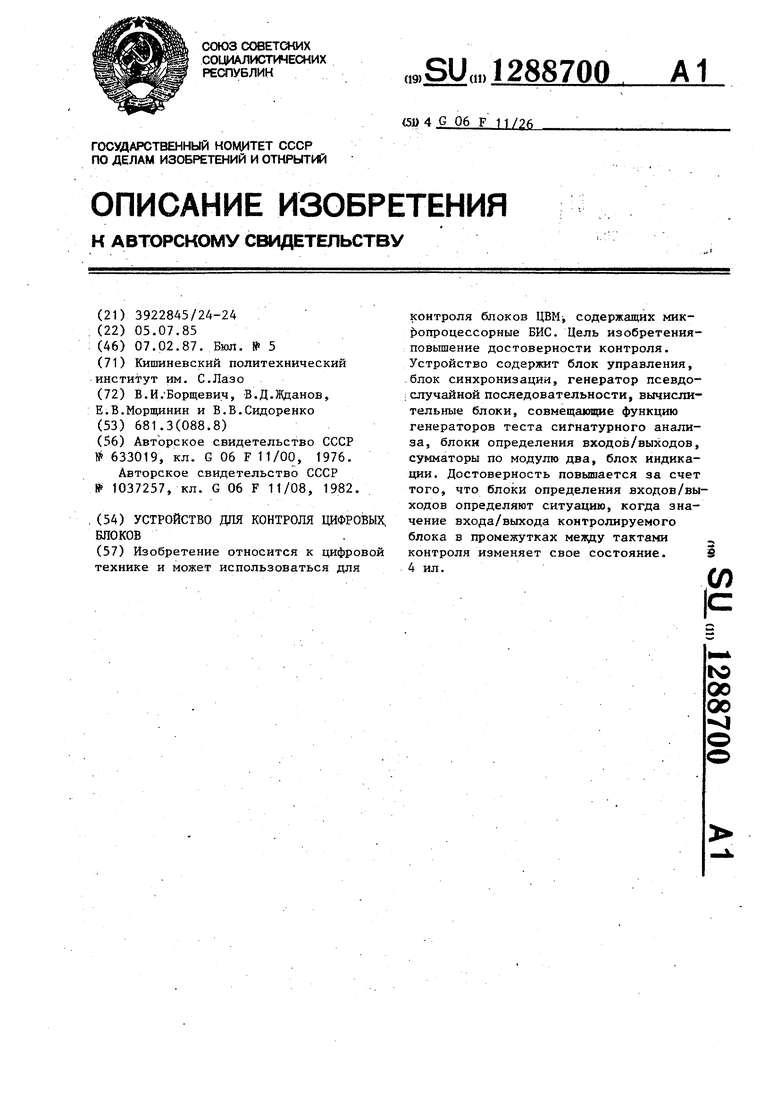

На фиг. 1 представлена структурная хема устройстваi на фиг. 2 - схема ычислительного блока; на фиг. 3 - хема блока определения входа/выхода; на фиг. 4 - временные диаграммы работы блока управления.

Устройство содержит вход 1 пуска блока управления, генератор 2 псевдослучайной последовательности, п блоков 3.1-З.п определения входов/выхоов (п - число входОБ/выходон контроируемого цифрового блока), п вычислительных блоков 4.1-4.П, N сумматоров 5 по модулю два, блок 6 индикации, контролируемый цифровой блок 7, триггер 8 пуска, одновибратор 9, элемент И 10, блок 11 синхронизации, счетчик 12 (длины) цикла контроля. Кроме того, i-й (i 1, ..., п) вы- числительньй блок (фиг. 2) содержит регистр 13 сдвига, сумматоры 14 и 15 по модулю два.

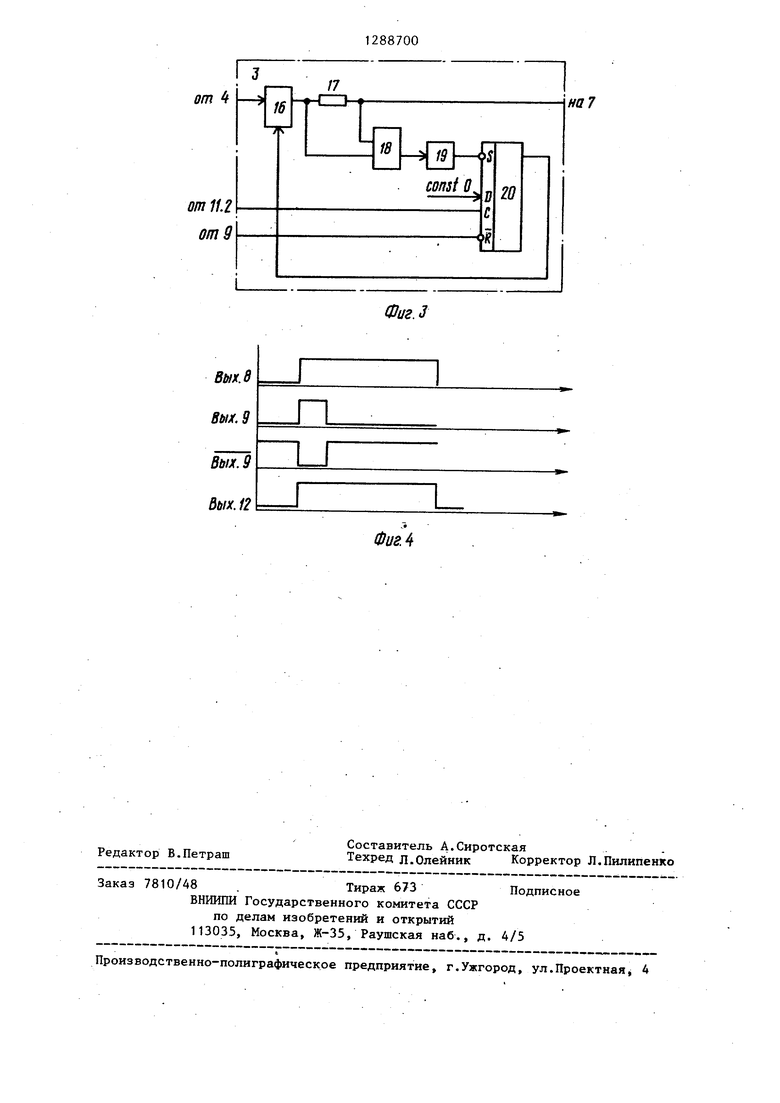

Блок определения входов/выходов (фиг. 3) содержит элемент 16 коммутации, резистор 17, сумматор 18 по модулю два, элемент НЕ 19,В-триг- гер 20.

.Блок синхронизации обеспечивает потактное срабатывание цепей устройства . На втором выходе этого блока сигнал формируется с учетом времени срабатывания контролируемого блока и с учетом срабатывания цепей вычисительных блоков. Блок представляет собой генератор с последовательно включенной линией задержки.

Элемент 16 коммутации с тремя состояниями представляет собой коммутатор, значение логического уров- ня на выходе которого равно значению логического уровня на его информационном входе при условии, что на управляющий вход подан сигнал логического нуля, в.противном случае выход принимает высокоимпедансное состояние, например элемент, входящий в состав интегральной микросхемы. ,

Каждьш вычислительный блок 4 используется в качестве генератора тестовых воздействий, если i-й вывод контролируемого цифрового блока

7 является входом. Каждый i-й блок 4 используется в качестве формирователя сигнатуры, если i-й вывод контролируемого цифрового блока 7 является вьгходом, или одновременно и как генератор тестовых воздействий, и как формирователь сигнатуры, если 1-й вывод контролируемого цифрового блока 7 является одной из линий двунаправленной шины. Причем в те такты процесса контроля, когда шина включена в режим приема информации, блок 4 используется в качестве генератора тестовых воздействий, когда же шина включена в режим выдачи информации с контролируемого цифрового блока, блок 4 используется как формирователь сигнатуры.

Генератор 2 используется как генератор т-последовательности для осуществления начальной загрузки блоков 4 и для обеспечения функционирования блоков 4 в качестве генераторов тпоследовательности.

Необходимость использования блоков 3 объясняется следующим. В некоторые такты работы устройства могут создаваться ситуации, когда одновре

0

0

5

0

5

менно выполняются следующие два условия :

i-й вывод контролируемого цифрового блока 7 является выходом одной из линий двунаправленной шины, и в данный такт шина работает в режиме выдачи информацииJ

в рассматриваемьй такт работы устройства сигналы на выходе i-ro блока 4 и на i-м выводе контролируемого цифрового блока 7 имеют противоположные один по отношению к другому уровни логических сигналов.

Назовем такую ситуацию конфликтной. Рассмотрим два случая возникновения конфликтной ситуации на i-м выводе контролируемого цифрового блока 7, удовлетворяющей первому условию.

Пусть в некоторый такт процесса контроля i-й блок 4 вычисления остатка выработал на своем выходе уровень логического нуля, а на i-м выводе контролируемого цифрового блока 7 в то же такт был сформирован высокий логический уровень (логическая единица) . В этом случае нижний транзистор выходного каскада интегральной микросхемы, включенной на выходе блока 4, находится в режиме насыщения и прямое соединение выхода блока 4

и соответствующего вывода контролируемого цифрового блока 7 приводит к тому, что в точке их соединения уровень jforH4ecKoro сигнала низкий (логический нуль). Таким образом, информация о контролируемом цифровом блоке 7 искажена, а нижний тран9, которьй генерирует импульс сбро са, переводящий все элементы устро ства в исходное состояние. Триггер 20 переходят в нулевое состояние 5 и открывают элементы 16 (фиг. 2), выходе которых появляется уровень логического нуля. Если на некоторо выводе контролируемого цифрового б ка присутствует уровень логической единицы, т.е. возникла конфликтная ситуация, то при достижении током, протекающим через резистор 17, вел

зистор выходного каскада интегральной микросхемы, включенной на выходе блока 4, перегружен за счет дополни- fO тельного тока, поступающего с выходного каскада контролируемого цифрового блока 7.

Пусть в некоторый такт работы i-й

.,с разность потенциалов между входами

блок 4 выработал на своем выходе вы- -

чины 1пор ГД пор минимальна

сумматора 18 по модулю два, при которой его выход находится в состоянии логической единицы; R - величи- .на резистора 17, которая должна удовлетворять условию

сокий логический уровень (логическую единицу), а на i-м выводе контролируемого цифрового блока 7 в тот же такт бьш сформирован низкий логический уровень (логический нуль). Это приводит к тому, что при прямом соединении выхода блока 4 и соответствующего вывода контролируемого цифрового блока 7 перегружен нижний транзистор выходного каскада контролируемого цифро- вого блока за счет дополнительного тока, протекающего через верхний транзистор выходного каскада интегральной микросхемы, включенной на выходе блока 4.

Таким образом, конфликтные ситуации, возможные в известном устройстве снижают достоверность контроля и являются недопустимыми. Их устранение

является функцией активных блоков 3. 35 элемент 16 коммутации в третье сосУстройство работает следующим образом.

После включения устройства, до прихода сигнала Пуск, содержимое сдви

говых регистров 13, счетчика 12 и состояние триггера 20 могут быть произвольными. Состояние триггера 8 до прихода сигнала Пуск - всегда нулевое, так как в случае установления единичного состояния в момент включения питания оба входа элемента И 10 имеют единичный уровень и, следовательно, блок 11 синхрониза-, ции работает в режиме генерации импульсов, которые поступают на счетный вход счетчика 12 до тех пор, пока на его выходе не появится уровень логического нуля и триггер 8 не будет переведен в нулевое состояние , а блок 11 не прекратит вырабаты вать импульсы.

По приходу сигнала Пуск триггер 8 устанавливается в единичное состояние и запускает одновибратор

87004

9, которьй генерирует импульс сброса, переводящий все элементы устройства в исходное состояние. Триггеры 20 переходят в нулевое состояние 5 и открывают элементы 16 (фиг. 2), на выходе которых появляется уровень логического нуля. Если на некотором выводе контролируемого цифрового блока присутствует уровень логической единицы, т.е. возникла конфликтная ситуация, то при достижении током, протекающим через резистор 17, велиfO разность потенциалов между входами

чины 1пор ГД пор минимальная

сумматора 18 по модулю два, при которой его выход находится в состоянии логической единицы; R - величи- .на резистора 17, которая должна удовлетворять условию

R

Уа..Е

- максимальная величина тогде I

нглаке

ка нагрузки в случае, отсутствия конфликтной ситуации, изменяется логический уровень на выходе сумматора 18 по модулю два с нуля на единицу .

На входе установки в единицу триггера 20 возникает перепад логического уровня из единицы в нуль, и триггер 20 устанавлибается в единичное состояние, тем самым переводя

40

5

тояние с высокоимпедансным выходом. Таким образом, конфликтная ситуация ликвидируется. Величина тока 1„„а.кс

- и. - Ua

должна быть не более - --, где

R

5

Ц - величина напряжения, соответст- в тощая максимально допустимому уровню логического нуля (например, для ТТЛ-схем и 0,4В); U - величина 5 напряжения на выходе элемента 16 с тремя состояниями. Такое условие накладывает ограничения на количество входов контролируемого цифрового блока, подключаемЕлх к выходу одного элемента 16.

После окончания импульса сброса начинает работу блок 11. В течение первых k-n тактов работы (k - количество, разрядов сдвигового регистра. 13) происходит последовательное заполнение сдвиговых регистров 13 фрагментами т-последовательности с одновременным формированием сигнатур и подачей на контролируемый цифровой блок

0

.

7 тестовых наборов, содержащих большое количество нулей.. Включение выхода каждого i-ro блока 4 в обратную связь i-ro сдвигового регистра 13 через соответствующий сумматор по модулю два коммутатора обеспечивает заполнение каждого i-ro сдвигового регистра фрагментами т-последователь ности, что исключает корреляцию тестовых сигналов между выводами контро лируемого цифрового блока 7, являющимися либо входами, либо линиями двунаправленной шины. Генерация т- последовательности обеспечивается включением в обратную связь сигнала логической единицы, обеспечивающей ненулевое состояние сдвигового регистра 13 уже после первого тактового импульса. Генератор 2 построен, как .блоки, и через m.n тактов работы устройства гарантируется дальнейшая подача тестовых воздействий с вероятностью единиц в последовательности Р 0,5.

Каждьй последующий блок 4 функционирует как генератор т-последователь ности, что обеспечивается включением в обратную связь через соответствующий сумматор по модулю два сигнала коммутатора с выхода предьщущего i-r блока, генерирующего т-последователь ность. Подключение в обратную связь сдвигового регистра 13 сигнала с выхода контролируемого цифрового блока 7 не приводит к нарушению вероятност ных свойств т-последовательности, генерируемой данным блоком 4 за счет суммирования по модулю два выходного сигнала контролируемо,го цифрового блока 7 с т-последовательностью, вырабатываемой предьщущим блоком 4.

Послё Каждого тактового импульса с задержкой, равной времени распространения логического сигнала с выхода блока 4 через блок 3, с второго вы- хода блока 11 синхронизации поступает импульс, переключающий триггер 20 в нулевое состояние, так как сигнал на его информационном входе всегда имеет низкий логический уровень. Есл в t- й такт работы (t 1,2,..., k, где k - максимальное число тактов) не возникло конфликтной ситуации, то выход триггера 20 будет поддерживать нулевой уровень на управляющем входе коммутатора 16 с тремя состояниями. Если в t-й такт возникла конфликтная ситуация, то за счет

10

15

20

25

5

887006

протекания тока I 1 через резистор 17 на нем выделится падение напряжения и , которое переведет выход сумматора 18 по модулю два в единичное состояние, а коммутатор 16 с тремя состояниями переключится в третье состояние. Конфликт будет устранен.

По приходу (t+1)-ro тактового импульса анализ на наличие конфликтной ситуации возобновляется. Искажения в выходной последовательности, получаемой на какой-либо линии двунаправленной шины контролируемого цифрового блока 7, обусловленные наличием в нем неисправности, вызывают изменения в последовательности на выходе соответствующего блока 4, что приводит к тому, что в последующие такты процесса контроля, когда указанная линия двунаправленной шины функционирует, как вход контролируемого блока 7, подаваемые на нее воздействия отличаются от воздействий, подаваемых на исправный цифровой блок 7, что, соответственно, проявляется в дальнейшем искажении выходной последовательности контролируемого цифрового блока 7. Указанное явление повышает контролирующую способность устройства.

Количество тактов k работы устройства фиксировано, после выдачи последнего тестового с выхода счетчика 12 сброса триггера В, работа блока 11 синхронизации прекращается. Вычисленные остатки индицируются, блоком 6 индикации и сравниваются с остатками, полученными в результате проверки исправного цифрового блока или математического моделирования.

Контролируемый цифровой блок считается исправным, если указанные остатки совпадают.

Формула изобре. те ння

воздействия подается сигнал

40

45

Устройство для контроля цифровых блоко-в, содержащее блок управления, блок синхронизации, генератор псевдослучайной последовательности,и блоков определения входов/выходов (п - число входов/выходов контролируемо- го цифрового блока), п вычислительных блоков и блок индикации, причем вход пуска устройства соединен с входом пуска блока управления, выход признака начала работы которого соединен с входами сброса генератора псевдослучайной послеповательности п блоков определения входов/выхйдов и п вычислительных блоков, выход признака начала контроля блока управления соединен с входом пуска блока синхронизации, первый выход которого соединен с входами: синхронизации генератора псевдослучайной последовательности и вычислительных блоков и тактовым входом блока управления, выходы п вычислительных блоков соединены с информационными входами п блоков определения входов/выходов, выходы которых соединены с соответствующими входами/выходами контролируемого цифрового блока, группы выходов всех вычислительных блоков соединены с входами блока индикации, причем блок управления содержит триггер пуска, одновибратор, элемент И, счетчик цикла контроля, причем инверсный вход триггера пуска соединен с входом пуска блока управления, выход триггера пуска соединен с входом одновибратора и первым входом элемента И, выход которого соединен с выходом признака начала контроля блока управления, инверсньй выход одновибратора соединен с вторым входом элемента И и с выходом признака начала работы блока управления, прямой выход одновибратора соединен с входом сброса счетчика цикла контроля, выход переполнения которого соединен с инверсным входом сброса триггера пуска счетный вход счетчика цикла контроля соединен с тактовым входом счетчика цикла контроля, каждый i-й (i 1, .. . , п) вычислительный блок содержит регистр сдвига и два сумматора,причем вход синхронизации i-ro вычислительного блока соединен с входом синхронизации регистра сдвига, группа выходов которого соединена с группой выходов i-ro вычислительного блока, k-й выход регистра сдвира (где k - число тестов) соединен с первым входом первого сумматора по модулю два, выход второго сумматора по модулю два соединен с информационным входом регистра сдвига, инверсный вход сброса которого соединен с вхо

5

0

5

дом сброса i-ro вычислительного блока, а каждый i-й блок определения входов/выходов содержит D-триггер, элемент НЕ и элемент коммутации,причем инверсный R-вход D-триггера соединен с входом сброса i-ro блока определения входов/выходов, отличающееся тем, что, с целью повышения достоверности контроля,устройство содержит п сумматоров по модулю два, а в каждьй i-й вычислительный блок введен ограничительный ре- зисфор и сумматор по модулю два,причем второй выход блока синхронизации соединен с входом синхронизации п блоков определения входов/выходов, выход генератора псевдослучайной последовательности соединен с первым входом первого сумматора по модулю два, выходы п сумматоров соединены с информационными входами п вычислительных блоков, первые входы сумматоров по модулю два с второго по п-й включительно соединены с выходами вычислительных блоков с первого по (п-1)-й соответственно, вторые входы п сумматоров соединены с выходами п блоков определения входов/выходов, причем в i-M вычислительном блоке i-й выход регистра Сдвига соединен с вторым входом первого сумматора по модулю два, выход которого соединен с первым входом второго сумматора по модулю два, вто- 5 рой вход которого соединен с информационным входом i-ro вычислительного блока, а в каждом i-м блоке определения входОБ/выходов выход D-триггера соединен с управляющим входом элемента коммутации, информациоиньй вход которого соединен с информационным входом i-ro блока определения входов/выходов, выход элемента коммутации соединен с первым входом сумматора по модулю два и через ограничительный резистор с вторым входом сумматора по модулю два и с выходом i-ro блока определения входов/выходов, выход сумматора по модулю два соединен через элемент НЕ . с инверсным S-входом D-триггера, D - вход которого подключен к шине нулевого потенциала устр- ройства.

0

5

0

Фиг. 2

Редактор В.Петраш

Заказ 7810/48 .Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

е-- .ьв-.-в Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектнаяj 4

Составитель А.Сиротская

Техред Л.Олейник Корректор Л.Пилипекко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1987 |

|

SU1506450A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1302285A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| Устройство для локализации неисправностей в цифровых схемах | 1981 |

|

SU1103201A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

Изобретение относится к цифровой технике и может использоваться для контроля блоков ЦВМ, содержащих микропроцессорные БИС. Цель изобретения- повышение достоверности контроля. Устройство содержит блок управления, .блок синхронизации, генератор псевдо- : случайной последовательности, вычислительные блоки, совмещающие функцию генераторов теста сигнатурного анализа, блоки определения входов/выходов, сумматоры по модулю два, блок индикации. Достоверность повышается за счет того, что блоки определения входов/выходов определяют ситуацию, когда значение входа/выхода контролируемого блока в промежутках мелзду тактами контроля изменяет свое состояние. i 4 ил. (Л to 00 оо -Nj

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля логических блоков | 1982 |

|

SU1037257A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| БЛОКОВ | |||

Авторы

Даты

1987-02-07—Публикация

1985-07-05—Подача