Изобретение относится к вычислительной технике и может быть использовано для преобразования кода Фибоначчи-1 в код золотой - 1 пропорции.

Целью изобретения является повышение быстродействия.

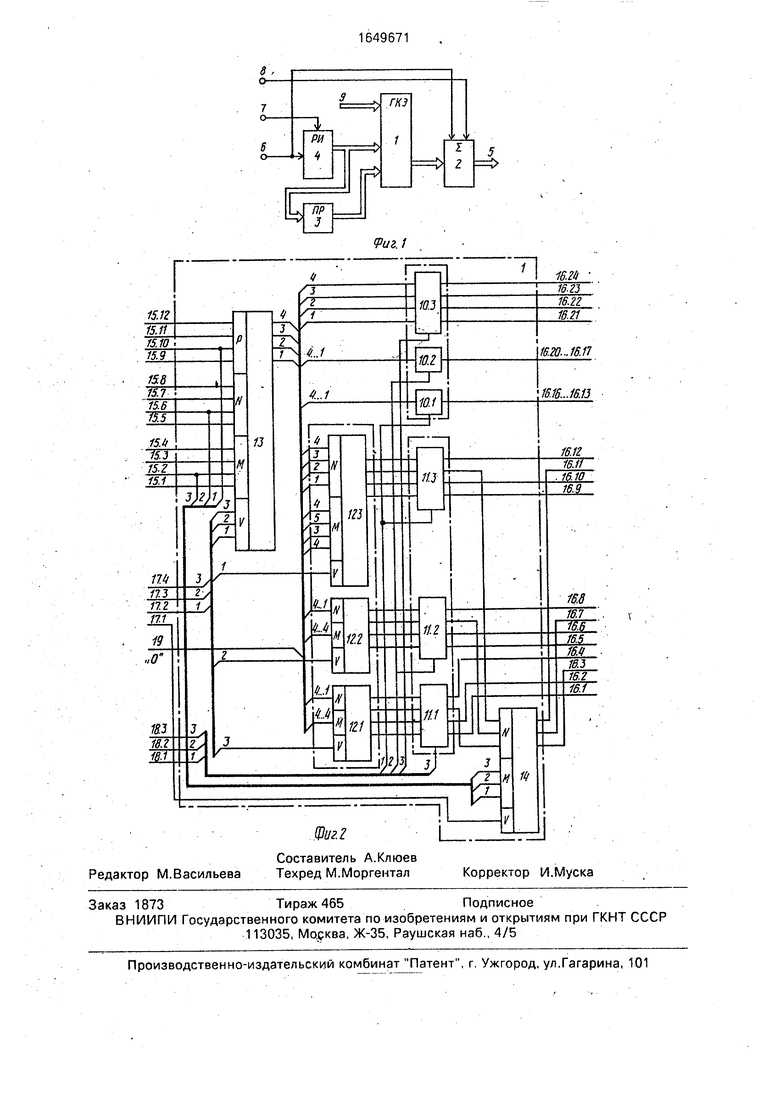

-1 На фиг. 1 представлена функциональная схема преобразователя кода Фибоначчи 1 в код золотой - 1 пропорции; на фиг. 2 -то же, генератор кодовых эквивалентов (для п 12).

Преобразователь содержит генератор 1 кодовых эквивалентов, накапливающий сумматор 2 кодов золотой - 1 пропорции, преобразователь 3 унитарного кода в единичный код, распределитель 4 импульсов, выход 5 преобразователя, вход 6 начальной установки преобразователя, первый и второй тактовые входы 7 и 8 преобразователя, информационный вход 9 преобразователя..

Генератор 1 кодовых эквивалентов содержит первую группу узлов 10.1 - 10,3 элементов И, вторую группу узлов 11 1 - 11,3 элементов И, группу мультиплексоров 12.1 - 12.3, коммутатор 13, мультиплексор 14, входы 15.1 - 15.12 разрядов информационного входа генератора 1 кодовых эквивалентов, выходы 16.1 - 16.24 разрядов выхода генератора 1 кодовых эквивалентов, входы 17.1 - 17.4 разрядов первого управляющего входа генератора 1 кодовых эквивалентов, входы 18.1 - 18.3 разрядов второго управляющего входа генератора 1 кодовых эквивалентов, вход 19 нулевого потенциала преобразователя.

Разрядность накапливающего сумматора 2 равна 2П. Разрядность преобразователя 3 равна п/4. Разрядность распределителя 4 равна п/4 + 1.

О

4

Ч) О

1

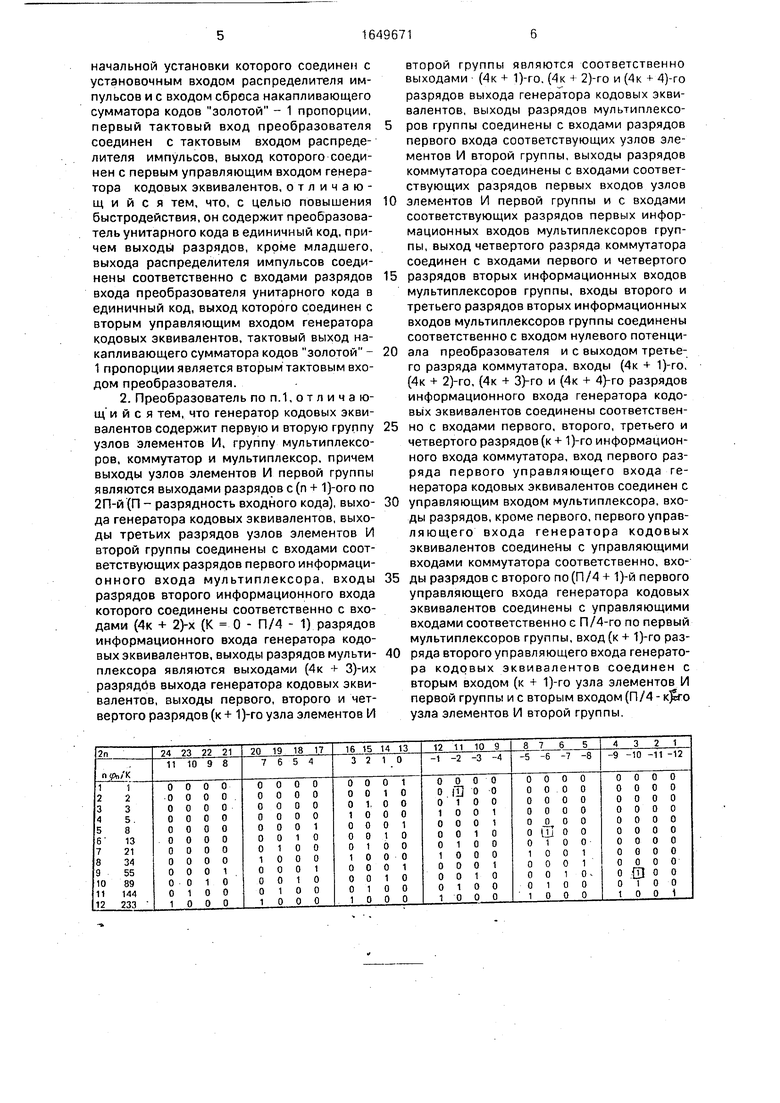

Применен табличный принцип преобразования кода Фибоначчи-1 в код золотой - 1 пропорции. В таблице приведены кодовые эквиваленты для двенадцати чисел (1) Фибоначчи в коде золотой - 1 пропорции. Анализ данных таблицы показывает, что за исключением выделенных единиц в кодовых эквивалентах чисел Фибоначчи (2 + 4п) кодовые эквиваленты в группах из четырех разрядов, начиная с младших, являются непересекающимися кодами, поэтому является возможным получить суммарный кодовый эквивалент от разрядов группы путем их одновременного формирования. Для выделенных единиц в кодовых эквивалентах чисел Фибоначчи (2 + 4п) необходим отдельный такт их преобразования. При разбиении кодовых эквивалентов на группы по четыре разряда возможны три варианта преобразования в зависимости от номера преобразуемой группы разрядов, причем для старших двенадцати разрядов два варианта - блокирующее (нулевое состояние) и повторители входного канала. Для младших двенадцати разрядов существует третий вариант преобразования описываемой функцией: yi Х4; У2 0; уз хз; У4 Х4.

Пример. На входе 9 задается преобразуемый код, например 0101.0110.1111 в произвольной форме. Подачей однократного импульса на установочный вход 6 осуществляется обнуление сумматора 2 и установка распределителя 4 в состояние 10000. На выходе преобразователя 3 устанавливается код 000, блокирующий все узлы 10 и 11 элементов и групп. Единичное состояние младшего разряда распределителя 4 коммутирует на вход сумматора 2 второй канал мультиплексора 14, что сформирует на входе сумматора 2 код, в котором состояние разрядов к -2, к -6, к -10будет зависеть от состояния соответствующих разрядов n 2, n 6,n 10 исходного кода при нулевом состоянии остальных разрядов, т.е. код 0010.0000.0010.0000.0000.0000, который просуммируется по синхроимпульсу по входу 8 с предыдущим состоянием сумматора 2.

На следующем такте работы синхроимпульс по входу 7 установит распределитель 4 в состояние 0100, а преобразователь 3 в состояние 100. При этом в коммутаторе 13 третий канал, т.е. содержимое четырех младших разрядов исходного кода 0101 коммутируются на его выход. Мультиплексор 14 переключается на первый канал и остается до конца преобразования в этом состоянии. Узлы 10.3, 10.2, 11.2, 11.1 элементов И будут по-прежнему закрыты, а узлы 10.1 и 11.3 элементов И откроются. В мультиплексоре 12.1 на выход подключится второй канал, т.е. на входе сумматора 2 сформируется код 0000.0000.1001.0000.0000, который по

приходу синхроимпульса по входу 8 будет накапливаться в сумматоре 2.

На следующем такте работы синхроимпульс по входу 7 устанавливает распредели- тель 4 в состояние. 0010, а

0 преобразователь 3 в состояние 110. При этом на выходе коммутатора 13 появится комбинация второго канала 0110. В мультиплексоре 12,3 на выходе будет комбинация первого канала, в мультиплексоре 12.2

5 на выходе будет комбинация второго канала. Узлы 10.3 и 11 1 элементов И остаются закрытыми, а узлы 10.2, 10.1, 11.2, 11.3, элементов будут открытыми. На входе сумматора 2 сформируется код:

0 0000.0100,0110.0110.0110.0000, который по приходу синхроимпульса 8 просуммируется с ранее сформированными.

По синхроимпульсу 7, на выходе распределителя 4 сформируется комбинация

5 0001, а на выходе преобразователя 3 111. При этом на выходе коммутатора 13 сформируется комбинация первого канала 1111 т.е. старших разрядов входного кода. Мультиплексоры 12.3 и 12.2 подключены на

0 первый канал мультиплексора 12.1 - на второй канал. Все узлы .10 и 11 элементов И открыты. На входе сумматора 2 сформируется код 1011.1111.1111.1111.1111.1111. По синхроимпульсу 8 происходит суммирова5 ние. На этом преобразование заканчивается, так как следующий синхроимпульс по входу 7 обнуляет распределитель 4 и преобразователь 3.

Таким образом, преобразование проис0 ходит за (П/4 + 1) тактов суммирования, однако возможно применение известных методов ускорения преобразования, а именно пропуска текста суммирования, если состояние преобразуемой группы разря5 дов нулевое, для чего достаточно анализировать состояние выхода коммутатора 13.

Формула изобретения

1. Преобразователь кода Фибоначчи-1 в

0 код золотой - 1 пропорции, содержащий генератор кодовых эквивалентов, накапливающий сумматор кодов золотой - 1 пропорции и распределитель импульсов, причем информационный вход преобразо5 вателя соединен с информационным входом генератора кодовых эквивалентов, выход которого соединен с входом слагаемого накапливающего сумматора кодов золотой - 1 пропорции, выход которого является выходом преобразователя, вход

начальной установки которого соединен с установочным входом распределителя импульсов и с входом сброса накапливающего сумматора кодов золотой - 1 пропорции, первый тактовый вход преобразователя соединен с тактовым входом распределителя импульсов, выход которого соединен с первым управляющим входом генератора кодовых эквивалентов, отличающийся тем, что, с целью повышения быстродействия, он содержит преобразователь унитарного кода в единичный код, причем выходы разрядов, кроме младшего, выхода распределителя импульсов соединены соответственно с входами разрядов входа преобразователя унитарного кода в единичный код, выход которого соединен с вторым управляющим входом генератора кодовых эквивалентов, тактовый выход накапливающего сумматора кодов золотой - 1 пропорции является вторым тактовым входом преобразователя.

2. Преобразователь по п. 1, о т л и ч а ю- щ и и с я тем, что генератор кодовых эквивалентов содержит первую и вторую группу узлов элементов И, группу мультиплексоров, коммутатор и мультиплексор, причем выходы узлов элементов И первой группы являются выходами разрядов с (п + 1)-ого по 2П-й (П - разрядность входного кода), выхода генератора кодовых эквивалентов, выходы третьих разрядов узлов элементов И второй группы соединены с входами соответствующих разрядов первого информаци- онного входа мультиплексора, входы разрядов второго информационного входа которого соединены соответственно с входами (4к + 2)-х (К 0 - П/4 - 1) разрядов информационного входа генератора кодовых эквивалентов, выходы разрядов мультиплексора являются выходами (4к + 3)-их разрядбв выхода генератора кодовых эквивалентов, выходы первого, второго и четвертого разрядов (к + 1)-го узла элементов И

10

второй группы являются соответственно выходами (4к + 1)-го. (4к -t 2)-ro и (4к + 4)-го разрядов выхода генератора кодовых эквивалентов, выходы разрядов мультиплексоров группы соединены с входами разрядов первого входа соответствующих узлов элементов И второй группы, выходы разрядов коммутатора соединены с входами соответствующих разрядов первых входов узлов элементов И первой группы и с входами соответствующих разрядов первых информационных входов мультиплексоров группы, выход четвертого разряда коммутатора соединен с входами первого и четвертого 5 разрядов вторых информационных входов мультиплексоров группы, входы второго и третьего разрядов вторых информационных входов мультиплексоров группы соединены соответственно с входом нулевого потенциала преобразователя и с выходом третьего разряда коммутатора, входы (4к + 1)-Го, (4к + 2)-го, (4к + 3}-го и (4к + 4}-го разрядов информационного входа генератора кодовых эквивалентов соединены соответственно с входами первого, второго, третьего и четвертого разрядов (к + 1)-го информационного входа коммутатора, вход первого разряда первого управляющего входа генератора кодовых эквивалентов соединен с управляющим входом мультиплексора, входы разрядов, кроме первого, первого управляющего входа генератора кодовых эквивалентов соединены с управляющими входами коммутатора соответственно, вхо- 5 ды разрядов с второго по (П/4 + 1)-й первого управляющего входа генератора кодовых эквивалентов соединены с управляющими входами соответственно с П/4-ro по первый мультиплексоров группы, вход (к + 1)-го разряда второго управляющего входа генератора кодовых эквивалентов соединен с вторым входом (к + 1)-го узла элементов И первой группы и с вторым входом (П/4 - узла элементов И второй группы.

0

5

0

0

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

| Преобразователь кодов | 1988 |

|

SU1658390A1 |

| Устройство аналого-цифрового преобразования | 1985 |

|

SU1288914A1 |

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Устройство контроля цифро-аналоговых преобразователей | 1981 |

|

SU1008902A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

| Последовательный сумматор | 1988 |

|

SU1571573A1 |

| Устройство для передачи радиотелеметрических сигналов | 1990 |

|

SU1714368A1 |

Изобретение относится к вычислительной технике и предназначено для преобразования кода Фибоначчи-1 в код золотой - 1 пропорции. Целью изобретения является повышение быстродействия Преобразователь содержит генератор 1 кодовых эквивалентов, накапливающий сумматор 2 кодов золотой -1 пропорции, преобразователь 3 унитарного кода в единичный код и распределитель 4 импульсов с соответствующими связями Генератор 1 кодовых эквивалентов формирует суммарный кодовый эквивалент для групп из четырех разрядов преобразуемого кода, что обеспечивает высокое быстродействие-преобразователя. 1 з,п.ф-лы, 2 ил, 1 табл.

| Преобразователь р-кода фибоначчи в двоичный код | 1976 |

|

SU662932A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-15—Публикация

1988-09-26—Подача