импульсов и на их основе команд управления. Синхроимпульсы, поступающие с друг ого выхода блока синхронизации на входы блока 2 коммутации, блока 24 оперативной памяти и выходного блока 23, предназначены для формирования импульсов записи в элементы памяти. Изобретение позволяет осуществлять запись информации в элементы памяти по сигналу записи, снятие которого производится до снятия информационного сиг нала, что гарантирует правильность записи информации в элементы памяти. 6 ил.

1

Изобретение относится к системам автоматики и может быть использовано в автоматизированных системах управления машинами, механизмами, поточными линиями и т.д.

Цель изобретения - повышение надежности работы устройства.

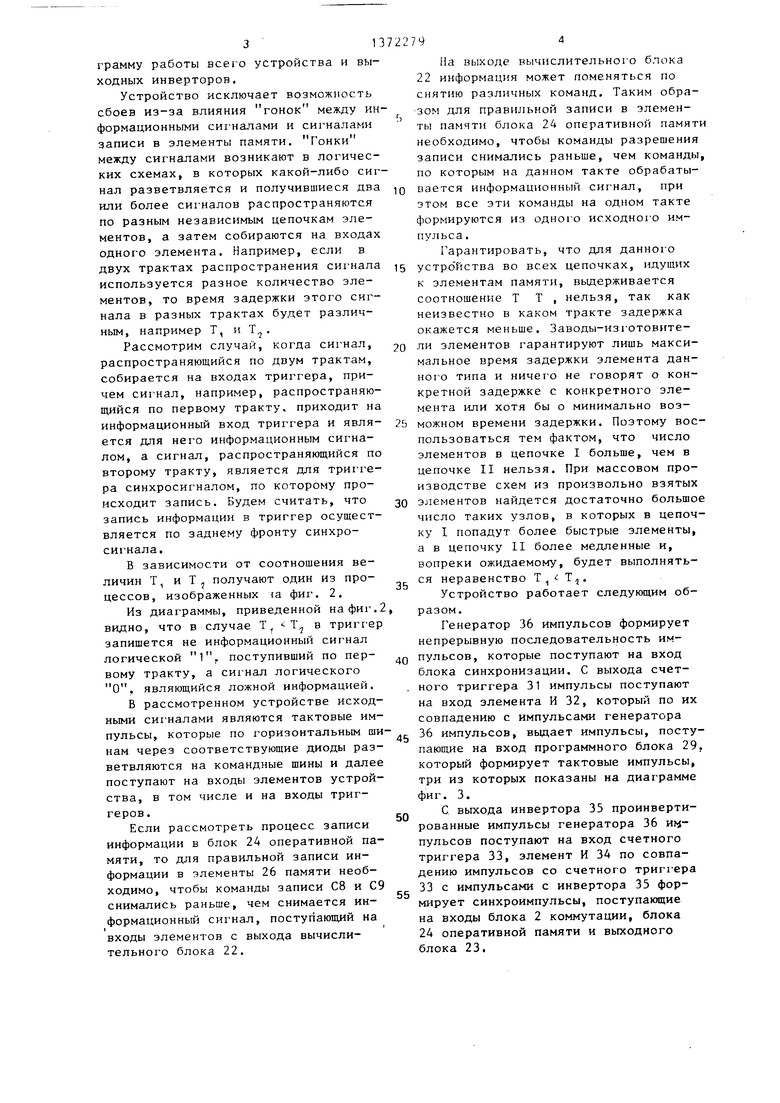

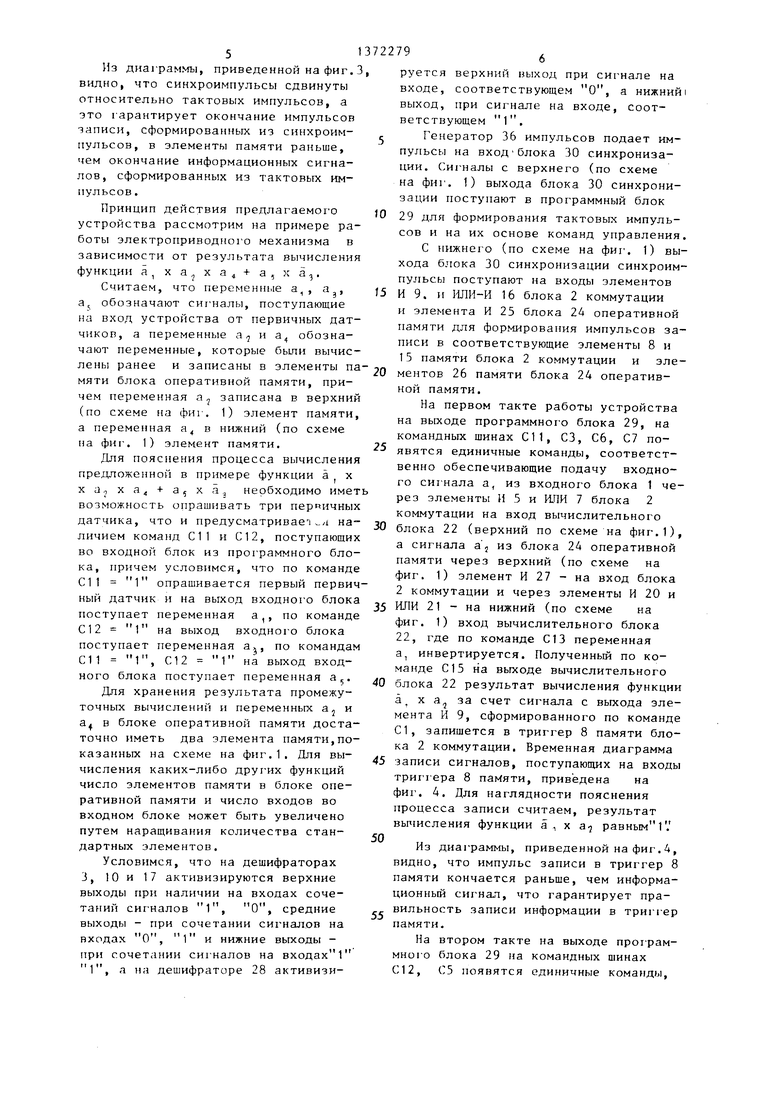

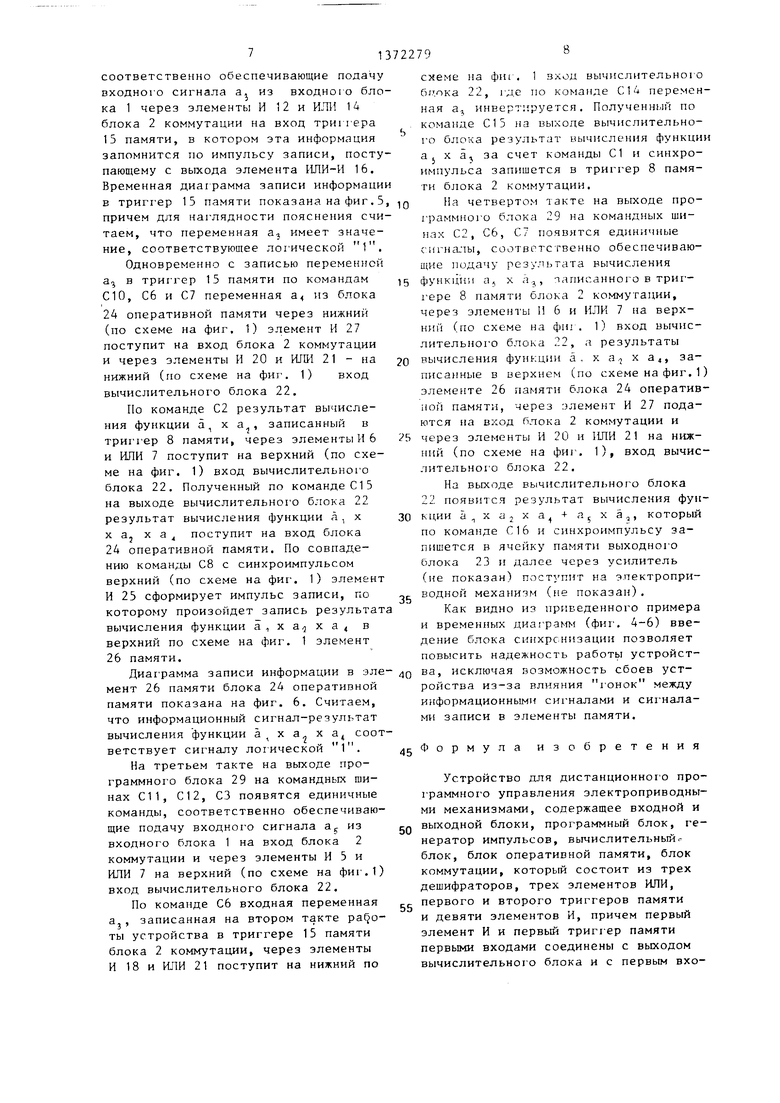

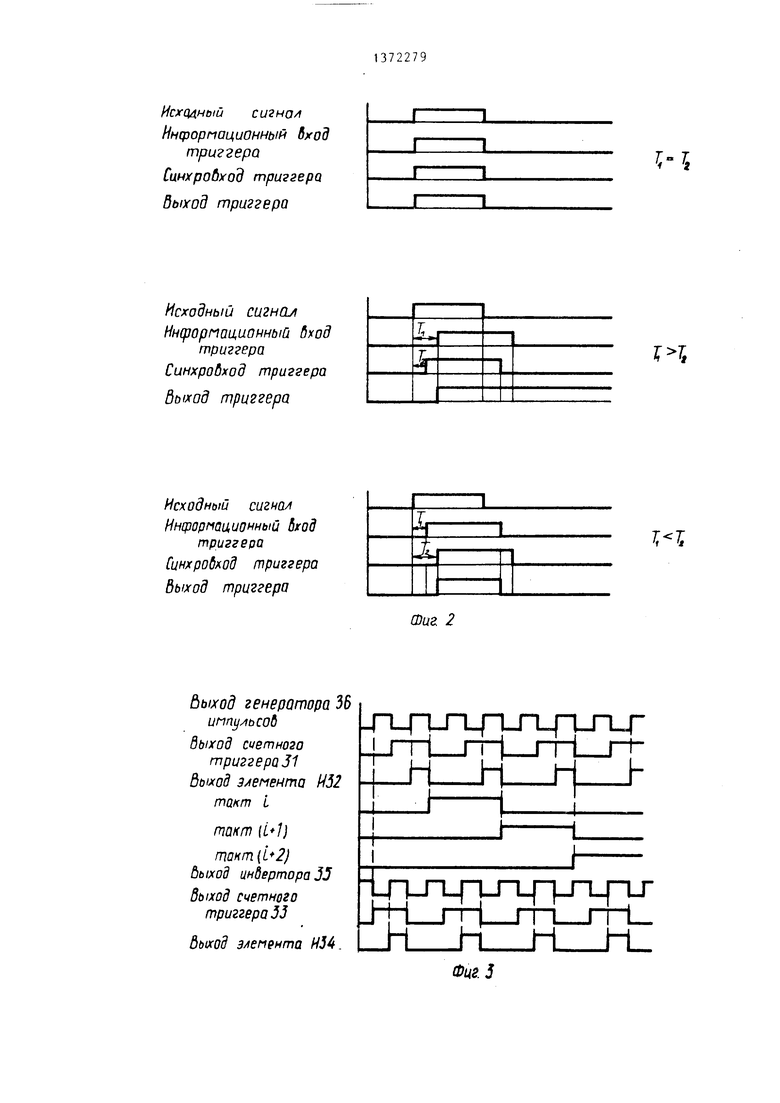

На фиг. 1 представлена схема устройства, на фиг-. 2 - временные диаграммы, поясняющие запись информации в трИ1гер, на фиг. 3 - временная диаграмма, поясняющая работу блока синхронизации, на фиг . А - временная

диаграмма заттсн сигналов, по- упаю- щих-на входы триггера памяти, нафиг .2 фиг. 5 и 6 - временные диаграммы записи информации в элементы памяти.

Устройство содержит входной блок 1, блок 2 коммутации, содержащий дешифратор 3, элементы И 4-6 и ИЛИ 7, первый триггер 8 памяти, элемент И 9, дешифратор 10, элементы И 11-13 и ИЛИ 14, второй триггер 15 памяти, элемент ИЛИ-И 16, дешифратор 17, элементы И 18-20 и ИЛИ 21, вычислительный 22 и выходной 23 блоки, блок 24 оперативной памяти, содержащий вторые элементы И 25, элементы 26 памяти, первые элементы И 27 и дещифратор 28, а также содержит программный блок 29, блок 30 синхронизации, состоящий из первого счетного тригг ера 31, первого элемента И 32, второго счетного триггера 33, второго элемента И 34, инвертора 35, и генератор 36 импульсов .

Показаны командные шины С1-С16, по которым поступают соответствующие команды из прот раммного блока.

Входной блок 1 известной структуры состоит из стандартных элементов (не гюкатлиы), на вход которых поступают сш палы от первичных датчиков, а с

выхода снимаются унифицированные СИ1- налы, соответствующие логическим

сигналам

О и 1,

элементов считывания, в качестве которых можно применять двухвходные элементы И, элемента ИЛИ, объединяющего по выходу все элементы И, и дешифратора управляющего элементами И по командам из программного блока.

Выходной блок 23 состоит из элементов И, стандартных ячеек памяти и соответствующих усилителей (не показаны) , передающих логические сигналы из ячеек памяти на электроприводные

механизмы (не показаны), по командам из программного блока.

Вычислительный блок 22 известной структуры состоит из стандартных элементов (не показаны), позволяющих

производить операции сложения (элемент ИЛИ), умножения (элемент И). инверсию (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ) переменных булевых функций по командам из прог раммного блока, дешифратора,

элементов считьшания, произведения или суммы и элемента Ш1И (не показаны) .

На одном такте вычислительный блок 22 может вычислить одну из логических

функций: а

а, а.

X а

1

X а, + -а,.

а,

X 32,

+ а,.

X а -;,

+ а,.

+ а, где а, и а - переменные

булевых функций, поступающие на вход вычислительного блока, а - инвер- 35 сия а.

Программный блок 29 известной структуры состоит из стандартных элементов: счетчика, дешифратора, 40 распределяющего импульсы во времени и по направлению, диодной матрицы с горизонтальными, командными шинами и диодами, определяющими программу работы всего устройства ходных инверторов.

Устройство исключает возможность сбоев из-за влияния гонок между информационными сигналами и сигналами записи в элементы памяти. Гонки между сигналами возникают в логических схемах, в которых какой-либо сигнал разветвляется и получившиеся два или более сигналов распространяются по разным независимым цепочкам элементов, а затем собираются на входах одного элемента. Например, если в двух трактах распространения сигнала используется разное количество элементов, то время задержки этого сигнала в разных трактах будет различным, например Т, и Т.

Рассмотрим случай, когда сигнал, распространяющийся по двум трактам, собирается на входах триггера, причем сигнал, например, распространяющийся по первому тракту, приходит на информационный вход триггера и является для него информационным сигналом, а сигнал, распространяющийся по второму тракту, является для триггера синхросигналом, по которому происходит запись. Будем считать, что запись информации в триггер осуществляется по заднему фронту синхросигнала.

В зависимости от соотношения величин Т, и Т, получают один из процессов, изображенных la фиг. 2.

Из диаграммы, приведенной на фиг.2 видно, что в случае Т Т. в трип ер запишется не информационный сигнал логической 1. поступивший по первому тракту, а сигнал логического О, являющийся ложной информацией.

В рассмотренном устройстве исходными сигналами являются тактовые импульсы, которые по горизонтальным шинам через соответствующие диоды разветвляются на командные шины и далее поступают на входы элементов устройства, в том числе и на входы триггеров .

Если рассмотреть процесс записи информации в блок 24 оперативной памяти, то для правильной записи информации в элементы 26 памяти необходимо, чтобы команды записи С8 и С9 снимались раньше, чем снимается информационный сигнал, поступающий на II

входы элементов с выхода вычислительного блока 22.

вы-

,

10

15

20

2S

3722794

1а выходе вычислительного блока 22 информация может поменяться по снятию различных команд. Таким образом для правильной записи в элементы памяти блока 24 оперативной памяти необходимо, чтобы команды разрешения записи снимались раньше, чем команды, по которым на данном такте обрабатывается информационный сигнал, при этом все эти команды на одном такте формируются из одного исходного импульса .

Гарантировать, что для данного устро йства во всех цепочках, идущих к элементам памяти, выдерживается соотношение Т Т , нельзя, так как неизвестно в каком тракте задержка окажется меньше. Заводы-изготов1гте- ли элементов гарантируют лишь максимальное время задержки элемента данного типа и ничет о не говорят о конкретной задержке с конкретного элемента или хотя бы о минимально возможном времени задержки. Поэтому воспользоваться тем фактом, что число элементов в цепочке I больше, чем в цепочке II нельзя. При массовом производстве схем из произвольно взятых элементов найдется достаточно большое число таких узлов, в которых в цепочку I попадут более быстрые элементы, а в цепочку II более медленные и, вопреки ожидаемому, будет выполняться неравенство ,.

Устройство работает следующим образом.

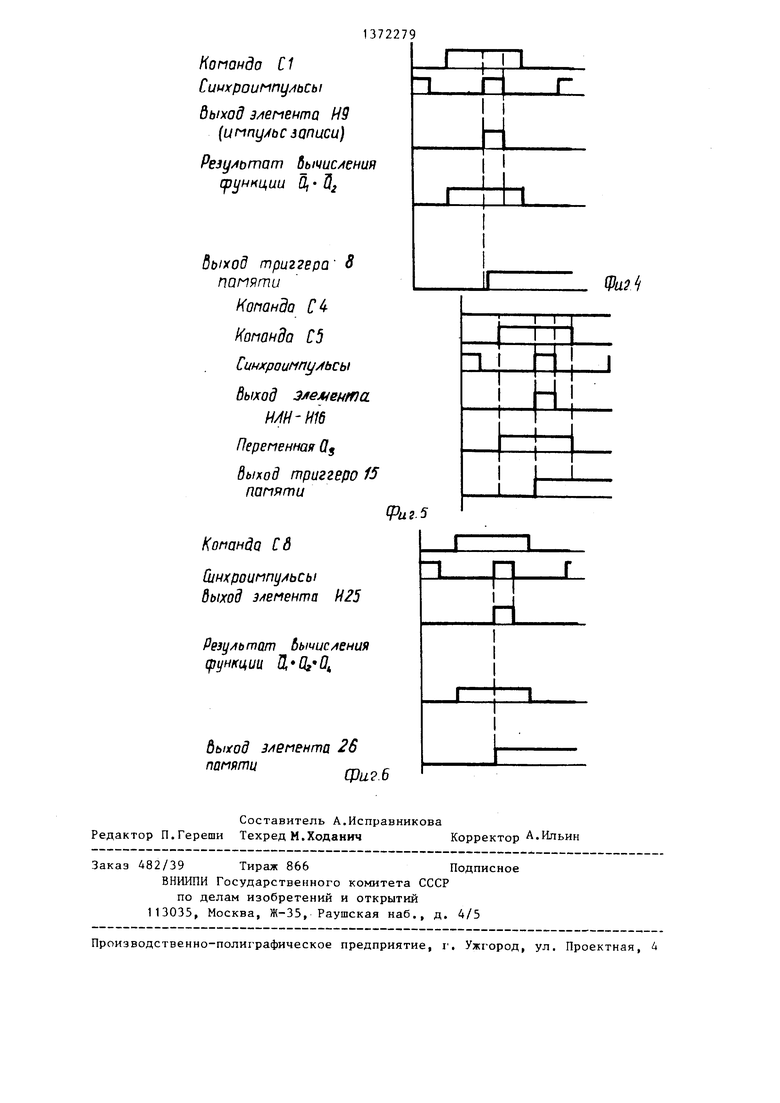

Генератор 36 импульсов формирует непрерывную последовательность импульсов, которые поступают на вход блока синхронизации. С выхода счетного триггера 31 импульсы поступают на вход элемента И 32, который по их совпадению с импульсами генератора 36 импульсов, вьщает импульсы, поступающие на вход программного блока 29. который формирует тактовые импульсы, три из которых показаны на диаграмме фиг. 3.

С выхода инвертора 35 проинверти- рованные импульсы генератора 36 пульсов поступают на вход счетного триггера 33, элемент И 34 по совпадению импульсов со счетного трип ера 33 с импульсами с инвертора 35 формирует синхроимпульсы, поступающие на входы блока 2 коммутации, блока 24 оперативной памяти и выходного блока 23.

30

35

40

46

50

55

5

Из диа1 раммы, приведенной на фиг видно, что синхроимпульсы сдвинуты относительно тактовых импульсов, а это гарантирует окончание импульсо записи, сформированных из синхроимпульсов, в элементы памяти раньше, чем окончание информационных сигна

лов, сформированных из тактовых импульсов.

Принцип действия предлагаемого устройства рассмотрим на примере работы электроприводного механизма в зависимости от результата вычисления функции а X а х а,

3

Считаем, что переменные а

aj обозначают сиг налы, поступающие на вход устройства от первичных датчиков, а переменные а и а обозначают переменные, которые были вычислены ранее и записаны в элементы па- мяти блока оперативной памяти, причем переменная а, (по схеме на фиг.

записана в верхний 1) элемент памяти.

а переменная а в нижний (по схеме на фиг. 1) элемент памяти.

Для пояснения процесса вычисления предложенной в примере функции а х xajXa +ajXa, необходимо иметь возможность опрашивать три первичных датчика, что и предусматривает п наличием команд С11 и С12, поступающих во входной блок из программного блока, причем условимся, что по команде С11 1 опрашивается первый первичный датчик и на выход входного блока

поступает переменная

1

по команде

С12 1 на выход входного блока поступает переменная а, по команда СП 1, С12 1 на выход входного блока поступает переменная а

Для хранения результата промежуточных вычислений и переменных а и а в блоке оперативной памяти достаточно иметь два элемента памяти,показанных на схеме на фиг.1. Для вычисления каких-либо друг их функций число элементов памяти в блоке оперативной памяти и число входов во входном блоке может быть увеличено путем наращивания количества стандартных элементов.

Условимся, что на дешифраторах 3, 10 и 17 активизируются верхние выходы прп наличии на входах сочетаний сигналов 1, О, средние выходы - при сочетании сигналов на входах О, 1 и нижние выходы - при сочетании сигналов на входах 1 1, а на дешифраторе 28 активизи

5

Q

5

5

0 б

руется верхний выход при сигнале на входе, соответствующем О, а нижний выход, при сигнале на входе, соответствующем 1.

Генератор 36 импульсов подает импульсы на вход блока 30 синхронизации. (;:и1-налы с верхнего (по схеме на фиг. 1) выхода блока 30 синхронизации поступают в программный блок 29 для формирования тактовых импульсов и на их основе команд управления.

С нижнего (по схеме на фиг . 1) выхода блока 30 синхронизации синхроимпульсы поступают на входы элементов И 9. и 1-ШИ-И 16 блока 2 коммутации и элемента И 25 блока 2Д оперативной памяти для формировапия импульсов записи в соответствующие элементы 8 и 15 памяти блока 2 коммутации и элементов 26 памяти блока 24 оперативной памяти.

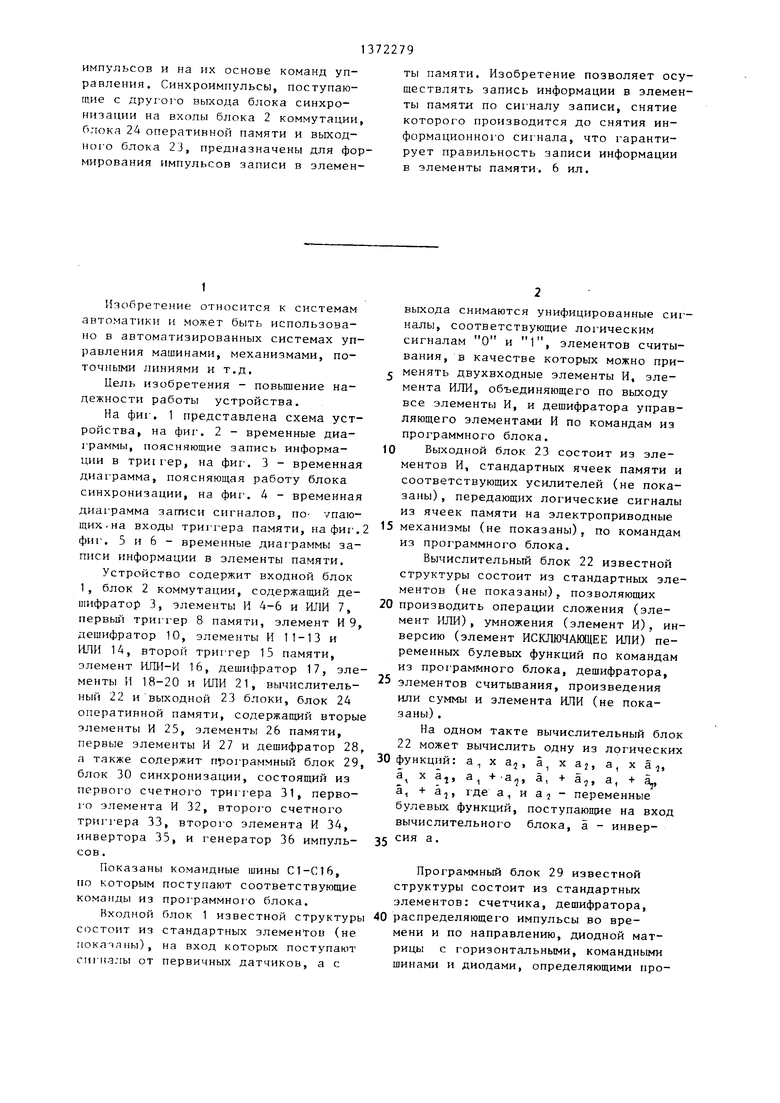

На первом такте работы устройства на выходе программног-о блока 29, на командных щинах 011, СЗ, С6, С7 появятся единичные команды, соответственно обеспечивающие подачу входного сигнала а, из входного блока 1 через элементы И 5 и ИЛИ 7 блока 2 коммутации на вход вычислительного блока 22 (верхний по схеме на фиг.1), а сигнала а , из блока 24 оперативной памяти через верхний (по схеме на фиг. 1) элемент И 27 - на вход блока 2 коммутации и через элементы И 20 и 5 ИЛИ 21 - на нижний (по схеме на фиг. 1) вход вычислительного блока 22, где по команде С13 переменная а, инвертируется. Полученный по команде С15 на выходе вычислительного блока 22 результат вычисления функции а X а за счет сигнала с выхода элемента И 9, сформированного по команде С1, запишется в триггер 8 памяти блока 2 коммутации. Временная диаграмма записи сигналов, поступаюпщх на входы триггера 8 памяти, приведена на фиг. 4. Для наглядности пояснения процесса записи считаем, результат вьпшсления функции а , х а-; равным .

Из диаграммы, приведенной на фиг.4, видно, что импульс записи в триггер 8 памяти кончается раньще, чем информационный сигнал, что гарантирует правильность записи информации в трип-ер памяти.

На втором такте на выходе программного блока 29 на командных шинах С12, С5 появятся единичные команды.

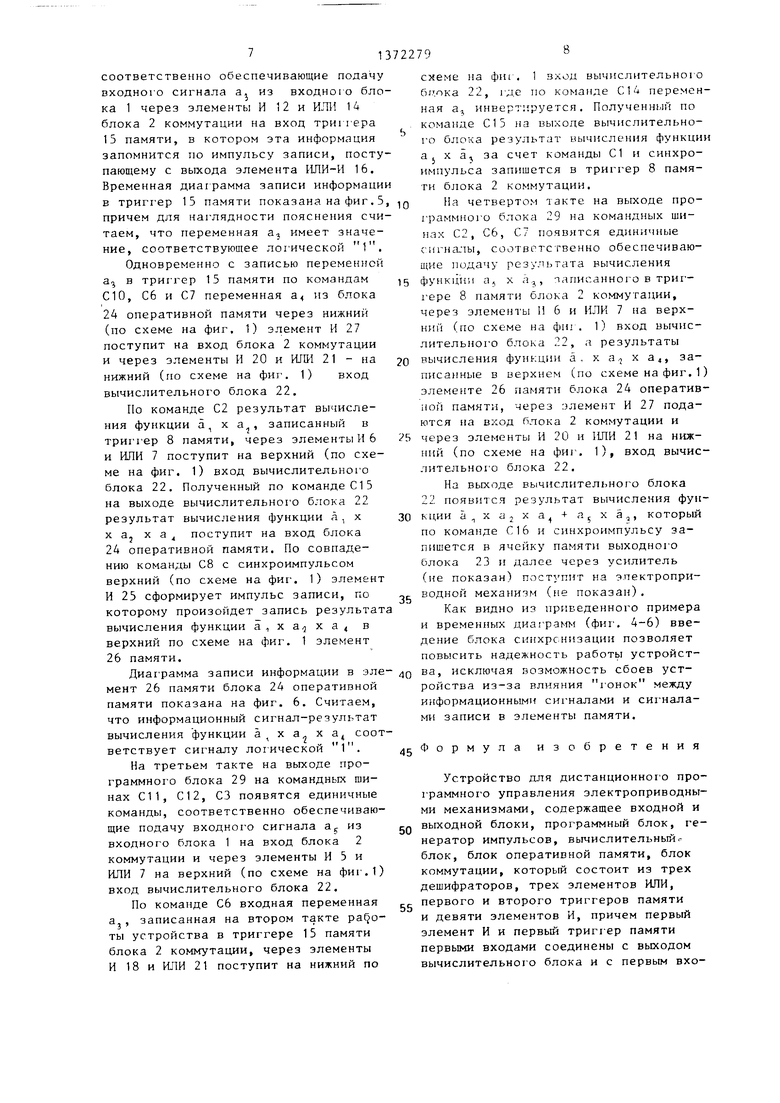

0

0

5

соответственно обеспечивающие подачу входного сигнала а, из входного блока 1 через элементы И 12 и ИЛИ 14 блока 2 коммутации на вход триггера 15 памяти, в котором эта информация запомнится по импульсу записи, поступающему с выхода элемента РШИ-И 16. Временная диаграмма записи информаци в триггер 15 памяти показана на фиг.5 причем для Hai-лядности пояснения считаем, что переменная а, имеет значение, соответствующее логической 1.

Одновременно с записью переменной а в тригтер 15 памяти по командам С10, С6 и С7 переменная а4 из блока 24 оперативной памяти через нижний (по схеме на фиг. 1) элемент И 27 поступит на вход блока 2 коммутации и через элементы И 20 и ИЛИ 21 - на нижний (по схеме на фиг. 1) вход вычислительного блока 22.

По команде С2 результат вычисления функции а X а, записанный в триггер 8 памяти, через элементы И 6 и ИЛИ 7 поступит на верхний (по схеме на фиг. 1) вход вычислительного блока 22. Полученный по команде С15 на выходе вычислительного блока 22 результат вычисления функции а, х X а, X а поступит на вход блока 24 оперативной памяти. По совпадению команды С8 с синхроимпульсом верхний (по схеме на фиг. 1) элемент И 25 сформирует импульс записи, по которому произойдет запись результат вычисления функции в верхний по схеме на фиг. 1 элемент 26 памяти.

Диаг рамма записи информации в элемент 26 памяти блока 24 оперативной памяти показана на фиг. 6. Считаем, что информационный сигнал-результат вычисления функции а х а. х а соответствует сигналу логической 1.

На третьем такте на выходе программного блока 29 на командных шинах С11, С12, СЗ появятся единичные команды, соответственно обеспечивающие подачу входного сигнала а из входного блока 1 на вход блока 2 коммутации и через элементы И 5 и ИЛИ 7 на верхний (по схеме на фиг.1) вход вычислительного блока 22.

По команде С6 входная переменная а., записанная на втором такте paQo- ты устройства в триггере 15 памяти блока 2 коммутации, через элементы И 18 и ИЛИ 21 поступит на нижний по

0

5

Ъ

схеме на фиг. 1 вход вычислительного бттока 22, где по команде С14 переменная а, инверт1;руется. Полученный по команде С15 на выходе вычислительного блока результат нычисления функции а X а, за счет команды С1 и синхроимпульса запишется в триггер В памяти блока 2 коммутации.

Яа четвертом такте на выходе программного блока 29 на командных шинах С2, С6, С7 появятся единичные с игналы, соответственно обеспечивающие подачу результата вычисления функции а, X a.j, написанного в триггере 8 памяти блока 2 коммутации, через элеме}П ы И 6 и ИЛИ 7 на верхний (по схеме на фиг. 1) вход вычислительного блока 22, а результаты вычисления функции а, х а х а, записанные в верхнем (по схеме на фиг.1) элементе 26 памяти блока 24 оперативной памяти, через элемент И 27 подаются на вход блока 2 коммутации и через элементы И 20 и ИЛИ 21 на нижний (по схеме на фиг. 1), вход вычислительного блока 22.

На выходе вычислительног о блока 22 появится результат вычисления фун

кции aj X а + а х а,, который по команде С16 и синхроимпульсу за- пиЕ1ется в ячейку памяти выходно1 о блока 23 и далее через усилитель (не показан) поступит на электроприводной механизм (не показан).

Как видно из приведенного примера и временных диа1 ра.т (фиг. 4-6) введение блока синхронизации позволяет повысить надежность работы устройства, исключая возможность сбоев устройства из-за влияния гонок между информационными сигналами и сигналами записи в элементы памяти.

Формула изобретения

Устройство для дистанционног о про- граммног о управления электроприводными механизмами, содержащее входной и выходной блоки, программный блок, генератор импульсов, вычислительный. блок, блок оперативной памяти, блок коммутации, который состоит из трех дешифраторов, трех элементов ИЛИ, первого и второго триггеров памяти и девяти элементов И, причем первый элемент И и первый трип-ер памяти ервыми входами соединены с выходом вычислительного блока и с первым входом выходного блока, второй, третий и четвертый элементы И первыми входами подключены к выходу входного блока, пятый, шестой и седьмой элементы И первыми входами соединены с выходом блока оперативной памяти, восьмой элемент И входами подключен к выходу первого триггера памяти и к первому выходу первого дешифратора, второй и пятый элементы И вторыми входами соединены соответственно с вторым и третьим выходами первого дешифратора, первый элемент ИЛИ входами подключен к выходам восьмого, второго и пятого элементов И, а выходом - к первому входу вычислительного блока, первый, третий и шестой элементы И вторыми входами соединены соответственно с первым, вторым и третьим вы- ходами второго дешифратора, второй элемент ИЛИ входами подключен к выходам первого, третьего и шестого элементов И, а выходом - к первому входу второго тригтера памяти, выход которого соединен с первьм входом девятого элемента И, второй вход которого, а также вторые входы давятох о, четвертого и седьмог о элементов И подключены соответственно к , второму и третьему выходам третьего дешифратора, входы третьег о элемента И соединены с выходами девятого, четвертого и седьмого элементов И, а выход третьего элемента ИЛИ под- ключен к второму входу вычислительного блока, дешифраторы обоими входами соединены с соответствующими командными шинами программного блока, причем блок оперативной памяти состоит из дешифратора и двух параллельно подключенных каналов, каждый из которых содержит элемент памяти и первый элемент И, первые входы элементов памяти обоих каналов подклю- 5 выходы вторых элементов И блока

чены к выходу вычислительного блока, выходы элементов памяти соединены с первыми входами первых элементов И своего канала, вторые входы первых элементов И подключены к соответствующим выходам дешифратора, а выходы

первых элементов И соединены с выходом блока оперативной памяти, первый и второй входы входного блока, второй вход выходного блока, третий, четвертьй и пятый входы вычислительного блока и вторые и третий входы блока оперативной памяти соединены с соответствующими выходами программного блока, а третьи входы входного блока являются входами устройства, отличающееся тем, что, с целью повьш1ения надежности работы, в устройство введен блок синхронизации, состоящий из двух счетных триггеров, двух элементов И и инвертора, первый счетный триггер соединен своим входом с выходом генератора импульса, с первым входом первого элемента И и с входом инвертора, а выходом - с вторым входом первого элемента И, выход которого подключен к входу программного блока, второй счетный триггер входом соединен с выходом инвертора и с первым входом второг О элемента И, второй вход которого соединен с выходом второго счетного триггера, выход второго элемента И подключен к третьему входу вы- ходног о блока, а также введены в блок коммутации элемент ИЛИ-И и десятый элемент И, первые входы которых соединены с выходом второго элемента И блока синхронизации, а выходы - с вторыми входами триггеров памяти, а в каждый канал блока оперативной памяти введены элементы памяти, число которых определено реализуемой функцией, и соответственно им вторые элементы И, первые входы которых являются вторыми входами блока оперативной памяти, вторые входы вторых элементов И соединены с выходом второго элемента И блока синхрониза

оперативной памяти подключены к вторым входам элемента памяти, а вторые входы элемента ИЛИ-И и десятого элемента И блока коммутации соединены с соответствующими выходами программного блока.

Hcx-Q4Ht iu сигна/1

Нн(рорпационнь1й 6)fod триггера

Cuwpo6)fod триггера дых од триггера

Исходный сигнет

Нн(рорг1 анионный Sxod триггера

Синхробход триггера Выход триггера

Исходный сигнал

Ин1рарпаи,ионныи бгод триггера

Син еробход триггера дыход триггера

дыход генератора 36

иППу/1ЬСОб

дыход счетного

триггера Л до IXод з/емента /Ш

такт 1

такт (

тйнт() дыход инвертора 3

дыход счетного триггера 3

быход з епента Н34.

.

I

i

Фиг 2

HVVKT-rV-LrLJ

Фцг.5

Ко панд О С1 Син)(роимпу/1ьсь I

ды)(од 3/ierieHma Н9 (и г пу/ьс записи)

Рез та т бычис/1ения

(руинции о, И

Вь1)(од триггера 3

попяти

Нопанда С Нопаидо С5

CuHXpOUfifiy/fbCbl

Выход 3 ej4et ma. И/1Н-И16

Перепенная Qg

Выход триггера 15 папяти

Копанда С в

OjH pounny/ibCbi дыход элемента И25

Результат Ьычис/чения (функции U Qa Ot

)fod з впента 26 папрти

Ср

te

(риг. 5

6

Сри.6

| Устройство для дистанционного программного управления электроприводными механизмами | 1982 |

|

SU1071999A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для дистанционного программного управления электроприводными механизмами | 1984 |

|

SU1257614A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-02-07—Публикация

1986-06-19—Подача