(57) Изобретение относится к цифровой циентов. 1 з.п. ф-лы, 3 ил.

%

(Л

31654835

Изобретение относится к цифровой обработке сигналов и может быть использовано при реализации алгоритмов

вания равны Р, 5, Р 3 и Р3

(таким образом Рп. П-Р1 30).

КОМ

Через время задержки t

ком

W

затраспектрального анализа, цифровой фильт- чиваемое кодами /Xf/f Р; на прохожде устройств с заданными времен- ние через соответствующие коммутаторы

10

рации,

ными характеристиками на специализированных вычислительных устройствах.

Целью изобретения является повышение производительности устройства.

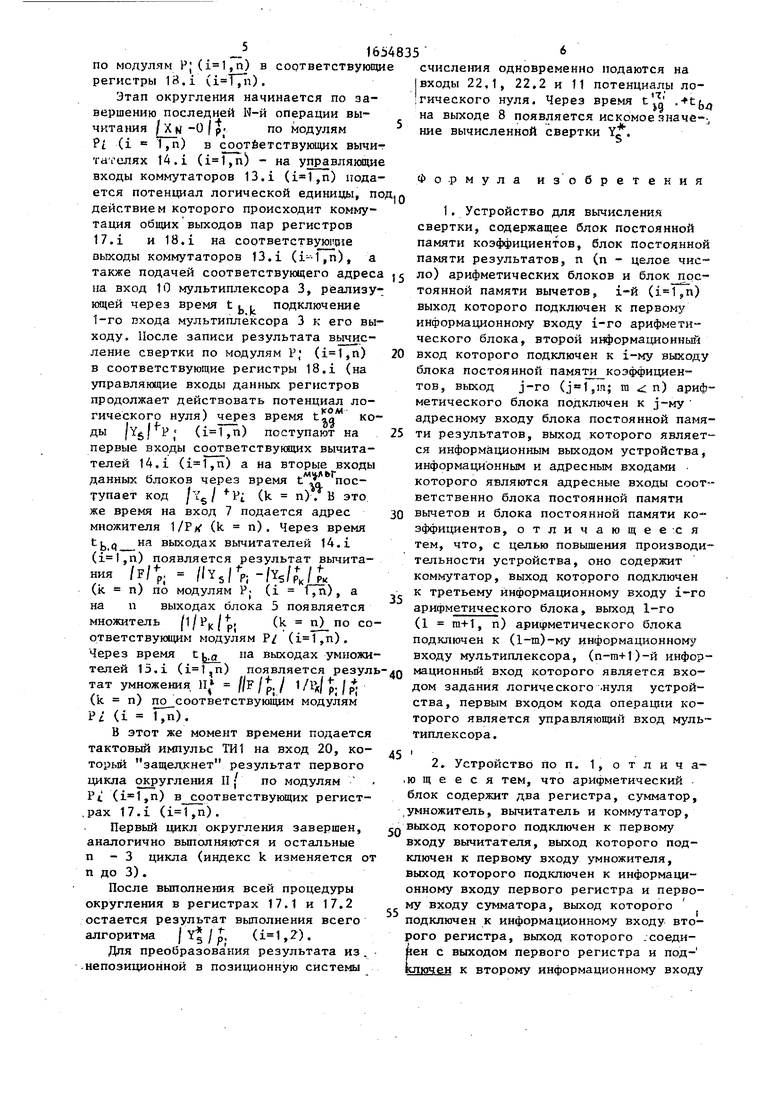

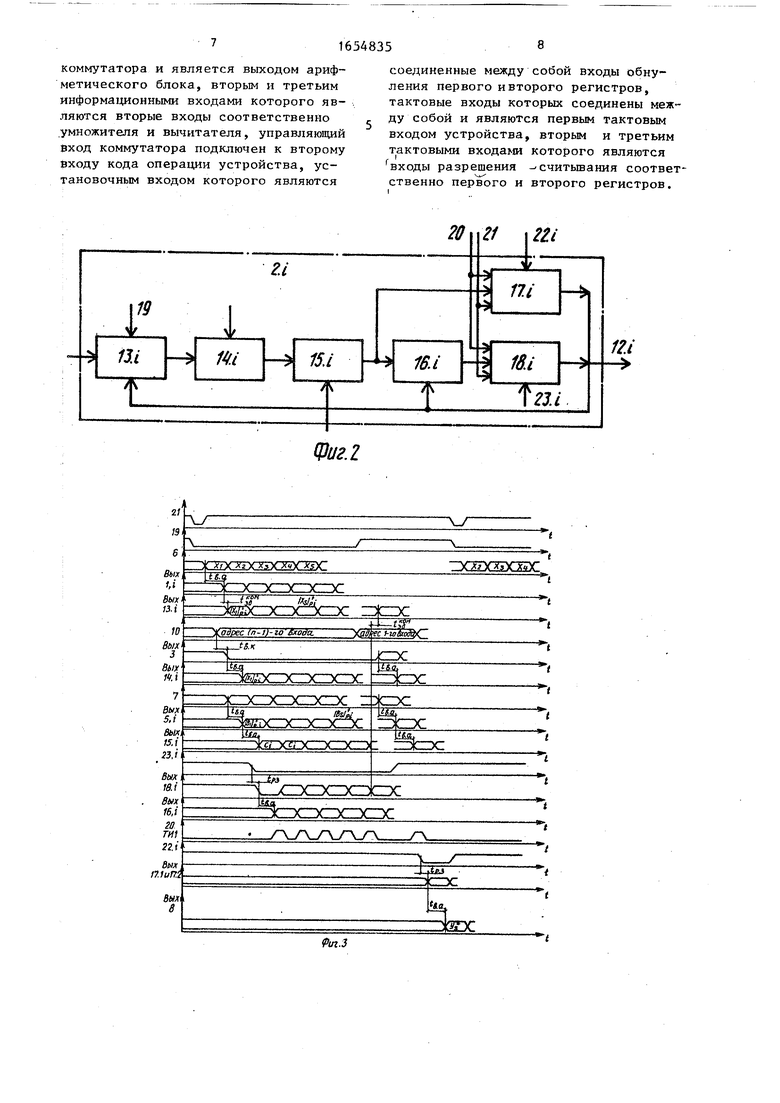

На фиг. 1 приведена функциональная схема устройства для вычисления свертки; на фиг. 2 - арифметический блок; на фиг. 3 - временные диаграммы работы устройства.

Устройство для вычисления свертки содержит (фиг. 1) блок 1 постоянной памяти вычетов, п арифметических блоков 2.1-2.П, мультиплексор 3, блок 4

постоянной памяти результатов, блок 5 Q является результат вычитания /Х,-0/ Р; постоянной памяти коэффициентов, ин- по соответствующим модулям Р(. (). формационный вход 6, адресный вход 7, На п выходах 5 появляется первый ко- инсрормационныи выход 8, вход 9 зада- коэффициент /В,/ Р , по соответст- ькя логического нуля и вход 10 кода вующим модулям P;(,n). Через время операции мультиплексора 3, адресный 25 с Ьй на вых°Дах умножителей 15.i (i

13,i (), данные коды поступают на входы соответствующих вычитателей 14.1 (,п), К этому моменту на вторые входы вычитателей 14.1 поступает код нуля с входа 9 мультиплексора 3. Это достигается заблаговременной подачей на время выбора канала ti адреса (п-1)-го входного канала на вход 75 10 мультиплексора 3. В этот же момент на вход 7 подается адрес первого коэффициента В /.

Таким образом, через время 1. Q на

выходах вычитателей 14.1 (.п) по .ж 1, появляется результат умножения

С J /Х; В по соответствующим

модулям Р (,п).

К этому же моменту на выходах регистров 18.1 (,п) появляется код нуля

ной, .. 18.

, Это достигается заблаговремен- на время задержки разрешения

вход 11 блока 4 и выходы 12.1-12.п соответствующих арифметических блоков 2.1-2.п.

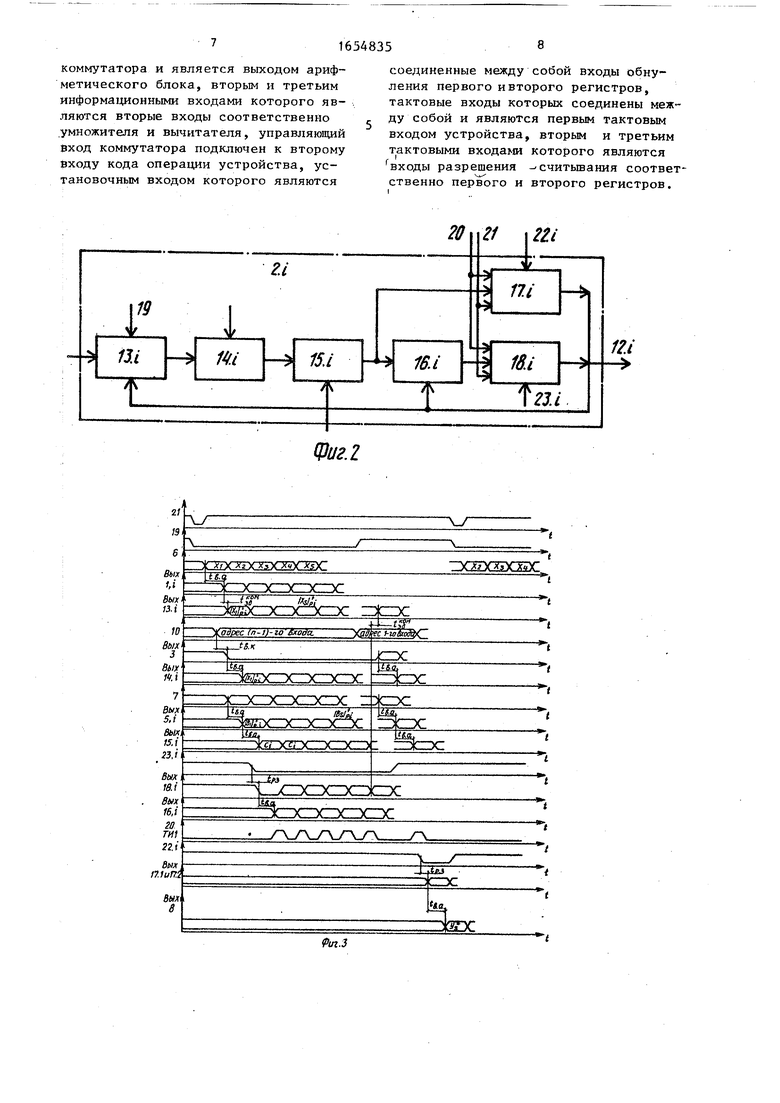

Арифметический блок (фиг. 2) содержит коммутатор 13.1, вычитатель о 14.1, умножитель 15.1, сумматор 16.1, регистры 17.1 и 18.1, вход 19 кода операции, тактовый вход 20, вход 21 обнуления регистров, входы 22.1 и 23.1 разрешения считывания соответст- ,вующих регистров 17.1 и 18.1.

Устройство работает следующим образом.

В исходном состоянии регистры 17.1 и 18.1 (,п) обнулены, общий сброс всех регистров происходит потенциалом логического нуля, поданно- (по модулям Р; () в соответствую- го на вход 21. На управляющие входы щие регистры 18.1 (). коммутаторов 13.1 (,п) подан потен- Устройство работает в конвейерном ре- циал логического нуля, под действием , жиме, что демонстрируется на времен- i которого происходят коммутации первых

35

40

РЯ1Р считывания,, подачей потенциала логического нуля на соответствующие входы 23.1 (,п), в результате чего через время tfe.a на выходах сумматоров, 16.1 (,п) появляется код суммы

/С(1 ПО МОДУЛЯМ Pt (,п) И В

это же время на вход 20 подается короткий импульс ТИ1 записи, который защелкивает результат суммирования

ных диаграммах (фиг. 3), т.е. в момент поступления кода входного отсчевходов коммутаторов 13.1 (,п) на соответствующие выходы данных блоков. Под действием кода первого нходнощих вычитателей 14.1 (,п), код

го отсчета X, через время выборки второго отсчета Х подается на вход адреса tL. на п выходах блока 1 появляются коды вычетов входного отсчета Х по соответствующим модулям Р; (,п)/Хч/ Р;.

Пример. Рассматривают устройство, содержащее три канала (); количество отсчетов для определения одного значения свертки N 3; осио55

6 и далее весь процесс выполняется аналогично изложенному (по входу 7 подается адрес коэффициента В, в су маторе происходит сложение /С | p. cfcj и т.д.). Процесс выполнения свертки реализуется до тех пор, пока Ы-м тактовым импуль сам ТИ1 не запишется результат вычис ления свертки /УЗ/Р; . ,

вания равны Р, 5, Р 3 и Р3

(таким образом Рп. П-Р1 30).

КОМ

Через время задержки t

ком

W

затрачиваемое кодами /Xf/f Р; на прохожде ние через соответствующие коммутаторы

чиваемое кодами /Xf/f Р; на прохожде ние через соответствующие коммутаторы

является результат вычитания /Х,-0/ Р; по соответствующим модулям Р(. (). На п выходах 5 появляется первый ко- коэффициент /В,/ Р , по соответст- вующим модулям P;(,n). Через время с Ьй на вых°Дах умножителей 15.i (i

13,i (), данные коды поступают на входы соответствующих вычитателей 14.1 (,п), К этому моменту на вторые входы вычитателей 14.1 поступает код нуля с входа 9 мультиплексора 3. Это достигается заблаговременной подачей на время выбора канала ti адреса (п-1)-го входного канала на вход 10 мультиплексора 3. В этот же момент на вход 7 подается адрес первого коэффициента В /.

Таким образом, через время 1. Q на

выходах вычитателей 14.1 (.п) по .ж является результат вычитания /Х,-0/ Р; по соответствующим модулям Р(. (). На п выходах 5 появляется первый ко- коэффициент /В,/ Р , по соответст- вующим модулям P;(,n). Через время с Ьй на вых°Дах умножителей 15.i (i

1, появляется результат умножения

С J /Х; В по соответствующим

модулям Р (,п).

К этому же моменту на выходах регистров 18.1 (,п) появляется код нуля

ной, .. 18.

, Это достигается заблаговремен- на время задержки разрешения

(по модулям Р; () в соответствую- щие регистры 18.1 (). Устройство работает в конвейерном ре жиме, что демонстрируется на времен-

РЯ1Р считывания,, подачей потенциала логического нуля на соответствующие входы 23.1 (,п), в результате чего через время tfe.a на выходах сумматоров, 16.1 (,п) появляется код суммы

/С(1 ПО МОДУЛЯМ Pt (,п) И В

это же время на вход 20 подается короткий импульс ТИ1 записи, который защелкивает результат суммирования

по модулям Р; () в соответствую- щие регистры 18.1 (). Устройство работает в конвейерном р жиме, что демонстрируется на времен-

ных диаграммах (фиг. 3), т.е. в момент поступления кода входного отсчета

/Х,| Р2 на входы соответствун)щих вычитателей 14.1 (,п), код

второго отсчета Х подается на вход

второго отсчета Х подается на вход

6 и далее весь процесс выполняется аналогично изложенному (по входу 7 подается адрес коэффициента В, в сумматоре происходит сложение /С | p. cfcj и т.д.). Процесс выполнения свертки реализуется до тех пор, пока Ы-м тактовым импульсам ТИ1 не запишется результат вычисления свертки /УЗ/Р; . ,

„516348356

по модулям P|(,n) в соответствующие счисления одновременно подаются на

регистры 18.1 ().

Этап округления начинается по завершению последней Н-и операции вычитания /X ц -0 f р- по модулям l (1 1,п) в соответствующих вычи- тателях I4.i (,п) - на управляющие входы коммутаторов 13.1 (,п) подается потенциал логической единицы, под,Q действием которого происходит коммутация общих выходов пар регистров 17.1 и 18.1 на соответствующее выходы коммутаторов 13.1 (i-1,n), а также подачей соответствующего адреса ло) арифметических блоков и блок jrcoc- на вход 10 мультиплексора 3, реализу- тоянной памяти вычетов, 1-й (,n) кяцей через время t , подключение выход которого подключен к первомз 1-го пхода мультиплексора 3 к его вы- информационному входу 1-го арифмети- ходу, После записи результата вычис- ческого блока, второй информационный ление свертки по модулям Р; (,п) 20 вход которого подключен к 1-му выходу в соответствующие регистры 18.1 (на блока постоянной памята коэффициентов, выход j-го (je1,m; m n) арифметического блока подключен к j-му

гического нуля) через время t«n ко- адресному входу блока постоянной памя- rf -- ™

входы 22,1, 22.2 и 11 потенциалы логического нуля. Через время tV -+tba на выходе 8 появляется искомое значе--, ние вычисленной свертки Y.

Формула изобретения

1. Устройство для вычисления свертки, содержащее блок постоянной памяти коэффициентов, блок постоянной памяти результатов, п (п - целое чисуправляющие входы данных регистров продолжает действовать потенциал локоды . (,n) поступают на 25 ти результатов, выход которого являет

ся информационным выходом устройства, информационным и адресным входами которого являются адресные входы соот ветственно блока постоянной памяти 30 вычетов и блока постоянной памяти коэффициентов, отличающееся на выходах вьгчитателей 14.1 (,п) появляется результат вычитания /F/ + . /lYjV/Y /k

(k п) по модулям Р. (1 f7n), a

WP первые входы соответствующих вычитателей 14.1 (,п) а на вторые входы данных блоков через время t А поступает код / LS/ Pi (k п). В это же время на вход 7 подается адрес множителя 1/Prf (k n). Через время

на

п

35

выходах блока 5 появляется

множитель |1/ к/ р IbL по со ответствующим модулям Р/ (,п). Через время t .g на выходах умножителей 15.1 (,n) появляется резуль- Q мационный вход которого . тат умножения 11 //F / „. / 1/ly p. | pi дом задания логического

(k п) по соответствующим модулям Pi (1 1,п).

В этот же момент времени подается тактовый импульс ТИ1 на вход 20, который защелкнет результат первого цикла округления II; по модулям I t (,п) в соответствующих регистрах 17.1 (,п).

Первый цикл округления завершен, аналогично выполняются и остальные п - 3 цикла (индекс k изменяется от п до 3).

После выполнения всей процедуры округления в регистрах 17.1 и 17.2 остается результат выполнения всего алгоритма | Y / р. (,2).

Для преобразования результата из. непозиционной в позиционную системы

тем, что, с целью повышения производительности устройства, оно содержит коммутатор, выход которого подключен к третьему информационному входу 1-го арифметического блока, выход 1-го (1 га+1, п) арифметического блока подключен к (1-т)-му информационному входу мультиплексора, (п-т+1)-й инфо является вхо- нуля устройства, первым входом кода операции которого является управляющий вход мультиплексора.

i

2. Устройство по п. 1, о т л и ч а- ,ю щ е е с я тем, что арифметический блок содержит два регистра, сумматор, умножитель, вычитатель и коммутатор, выход которого подключен к первому входу вычитателя, выход которого подключен к первому входу умножителя, выход которого подключен к информационному входу первого регистра и первому входу сумматора, выход которого подключен к информационному входу второго регистра, выход которого .соединен с выходом первого регистра и под- ключей к второму информационному входу

45

50

ло) арифметических блоков и блок jrcoc- тоянной памяти вычетов, 1-й (,n) выход которого подключен к первомз информационному входу 1-го арифмети- ческого блока, второй информационный вход которого подключен к 1-му выходу блока постоянной памята коэффициенвходы 22,1, 22.2 и 11 потенциалы логического нуля. Через время tV -+tba на выходе 8 появляется искомое значе--, ние вычисленной свертки Y.

ло) арифметических блоков и блок jrcoc- тоянной памяти вычетов, 1-й (,n) выход которого подключен к первомз информационному входу 1-го арифмети- ческого блока, второй информационный вход которого подключен к 1-му выходу блока постоянной памята коэффициенФормула изобретения

1. Устройство для вычисления свертки, содержащее блок постоянной памяти коэффициентов, блок постоянной памяти результатов, п (п - целое чисся информационным выходом устройства, информационным и адресным входами которого являются адресные входы соот ветственно блока постоянной памяти 0 вычетов и блока постоянной памяти коэффициентов, отличающееся

5

Q мационный вход которого . дом задания логического

тем, что, с целью повышения производительности устройства, оно содержит коммутатор, выход которого подключен к третьему информационному входу 1-го арифметического блока, выход 1-го (1 га+1, п) арифметического блока подключен к (1-т)-му информационному входу мультиплексора, (п-т+1)-й инфо является вхо- нуля устройства, первым входом кода операции которого является управляющий вход мультиплексора.

i

2. Устройство по п. 1, о т л и ч а- ,ю щ е е с я тем, что арифметический блок содержит два регистра, сумматор, умножитель, вычитатель и коммутатор, выход которого подключен к первому входу вычитателя, выход которого подключен к первому входу умножителя, выход которого подключен к информационному входу первого регистра и первому входу сумматора, выход которого подключен к информационному входу второго регистра, выход которого .соединен с выходом первого регистра и под- ключей к второму информационному входу

5

0

коммутатора и является выходом арифметического блока, вторым и третьим информационными входами которого являются вторые входы соответственно умножителя и вычитателя, управляющий вход коммутатора подключен к второму входу кода операции устройства, установочным входом которого являются

соединенные между собой входы обнуления первого и второго регистров, тактовые входы которых соединены между собой и являются первым тактовым входом устройства, вторым и третьим тактовыми входами которого являются fвходы разрешения считывания соответственно первого и второго регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1236617A1 |

| Устройство для умножения комплексных чисел в модулярной системе счисления | 1985 |

|

SU1280625A1 |

| Арифметическое устройство | 1987 |

|

SU1441397A1 |

| Устройство для расширения системы оснований модулярного кода | 1985 |

|

SU1282134A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Устройство для обнаружения и исправления ошибок в непозиционном коде | 1983 |

|

SU1134941A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство параллельной обработки видеоинформации | 1984 |

|

SU1262527A1 |

| УСТРОЙСТВО ДЛЯ БЫСТРОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2012051C1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

Фиг. 2

Вш 171иТП

Рш.З

| Цифровой фильтр | 1984 |

|

SU1246344A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1290350A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-07—Публикация

1989-06-14—Подача