Изобретение относится к вычислитель ной технике и может быть использовано в высокопроизводительных системах обоз- ботки информации, в первую очередь построенных с применением БИС.

Цель изобретения - расширение функциональных возможностей за счет задания двоичным кодом величины сдвига при разрядности устройства, не равной 2Р (р 0, 1 . .).

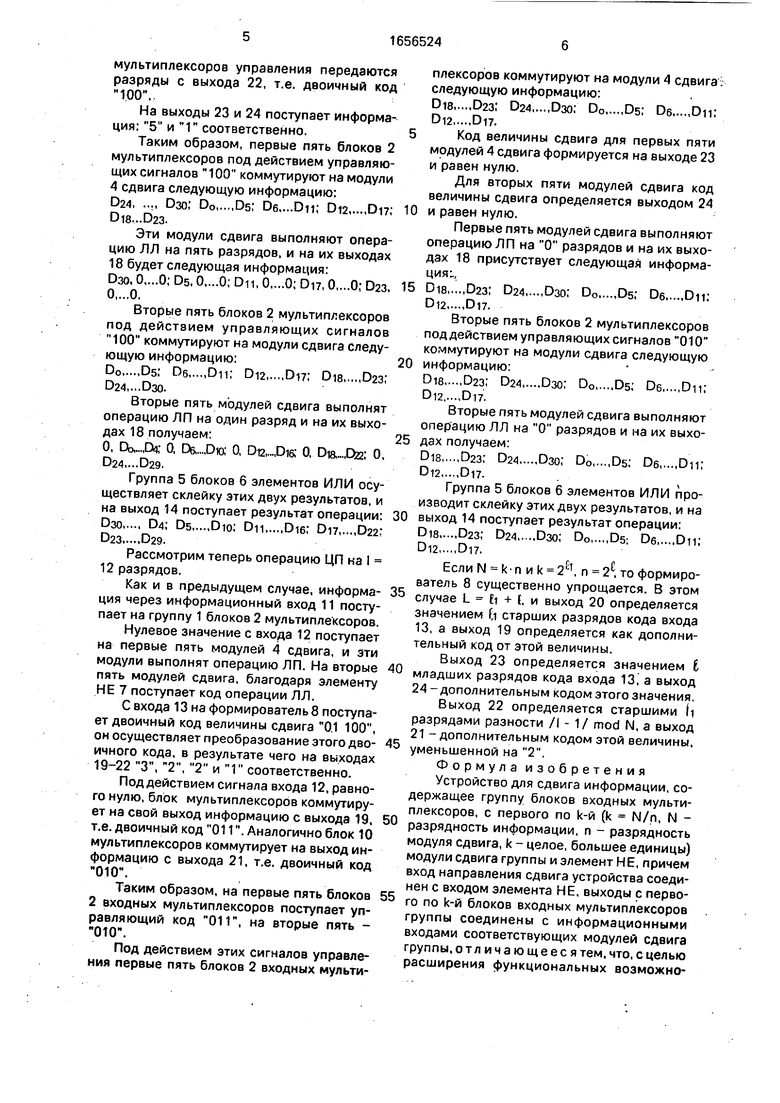

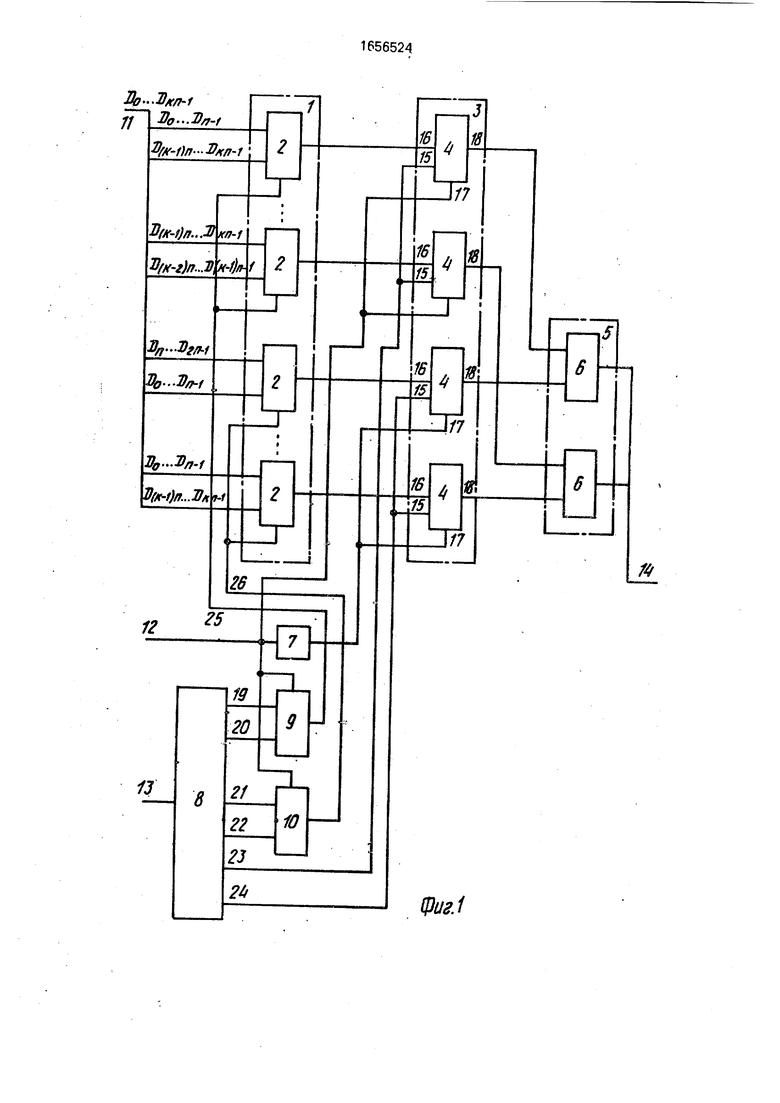

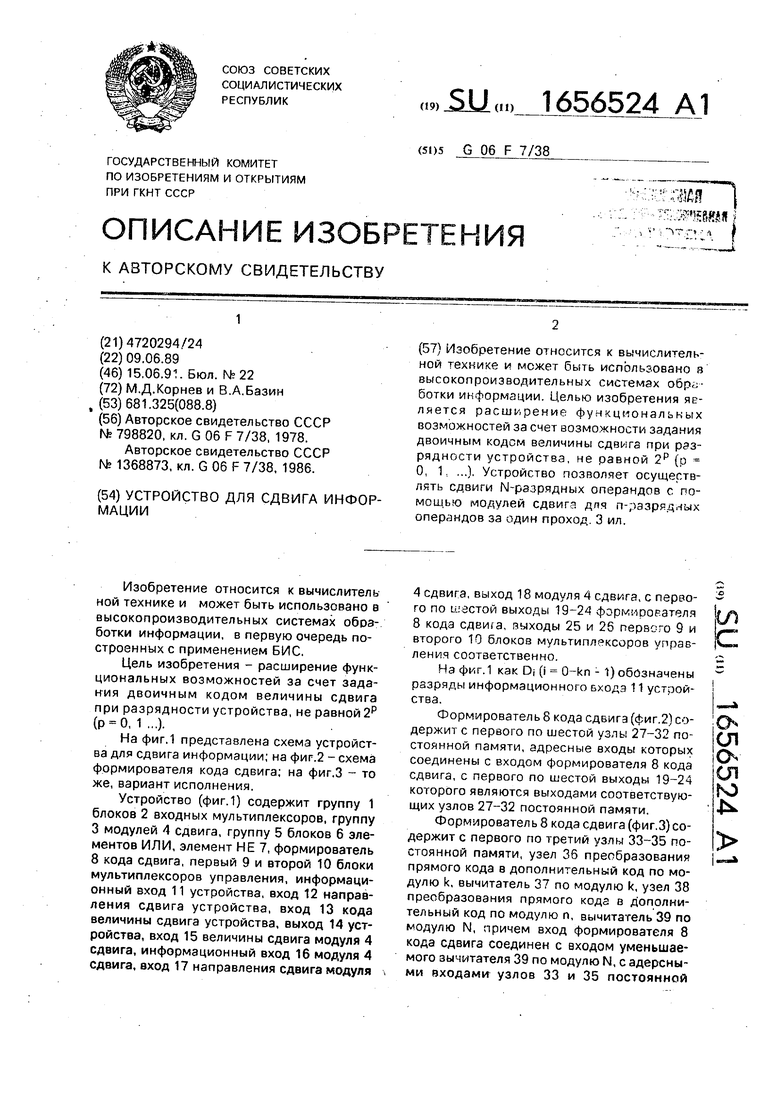

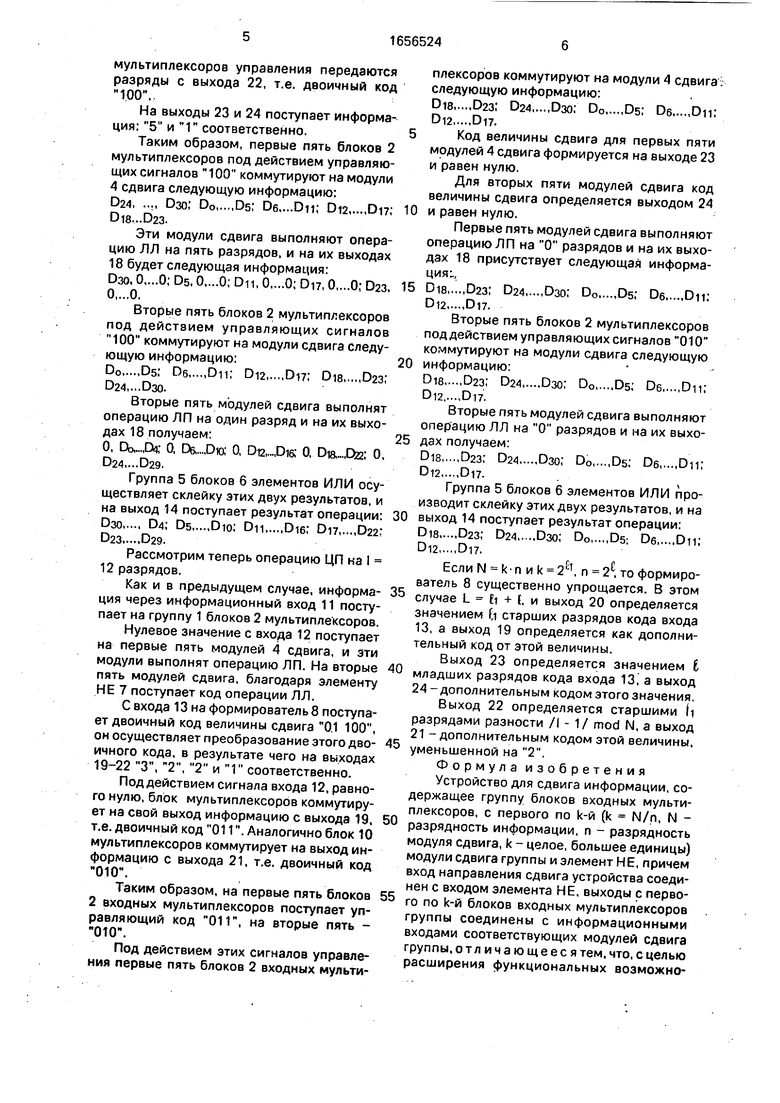

На фиг.1 представлена схемэ устройства для сдвига информации; на фиг 2 - схема формирователя кода сдвига; на фиг.З - то же,вариант исполнения

Устройство (фиг.1) содержит группу 1 блоков 2 входных мультиплексоров, группу 3 модулей 4 сдвига, группу 5 блоков 6 элементов ИЛИ, элемент НЕ 7, формирователь 8 кода сдвига, первый 9 и второй 10 блоки мультиплексоров управления, информационный вход 11 устройства, вход 12 направления сдвига устройства, вход 13 кода величины сдвига устройства, выход 14 устройства, вход 15 величины сдвига модуля 4 сдвига, информационный вход 16 модуля 4 сдвига, вход 17 направления сдвига модуля

4 сдвига, выход 18 модуля 4 сдвига, с перяо- го по и естой выходы 19 24 формпрогателя 8 кода сдви1а, выходы 25 и 25 первс-о 9 и второго 10 блокоз мультиплексоров управления соответственно

На фиг 1 как О, (i 0 -kn - 1) обозначены разряды информационного ьлодч 11 устройства.

Формирователь 8 кода сдвига (фиг.2) содержит с первою по шестой узлы 27-32 постоянной памяти, адресные входы которых соединены с входом формирователя 8 кода сдвига, с первого по шестой выходы 19-24 которого являются выходами соответствующих узлов 27-32 постоянной памяти.

Формирователь 8 кода сдвига (фиг.З) содержит с первого по третий узчы 33-35 постоянной памяти, узел 36 преобразования прямого кода в дополнительный код по модулю k, вычитатель 37 по модулю к, узел 38 преобразования прямого кода в дополнительный код по модулю п, вычитатель 39 по модулю N. причем вход формирователя 8 кода сдвига соединен с входом уменьшаемого зычитателя 39 по модулю N, с адерсны- ми входами узлов 33 и 35 постоянной

О

ел о ел ю

памяти, вход единичного потенциала устройства соединен с входом вычитаемого вы- читателя 39 по модулю N, выход которого соединен с адресным входом узла 34 постоянной памяти, выход узла 33 постоянной памяти соединен с выходом 20 и через узел 36 преобразователя прямого кода в дополнительный код по модулю k с выходом 19 формирователя 8 кода сдвига, выход узла 34 постоянной памяти соединен с входом вычитаемого вычитателя 37 по модулю k и с выходом 22 формирователя 8 кода сдвига, выход 21 которого соединен о%ыходом вычитателя 37 по модулю k, вход уменьшаемого которого соединен с входом константы (k - 2) устройства, выход узла 35 постоянной памяти соединен с выходом 23 и через узел 38 преобразования прямого кода в дополнительный код по модулю п с выходом 24 формирователя 8 кода Сдвига.

Устройство (фиг.1) оруществляет циклические сдвиги влево (ЦЛ)1 и вправо (ЦП) на величину 1 /0 I kn - 1 / N - (N k n, k - целое, k 1) - разрядной информации, имеющей следующий вид:

Do, Di Dn-i; Dn, Dn-t-1 D2n-i; ...

D(k-i)nDkn-1.

При выполнении операции ЦЛ на вход 12 подается сигнал логической единицы, при выполнении операции ЦП на тот же вход подается сигнал логического нуля.

Формирователь 8 кода сдвига осуществляет преобразование величины сдвига устройства по следующим правилам: выход 19 выдает информацию

()modk,

где X - целая часть X; выход 20 выдает информацию

Ж

выход 21 выдает информацию (k.2(l-1)modN )mod|C;

выход 22 выдает информацию

г ( I - 1 ) mod N , 1nj

рядность их выходов - не менее Iog2k для узлов 27-30 и 1од2П - Для узлов 31 и 32.

В формирователе 8 кода сдвига (фиг.З) разрядность входов узлов 33-35 постоянной памяти не менее log2N , разрядность выходной информации узлов 33 и 34 не менее Iog2k , узла 35 - не менее Iog2n .

В узлах 33, 35 по адресам I содержится

информация

фиЦ

I

n соответствен

но, а в узле 34 по адресу I содержится информация - , где I (I -1) mod N.

Количество двоичных разрядов, необхо- димое для кодирования величины сдвига устройства аналога, обозначим L log2k п,

где Х - ближайшее целое, бопьшее или равное X.

Количество двоичных разрядов, необходимое для кодирования величины сдвига (I), подаваемой на модули сдвига, реализованные согласно аналогу, обозначим через

t log2n.

Количество двоичных разрядов, необходимое для кодирования управления блоками входных мультиплексоров, равно Iog2k .

Рассмотрим работу устройства (фиг.1) на примере N 30, n 6. В этом случае И.

Рассмотрим сначала операцию ЦЛ на I 29 разрядов.

Информация D0D29 через информационный вход 11 порциями по 6 разрядов поступает на группу 1 блоков 2 входных мультиплексоров.

Единица с входа 12 поступает непос- редственно на входы 17 первых пяти модулей сдвига, и эти модули сдвига будут выполнять операцию Сдвиг влево логический (ЛЛ). На входы 17 вторых пяти модулей благодаря элементу НЕ 7 поступает код операции Сдвиг логический вправо (ЛП).

Величина сдвига с входа 13, поступающая на формирователь 8, имеет следующий вид: 11 101. На выходах 19-22 формирователя 8 имеем Г, 4, 4, 4 соответствен- но.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| КОМБИНАЦИОННЫЙ РЕКУРРЕНТНЫЙ ФОРМИРОВАТЕЛЬ ОСТАТКОВ | 1992 |

|

RU2029435C1 |

| Устройство для сдвига операндов | 1988 |

|

SU1633391A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство для деления чисел в модулярной системе счисления | 1990 |

|

SU1756887A1 |

| УМНОЖИТЕЛЬ ПО МОДУЛЮ | 2020 |

|

RU2751802C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПРЕДСКАЗАННЫХ СИГНАЛОВ ЧЕТНОСТИ ПРИ СДВИГАХ ДВОИЧНЫХ КОДОВ | 1992 |

|

RU2045772C1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2025897C1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизволительных системах обр,, Ьотки информации Целью изобретения яг- ляется расширениг фу цпональкых возможностей за снег возможности задания двоичным кодом величины сдвига при разрядности устройства, че равной 2Р (о О 1 ...). Устройство позволяет осуществлять сдвиги N-рафодных операндов с го- мощью модулей сдвиги для п ,133ррд.ных операндов за один проход 3 ил.

выход 23 выдает информацию

,

выход 24 выдает информацию (п-(1- n)modn.

В формирователе 8 кода сдвига (фиг.2) разрядность адресного входа узлов 27-32 постоянной памяти не менее logaN , разЕдиничное значение через вход 12 устройства коммутирует на выход блока 9 мультиплексоров управления второй вход, и на выход блока 9 мультиплексоров управления поступают разряды с выхода 20, т.е. в двоичном изображении код 100. Под действием единичного значения с входа 12 блок 10 мультиплексоров управления также коммутирует второй вход, и на выход блока 10

мультиплексоров управления передаются разряды с выхода 22, т.е. двоичный код 100.

На выходы 23 и 24 поступает информация: 5 и Г соответственно.

Таким образом, первые пять блоков 2 мультиплексоров под действием управляющих сигналов 100 коммутируют на модули 4 сдвига следующую информацию: D24 Озо; DoDs; De,...Dn; 012Di,

D18-..D23.

Эти модули сдвига выполняют опера цию ЛЛ на пять разрядов, и на их выходах 18 будет следующая информация: Озо, 0....0; Ds, 0....0; Dn, 0....0; Diy, 0....0; Оаз, 0....0.

Вторые пять блоков 2 мультиплексоров под действием управляющих сигналов 100 коммутируют на модули сдвига следующую информацию: DoDs; ОбDn; Di2DI ; DieD23,

D24....D30.

Вторые пять модулей сдвига выполнят операцию ЛП на один разряд и на их выходах 18 получаем: О, Оо,„.,О4- 0, Об,...,0ю; О, DCD 0, Dia...,D22; О,

D24....D29.

Группа 5 блоков 6 элементов ИЛИ осуществляет склейку этих двух результатов, и на выход 14 поступает результат операции: Озо D4; DsОю; ОнDie; Di 022:

023029Рассмотрим теперь операцию ЦП на I 12 разрядов.

Как и в предыдущем случае, информа- ция через информационный вход 11 поступает на группу 1 блоков 2 мультиплексоров.

Нулевое значение с входа 12 поступает на первые пять модулей 4 сдвига, и эти модули выполнят операцию ЛП. На вторые пять модулей сдвига, благодаря элементу НЕ 7 поступает код операции ЛЛ.

С входа 13 на формирователь 8 поступает двоичный код величины сдвига 01 100, он осуществляет преобразование этого дво- ичного кода, в результате чего на выходах 19-22 3, 2, 2 и 1 соответственно.

Под действием сигнала входа 12, равного нулю, блок мультиплексоров коммутирует на свой выход информацию с выхода 19, т.е. двоичный код 011. Аналогично блок 10 мультиплексоров коммутирует на выход информацию с выхода 21, т.е. двоичный код 010.

Таким образом, на первые пять блоков 2 входных мультиплексоров поступает управляющий код 011, на вторые пять - 010.

Под действием этих сигналов управления первые пять блоков 2 входных мультиплексоров коммутируют на модули 4 сдвига

следующую информацию:

Die023; D24Озо; DoDs; DeOn;

D12D17.

Код величины сдвига для первых пяти модулей 4 сдвига формируется на выходе 23 и равен нулю.

Для вторых пяти модулей сдвига код величины сдвига определяется выходом 24 и равен нулю.

Первые пять модулей сдвига выполняют операцию ЛП на О разрядов и на их выходах 18 присутствует следующая информация;, Die023: 024Озо; О0Ds; DeOn:

Dl2D17.

Вторые пять блоков 2 мультиплексоров под действием управляющих сигналов 010 коммутируют на модули сдвига следующую информацию: Die02з; 024Озо: DoDs; DeOn;

Di2,...,Dl7.

Вторые пять модулей сдвига выполняют операцию ЛЛ на О разрядов и на их выходах получаем: Die023; D24Озо; DoDs; DeDn;

Di2Dl7.

Группа 5 блоков б элементов ИЛИ производит склейку этих двух результатов, и на выход 14 поступает результат операции: DIB023; 024,. .,Озо; DoDs: ОбDn;

D12D17.

Если N k-n и k 21, n 2 , то формирователь 8 существенно упрощается. В этом случае L ti + (, и выход 20 определяется значением (.1 старших разрядов кода входа 13, а выход 19 определяется как дополнительный код от этой величины.

Выход 23 определяется значением t младших разрядов кода входа 13. а выход 24 -дополнительным кодом этого значения.

Выход 22 определяется старшими h разрядами разности /1-1/ mod N, а выход 21 -дополнительным кодом этой величины, уменьшенной на 2.

Формула изобретения

Устройство для сдвига информации, содержащее группу блоков входных мультиплексоров, с первого по k-й (k N/n, N - разрядность информации, n - разрядность модуля сдвига, k - целое, большее единицы) модули сдвига группы и элемент НЕ, причем вход направления сдвига устройства соединен с входом элемента НЕ, выходы с первого по k-й блоков входных мультиплексоров группы соединены с информационными входами соответствующих модулей сдвига группы, от л ичающееся тем, что. с целью расширения функциональных возможностей путем задания двоичным кодом величины сдвига при разрядности устройства, не равной 2Р (р 0, 1, ...). оно содержит с (k + 1)-го по 2k-u модули сдвига группы, группу блоков элементов ИЛИ, формирователь кода сдвига, первый и второй блоки мультиплексоров управления, причем вход кода величины сдвига устройства соединен с входом формирователя кода сдвига, первый и второй выходы которого соединены с соответствующими информационными входами первого блока мультиплексоров управления, выход которого соединен с управляющими входами с первого по k-й блоков входных мультиплексоров группы, третий и четвертый выходы формирователя кода сдвига соединены соответственно с первым и вторым информационными входами второго блока мультиплексоров управления, выход которого соединен с управляющими входами с (k + 1)-го по 2k-ft блоков входных мультиплексоров группы, выходы которых соединены с информационными входами соответствующих модулей сдвига группы, входы направления сдвига которых соединены с выходом элемента НЕ, вход которого соединен с управляющими входами первого и второго блоков мультиплексоров управления и с входами направления сдвига с первого по k-й модулей сдвига группы, пятый и

шестой выходы формирователя кода сдвига соединены с входами величины сдвига соответственно с первого по k-й и с (k + 1)-го по 2k-й модулей сдвига группы, выходы с первого по k-й модулей сдвига группы соединены с первыми входами соответствующих блоков элементов ИЛИ группы, выходы которых являются выходом устройства, выходы с (k + 1)-го no 2k-fl модулей сдвига группы

соединены соответственно с вторыми входами блоков элементов ИЛИ группы, входы разрядов j-ro информационного входа 1-го блока входных мультиплексоров группы (i, J 1 - k) соединены соответственно с входами

разрядов М-ой группы информационного входа устройства

(М {(I+J- 1), npnj (k-l + 1) Vl (l+J-k- 1). при (k-i+ 1),

информационные входы первого блока входных мультиплексоров группы соединены с соответствующими информационными входами 2k-ro блока входных мультиплексоров группы, информационные входы Ј-го (J. 2 - k) блока входных мультиплексоров группы соединены с соответствующими информационными входами (k + I - 1)-го блока входных мультиплексоров группы.

Гг

Ш.

Й 7

H

&

м 7г 7г 1г

9

г/

92

Л

t-t

Ј /(

иь-оц

Я

.

91

St

(М

il-up-Hfa

91

1-им

tf-Uft-XjQ

l-Uitg-Ud-Xfa

-U((L I

i -Ofj 399991

фиг.2

| Устройство для сдвига информации | 1978 |

|

SU798820A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сдвига операндов | 1986 |

|

SU1368873A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-09—Подача