1

Изобретение относится к вычислительной технике и может быть использовано при разработке микропрограммных устройств управления ЭВМ.

Цель изобретения - расширение функциональных возможностей устройст- ва за счет реализации переменной час тоты формирования микрокоманд.

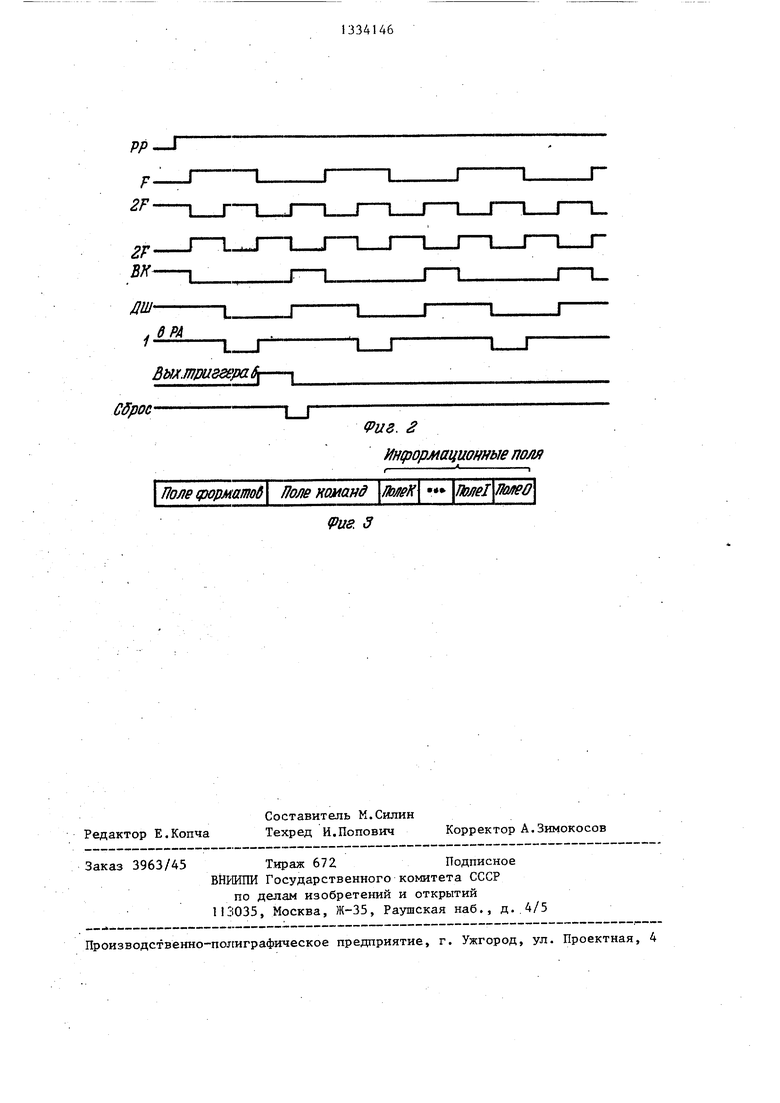

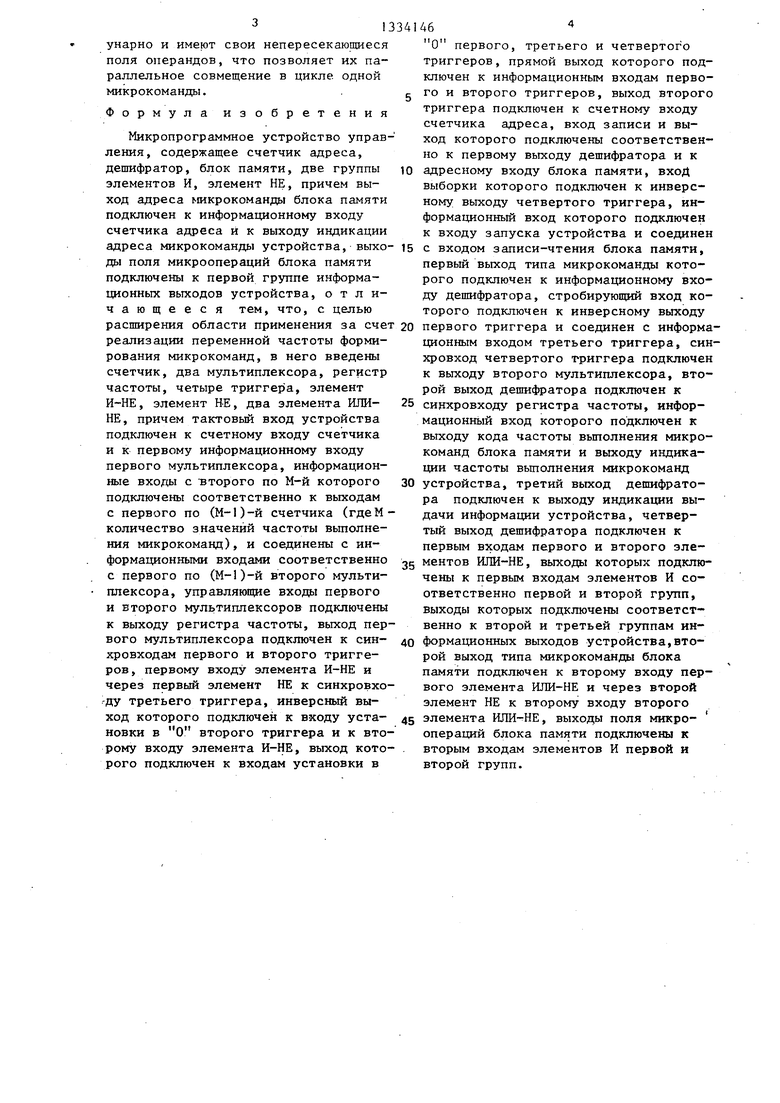

На фиг.1 представлена функциональ ная схема устройства; на фиг.2 - временные диаграммы работы устройства; на фиг.З - формат микрокоманд.

Устройство содержит счетчик 1 адре са, дешифратор 2, триггеры 3-6, группы 7 и 8 элементов И, элемент НЕ 9, блок iО Памяти, первый 11 и второй 12 мультиплексоры, счетчик 13, регистр 14 частоты, второй элемент НЕ 15, элемент И-НЕ 16, элеме.нты ИЛИ-НЕ 17 и 18, входы синхроимпульсов 19, запуска 20, индикации выдачи информации 21, вторая 22, третья 23, первая 24 группы информационных выходов, выход 25 индикации адреса следующей микрокоманды и выход 26 индикации частоты выполнения микрокоманд устройства.

Устройство работает следующим образом.

В блок 10 памяти предварительно в режиме подготовки устройства записывается программа управления устройством Слибо это блок памяти постоянного запоминающего устройства ПЗУ с заранее заданной программой) согласно временным диаграммам (фиг.2). При поступлении на вход 20 устройства сигнала высокого уровня триггер 3 под действием тактир /ющего сигнала с выхода мультиплексора 11 устанавливается в высокий зфонень, в результате триггеры 4, 5 и 6 отрабатывают конвейерную цепочку разбора микрокоманды под действием тактирующих сигналов с выхода мультиплексора 12. На выходах триггеров 3 - 6 согласно временным диаграммам (фиг.2) формируются синхросигналы управления блоком памяти ВК, дешифратором ДШ, регистром адреса +1, синхросигнал Сброс выполненного цикла разбора микрокоманды.

В устройстве реализован принцип разбора микрокоманд под действием тактирующего сигнала с двойной частотой стробируюш;их сигналов.

Сигнал с частотой F поступает на вход счетчика 13 и вход первого муль

34I462

типлексора II .. На выходах счетчика 13 формируются синхросигналы F/2, F/4, F/8 ... .На мультиплексоры 11 и 12 заведены сигналы таким образом, что на одноименных входах мультиплексора 11 частота вдвое меньше, чем на мультиплексору 12. Таким образом, при любом коде частоты на вы- 10 ходах регистра 14 частоты на управляющих входах мультиплексора присутствует один и тот же информационный код, а на выходе мультиплексоров, согласно фиг.2, частота синхросигна15 лов отличается в 2 раза. По переднему фронту син:хросигнала триггер 3 устанавливается в 1. С инверсного выхода этого триггера сигнал выборки кристалла поступает на блок IО памя20 |ги. Появление на выходе триггера 3 сигнала высокого уровня и через чет- рерть периода поступление тактирующего сигнала на тактирующие входы триггеров 4 и 5 формируют сигналы управ25 Ленин дешифратором 2 ДШ и прибавления +1 в счетчик адреса 1. Через четверть периода на тактирующий вход триггера 6 приходит положительный фронт синхросигнала, который при на30 личии сигнала ДШ устанавливает инверсный выход триггера в 1 и через четверть периода с приходом положи- тельного фронта сигнала на выходе элемента И-НЕ 6 формируется сигнал

2g сброса триггеров 3, 4 и 6.

Формат микрокоманд устройства приведен на фиг.З.

Каждое слово блока 10 памяти имеет формат, приведенный на фиг.З. Первые

40 два старших разряда определяют команды формата 0. Этот формат характеризуется максимальным быстродействием и реализует следующие микрокоманды: запись поля О памяти в счетчик адре45 са, запись поля 1 памяти в регистр частоты, вьщача всех информационных разрядов из блока памяти (исключая вторую группу информационных выходов блока памяти), формирование признака

5Q формата 1 или 2 устройства. При нали-. чии на четвертом выходе дешифратора 2 признака формата I или 2 анализируется третий информационный выход блока 10 памяти на элементах ШШ-НЕ

55 17 и 18. Нулевое значение этого сигнала соответствует командам формата 1 устройства, единичное - командам формата 2 устройства. Команды выполняются и кодируются в каждом формате

313

унарно и имеют свои непересекаюроцеся поля операндов, что позволяет их параллельное совмещение в цикле одной микрокоманды..

Формула изобретения

Микропрограммное устройство управления, содержащее счетчик адреса, дешифратор, блок памяти, две группы элементов И, элемент НЕ, причем выход адреса микрокоманды блока памяти подключен к информационному входу счетчика адреса и к выходу индикации адреса микрокоманды устройства, выхо- ды поля микроопераций блока памяти подключены к первой группе информа- ционньпс выходов устройства, отличающееся тем, что, с целью распмрения области применения за счет реализации переменной частоты формирования микрокоманд, в него введены счетчик, два мультиплексора, регистр частоты, четыре триггера, элемент И-НЕ, элемент Н-Е, два элемента ИЛИ- НЕ, причем тактовый вход устройства подключен к счетному входу счетчика и к первому информационному входу первого мультиплексора, информационные входы с второго по М-й которого подключены соответственно к выходам с первого по (М-1)-й счетчика (гдеМ- количество значений частоты выполнения микрокоманд), и соединены с информационными входами соответственно с первого по (М-1)-й второго мультиплексора, управляющие входы первого и второго мультиплексоров подключены к выходу регистра частоты, выход первого мультиплексора подключен к син- хровходам первого и второго триггеров, первому входу элемента И-НЕ и через первый элемент НЕ к синхровхо- -ду третьего триггера, инверсный выход которого подключен к входу уста- ковки в о второго триггера и к второму входу элемента И-НЕ, выход кото- рого подключен к входам установки в

46

О первого, третьего и четвертог о триггеров, прямой выход которого подключен к информационным входам первого и второго триггеров, выход второго триггера подключен к счетному входу счетчика адреса, вход записи и выход которого подключены соответственно к первому выходу дешифратора и к адресному входу блока памяти, вход выборки которого подключен к инверсному выходу четвертого триггера, информационный вход которого подключен к входу запуска устройства и соединен с входом записи-чтения блока памяти, первый выход типа микрокоманды которого подключен к информационному входу дешифратора, стробирующий вход которого подключен к инверсному выходу первого триггера и соединен с информационным входом третьего триггера, син хровход четвертого триггера подключен к выходу второго мультиплексора, второй выход дешифратора подключен к синхровходу регистра частоты, инфор- мационнь1й вход которого подключен к выходу кода частоты выполнения микрокоманд блока памяти и выходу индикации частоты вьтолнения микрокоманд устройства, третий выход дешифратора подключен к выходу индикации выдачи информации устройства, четвертый выход дешифратора подключен к первым входам первого и второго элементов ШШ-НЕ, выходы которых подключены к первым входам элементов И соответственно первой и второй групп, выходы которых подключены соответственно к второй и третьей группам информационных выходов устройства,второй выход типа микрокоманды блока памяти подключен к второму входу первого элемента ИЛИ-НЕ и через второй элемент НЕ к второму входу второго элемента ИЛИ-НЕ, выходы поля микроопераций блока памяти подключены к вторым входам элементов И первой и второй групп.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Логический анализатор | 1985 |

|

SU1283771A1 |

| Устройство для программного управления | 1989 |

|

SU1656498A1 |

| Микропрограммное устройство управления | 1990 |

|

SU1716512A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

Микропрограммное устройство управления относится к технике контроля и диагностики цифровых устройств и может быть использовано при разработке микропрограммных устройств управления ЭВМ, микропроцессорных устройств. Цель изобретения - расширение функциональных возможностей устройства за счет реализации переменной частоты формирования микрокоманд. Сущность изобретения состоит в том, ;что в известное устройство, содержащее счетчик 1 адреса, дешифратор 2, блок памяти 10, две группы элементов И 7, 8, первый элемент НЕ 9, дополнительно введены счетчик 13, первый и второй мультиплексоры II, 12, регистр 14 частоты, четыре триггера 3- 6, элемент И-НЕ 16, второй элемент НЕ 15, два элемента ИЛИ-НЕ 17, 18. 3 ил. (Л 27 СО СО 4 05 25

Вш,1ПЩ8гера6 --i

СбросI Поле форматб Поле ншанд

fPua. 3

Редактор Е.Копча

Составитель М.Силин Техред И.Попович

Заказ 3963/45

Тираж 672Подписное

ВИНИЛИ Государственного комитета СССР

по делам изобретений и открытий ПЗЮЗЗ, Москва, Ж-35, Раушская наб., д..4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(Рие. 2 Ин1рормационные лодя

flojieK

Корректор А.Зимокосов

| Хассон С | |||

| Микропрограммное управление, вьт | |||

| I | |||

| М.: Мир, 1973, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Микропрограммное устройство управления | 1980 |

|

SU928356A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-30—Публикация

1985-12-23—Подача