Изобретение относится к электросвязи и может использоваться для ци- кловой синхронизации приемников в системах передачи цифровой информации с временным разделением каналоп.

Целью изобретения является уменьшение времени вхождения в синхронизм

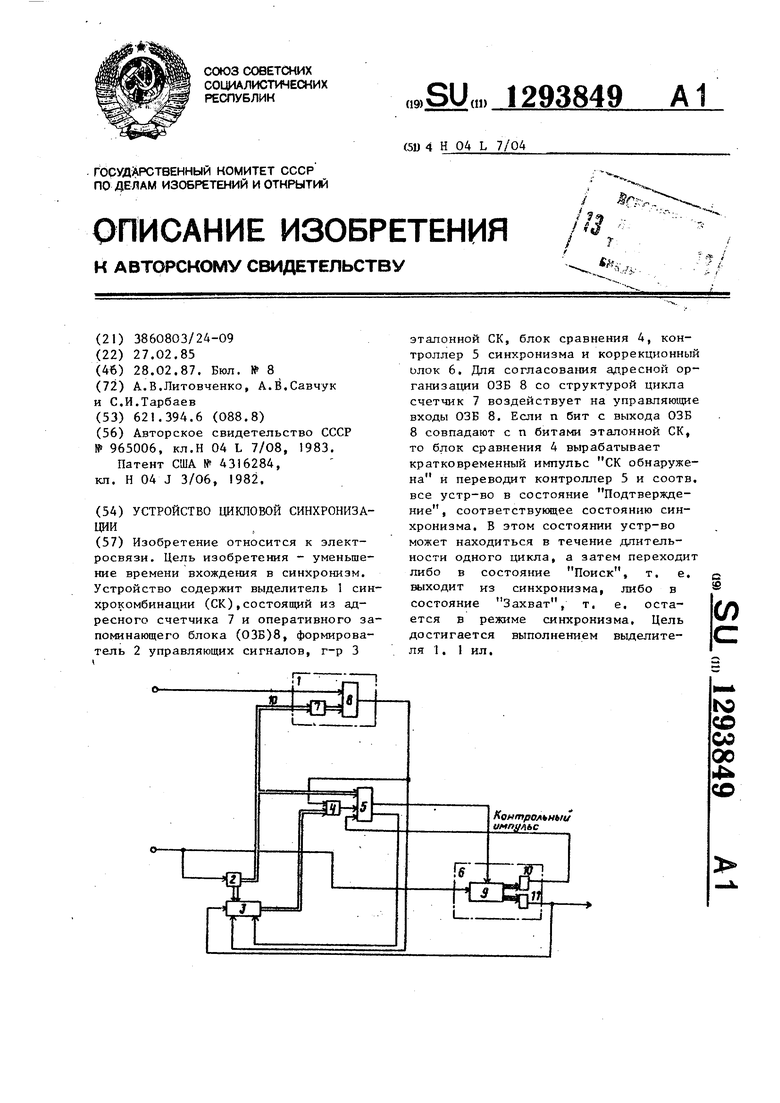

На чертеже представлена структурная электрическая схема устройства цикловой синхронизации.

Устройство цикловой синхронизации содержит выделитель 1 синхрокомбина- ции, формирователь 2 управляющих сигналов, генератор 3 эталонной синхро- комбинации, блок 4 сравнения, конт

ролл ер 5 синхронизма, коррекционный блок 6.

Выделитель 1 синхрокомбинации содержит адресный счетчик 7 и оперативный запоминающий блок 8, Коррекционный блок 6 содержит счетчик 9 импульсов и .первый и второй элементы И 10 и П,

Устройство цикловой синхронизации работает следующим образом,

В каждом цикле принимаемого группового сигнала содержится N бит, из которых п + k битов предназначены для циклового фазирования: п битов отведены для синхрокомбинации (СК), k битов - для идентификатора цикла (ИЦ). Указанные п + k битов равномерно распределены через каждые m - 1 информационных битов в части цикла, состоящей из m(n+k) битов.

Тактовое колебание поступает на тактовый вход формирователя 2, выходные управляющие сигналы которого поступают на соответствующие управляющие входа блока 4 сравнения и адресного счетчика 7, Адресный счетчик 7 воздействует на управляющие входы оперативного запоминающего блока (ОЗБ) 8 так, чтобы согласовать адресную организацию ОЗБ 8 со структурой цикла. Для .этого ячейки памяти ОЗБ 8 образуют матрицу из п + k строк и m столбцов. В режиме записи биты вход ного сигнала последовательно записываются в строки матрицы, а в режиме чтения считываются по столбцам.

На одном тактовом интервале в строку матрицы ОЗБ 8 записывается последний поступивший на информационный вход устройства цикловой синхро- низации бит входного сигнала, после чего ОЗБ 8 переводится в режим чтения и из него с высокой частотой считываются п + k битов, размещенных в

0

0

5

столбце матрицы, в котором содержится и последний поступивщий бит. Если в той части входного сигнгша, которая хранится в ОЗБ 8, содержится п + k

битов СК и ИЦ, то они оказываются размещенными в одном из столбцов матрицы ОЗБ 8, Описанная запись одного входного бита и чтение п + k битов из ОЗБ 8 повторяются на каждом тактовом интервале,

Цри отсутствии синхронизма контроллер 5 и соответственно устройство цикловой синхронизации находятся в состоянии Поиск, При этом считывае5 мые п битов с выхода ОЗБ 8 подаются . на блок 4 сравнения, на который также поступают п битов эталонной СК с эталонных выходов генератора 3,

Если указанные п битов с выхода ОЗБ 8 совпадают с п битами эталонной СК, то блок 4 сравнения вырабатывает кратковременный импульс СК обнару- жена и переводит контроллер 5 и соответственно устройство цикловой синхронизации в состояние Подтверждение, соответствующее режиму синхронизма,

В противном случае устоойство цикловой синхронизации остается в состоянии Поиск,

Сразу после перехода в состояние Подтверждение контроллер 5 вырабатывает два сигнала. Первый из них - кратковременный импульс, поступающий с выхода контроллера 5 на вход Сброс счетчика 9 коррекционного блока 6. Б режиме синхронизма нулевое состояние счетчика 9 совпадает по времени с импульсом СК обнаруже- на, т , е, с моментом обнаружения СК, Вт9РОЙ сигнал появляется на дополнительном выходе; контроллера 5 и представляет собой низкий логический уровень, который сохраняется до по5 тери синхронизма. Этот сигнал поступает с дополнительного выхода контроллера 5 на запоминающий вход генератора 3, Он обеспечивает запоминание k битов ИЦ, поступающих с выхо - да ОЗБ 8 вслед за обнаруженными п битами СК, Указанные биты ИЦ загшсыва- ются в генераторе 3 под воздействием синхросигнала, поступающего от формирователя 2,

Значение этих битов ИЦ изменяется от цикла к циклу при поступлении на вход сигнала Отметка цикла генератора сигнала с выхода Отметка цикла коррекционного блока 6, Указанное из5

0

0

менение ИЦ разрешается только в режиме синхронизма низким уровнем сигнала, поступающим с дополнительного выхода контролера 5 на запоминающий вход генератора 3,

Интервал времени, в течение которого контроллер 5 (и соответственно устройство цикловой синхронизации) может находиться в состоянии Подтверждение, не превышает длительное ти одного цикла, а затем переходит либо в состояние Поиск (выходит из синхронизма), либо в состояние Захват (остается в режиме синхронизма)

Критерием потери синхронизма в состоянии Подтверждение является ошибочный прием первой после восстановления синхронизма СК,включая ИЦ.

Модуль счета счетчика 9 равен N, Поэтому под действием тактового коле бания, поступающего на его тактовый вход, через N тактовых интервалов после первого обнаружения СК счетчик 9 оказывается в нулевом состоянии. Первый элемент И 10, подключенный к соответствующим разрядам счетчика 9, вырабатывает кратковременный контролный импульс. Этот импульс поступает на дополнительный управляющий вход контроллера 5 в тот момент времени, когда на первом его входе, подключенном к выходу блока 4 сравнения, должен появиться очередной импульс СК

обнаружена. Если в состоянии Подтверждение указанные импульсы не появляются одновременно в ожидаемый момент обнаружения СК, то устройство цикловой синхронизации считается вышедшим из синхронизма и возвращается в состояние Поиск. Если же точно через N тактовых интервалов после первого обнаружения СК контрольный импульс (выходной сигнал блока 4 сравнения) и импульс СК обнаружена поступают на контроллер 5 одновремен но, то контролер 5 (и соответственно устройство цикловой синхронизации) из состояния Подтверждение переходит в состояние Захват, В этом состоянии контроллер 5 начинает подсче числа несовпадений во времени контрольного импульса и импульса СК обнаружена. Из состояния Захват, контролер 5 выходит из синхронизма только в том случае, если указанные импульсы не появляются одновременно не менее трех раз подряд в моменты ожидаемого обнаружения СК, Только в

,

12938494

случае трех последовательных несовпадений сигнал на дополнительном выходе контроллера 5 принимает значение высокого логического уровня, что свидетельствует о переходе в состояние Поиск, т,е, о выходе из режима синхронизма.

Формула изобретения

-fO

35

-20 . 30

40

45

f5

Устройство цикловой синхронизации, сор,ерж.аЛ.ее последовательно соединенные генератор эталонной синхрокомби- нации , блок сравнения, контроллер синхронизма и коррекционный блок, также выделитель синхрокомбинации и формирователь управляющих сигналов, управляю цие выходы которого подсоединены к соответствукщим управляющим входам контроллера синхронизма, а вход сигнала Отметка цикла генератора эталонной синхрокомбинации подключен к выходу сигнала Отметка

jr цикла коррекционного блока, причем информационный вход выделителя синг хрокомбинации и объединенные тактовые входы формирователя управляющих сигналов и коррекционного блока являются соответственно информационным и тактовым входами устройства, о т л и- чающееся тем, что, с целью уменьшения времени вхождения в синхронизм, управляющие входы выделителя синхрокомбинации подключены к соответствующим управляющим выходам формирователя управляющих сигналов, выход выделителя синхрокомбинации подсоединен к другому входу блока сравнения и входу сигнала Идентификатор цикла генератора эталонной синхрокомбинации, запоминающий, тактовый и установочный входы которого подключены соответственно к дополнительному выходу контроллера синхронизма, тактовому и дополнительному управляющему выходам формирователя .. управляющих сигналов, а контрольный выход коррекционного блока подсоединен к дополнительному управляихцему входу контроллера синхронизма, причем выход сигнала Отметка цикла коррекционного блока является выходом устройства, а выделитель сиккрокок- бинации содержит последовательно сое55 диненные адресный счетчик и оперативный запоминающий блок, информационный вход и выход которого являются соответственно информационным вхо512938496

дом и выходом вьщелителя синхрокомби- счетчика являются улравляюсцими вхо- нации, а управляющие входы адресногодами выделителя синхрокомбинации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2190304C2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ | 2005 |

|

RU2302084C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2187210C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2000 |

|

RU2180157C2 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2237374C1 |

| Устройство коммутации дискретных каналов с временным разделением | 1989 |

|

SU1663785A1 |

| Устройство синхронизации станции коммутации каналов | 1987 |

|

SU1536518A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2256295C1 |

| УСТРОЙСТВО ДЛЯ ГРУППОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2003 |

|

RU2248677C1 |

| СПОСОБ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2010437C1 |

Изобретение относится к электросвязи. Цель изобретения - уменьшение времени вхождения в синхронизм. Устройство содержит выделитель 1 син- хрокомбинации (СК),состоящий из адресного счетчика 7 и оперативного запоминающего блока (ОЗБ)8, форьшрова- тель 2 управляющих сигналов, г-р 3 эталонной СК, блок сравнения 4, контроллер 5 синхронизма и коррекционный ьлок 6. Для согласования адресной организации ОЗБ 8 со структурой цикла счетчик 7 воздействует на управляюище входы ОЗБ 8. Если п бит с выхода ОЗБ 8 совпадают с п битами эталонной СК, то блок сравнения 4 вырабатывает кратковременный импульс СК обнаружена и переводит контроллер 5 и соотв. все устр-во в состояние Подтверждение, соответствующее состоянию синхронизма, В этом состоянии устр-во может находиться в течение длительности одного цикла, а затем переходит либо в состояние Поиск, т. е. выходит из синхронизма, либо в состояние Захват, т. е, остается в режиме синхронизма. Цель достигается выполнением вьщелите- ля 1, 1 ил, с Ев (Л 1C со со 00 N со

| Устройство циклового фазирования аппаратуры передачи двоичных сигналов | 1981 |

|

SU965006A1 |

| Патент США № 4316284, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-02-28—Публикация

1985-02-27—Подача